Изобретение относится к вычисли- тельной технике и может быть использовано при реализации технических средств вычислительной техники и дне- кретной автоматики.

Целью изобретения является повышение быстродействия и сокращение оборудования .

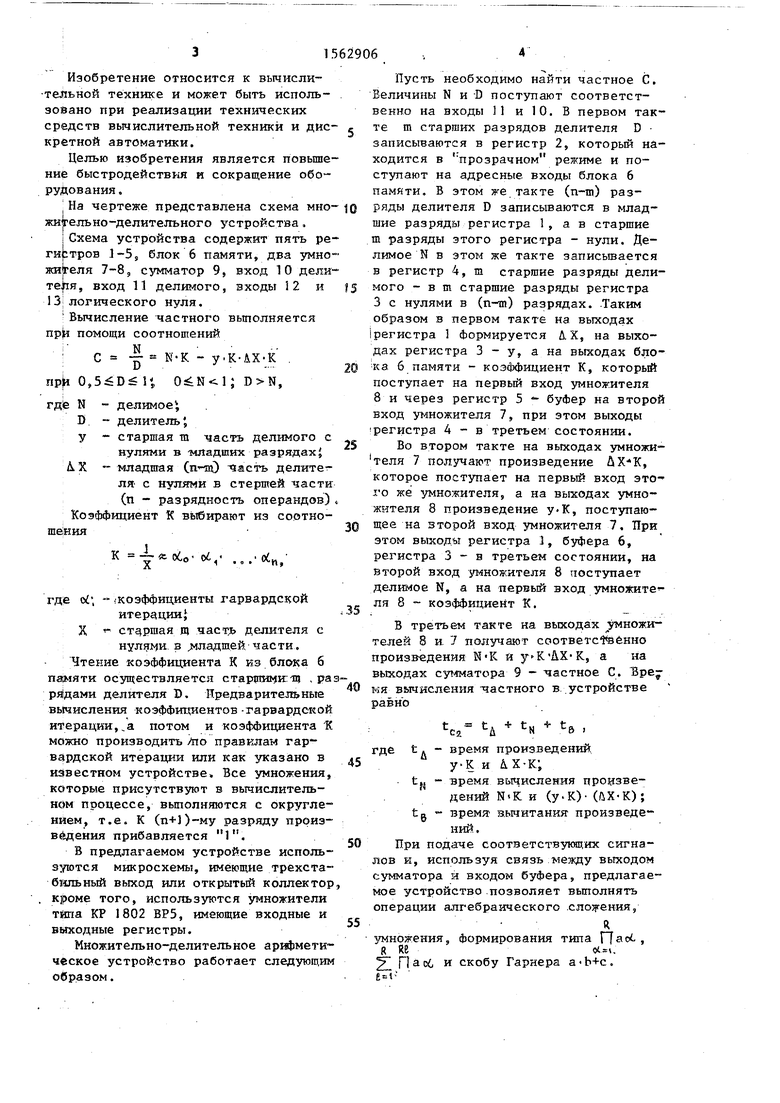

На чертеже представлена схема MHOжительно-делителъного устройства,

Схема устройства содержит пять ре- гиЬтров 1-5S блок 6 памяти, два умножителя 7-8, сумматор 9, вход 10 дели™ , вход 11 делимого, входы 12 и 13 логического нуля.

Вычисление частного выполняется при помощи соотношений

c-i-,.rри 0, 1

де N D У

У К-АХ-К .il; ,

&Х

делимое делитель ,

старшая m часть делимого с нулями в -младших раз рядах Ј младшая (гмд) -засть делителя с нулями в стершей части: (п - разрядность операндов). Коэффициент К выбирают из соотноения

I

2S

К

х. Ote. Oi

of.

и

где оЈ , -коэффициенты гарвардской

итерации

X старшая щ часть делителя с нулями в .младшей части.

Чтение коэффициента К из блока б памяти осуществляется старшими: , раз ря(дами делителя Т). Предварительные вычисления коэффициентов-гарвардской итерации,а потом и коэффициента К можно производить /по правилам гар вардской итерации или как указано в известном устройстве. Все умножения, которые присутствуют в вычислительном процессе, выполняются с округлением, т.е. К (п-Н)-му разряду проиэ- вйдения прибавляется 1.

В предлагаемом устройстве используются микросхемы, имеющие трехста- бштьный выход или открытый коллектор кроме того, используются умножители типа КР 1802 ВР5, имеющие входные и выходные регистры.

Множительно-делителыгое арифметическое устройство работает следующим образом.

$

5

0

5

Пусть необходимо найти частное С. Величины N и D поступают соответственно на входы 11 и 10. В первом такте m старших разрядов делителя D записываются в регистр 2, который находится в прозрачном режиме и поступают на адресные входы блока 6 памяти. В этом же такте (n-m) разряды делителя D записываются в младшие разряды регистра 1, а в старшие m разряды этого регистра - нули. Делимое N в этом же такте записывается в регистр 4, in старшие разряды делимого - в m старшие разряды регистра 3 с нулями в (n-m) разрядах. Таким образом в первом такте на выходах (регистра 3 Формируется U. X, на выходах регистра 3 - у, а на выходах блока б памяти - коэффициент К, который поступает на первый вход умножителя 8 и через регистр 5 - буфер на второй вход умножителя 7, при этом выходы регистра 4 - в третьем состоянии.

Во втором такте на выходах умножи- теля 7 получают произведение йХлК, которое поступает на первый вход этого же умножителя, а на выходах умножителя 8 произведение у-К, поступающее на второй вход умножителя 7. При этом выходы регистра 1, буфера 6, регистра 3 - в третьем состоянии, на второй вход умножителя 8 поступает делимое N, а на первый вход умножителя 8 - коэффициент К.

В третьем такте на выходах умножи- телей 8 и 7 получают соответственно произведения N K и у К АХ-К, а на выходах сумматора 9 - частное С. Бремя вычисления частного в устройстве равно

сеа- Ч СН + где t, - время произведений

у К и &Х-К;

tfi - время вычисления произведений N«K и (у-К)- (UX-K); tg - время1 вычитания произведений.

При подаче соответствующих сигналов vi, используя связь между выходом сумматора и входом буфера, предлагаемое устройство позволяет выполнять операции алгебраического сложения,

R

умножения, формирования типа ГТао. , R ,

П а с(, и скобу Гарнера а-Ь+с.

Формула изобретения

Множительно-делительное арифметическое устройство, содержащее пять ргистров, два умножителя, блок памяти и сумматор, причем выход первого регистра соединен с входом первого сомножителя первого умножителя, выход которого соединен с первым информационным {Входом сумматора, вход старших разрядов делителя устройства соединен с информационным входом второго регистра, выход которого соединен с адресным входом блока памяти, выход которого соединен с входом первого сомножителя второго умножителя, вход старших разрядов делимого устройства соединен с информационным входом третьего регистра, отличающееся тем, что, с целью повышения быстродействия и сокращения оборудования, вход n-m разрядов делителя первого регистра соединен с информационным входом n-m разрядов первого регистра, вход ш разрядов которого соединен с входом логического нуля устройства и с входом n-m разрядов третьего регистра, выход которого соединён с входом второго сомножителя второго умножителя и с выходом четg вертого регистра, информационный вход которого осединен с входом m старших разрядов делимого устройства, выход сумматора соединен с информационным входом пятого регистра и входом пер5 вого сомножителя второго умножителя, выход которого соединен с выходом пятого регистра, вторым,информационным входом сумматора и входом второго сомножителя первого умножителя выход

0 которого соединен с входом первого сомножителя первого умножителя выход сумматора является выходом результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1988 |

|

SU1517026A1 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

Изобретение относится к вычислительной технике, в частности к устройствам деления, и может быть использовано при реализации технических средств вычислительной техники и дискретной автоматики. Целью изобретения является повышение быстродействия и сокращение оборудования. Поставленная цель достигается тем, что, устройство, содержащее пять регистров 1 - 5, два умножителя 7 - 8, блок 6 памяти и сумматор 9, причем M старших выходных разрядов второго регистра подключены к адресным входам блока памяти. Отличительным в работе устройства является состав и характер связей между элементами устройства, а также применение другой организации вычислительного процесса. 1 ил.

| Устройство для умножения-деления | 1985 |

|

SU1249509A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Множительно-делительное арифметическое устройство | 1986 |

|

SU1381491A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-07—Публикация

1988-10-04—Подача