(Л

со

00

о

4

00

к

}

1

Изобретение относится к вычислительной технике, а именно к области запоминающих устройств, и является усовершенствованием устройства по авт. св. № 1195391.

Целью изобретения является повышение надежности устройства.

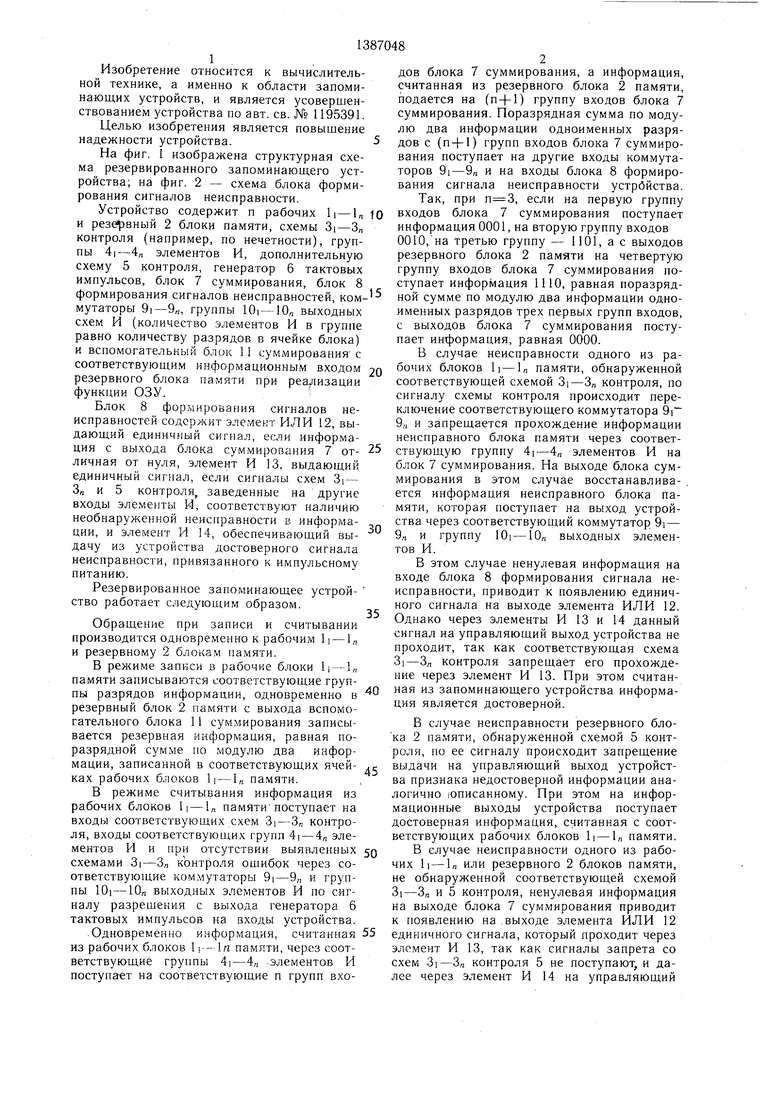

На фиг. 1 изображена структурная схема резервированного запоминаюш,его устройства; на фиг. 2 - схема блока формирования сигналов неисправности.

дов блока 7 суммирования, а информация, считанная из резервного блока 2 памяти, подается на (n-f-l) группу входов блока 7 суммирования. Поразрядная сумма по модулю два информации одноименных разрядов с (п + 1) групп входов блока 7 суммирования поступает на другие входы коммутаторов 9i-9„ и на входы блока 8 формирования сигнала неисправности устройства. Так, при , если на первую группу

Устройство содержит п рабочих Ь -1„ ю входов блока 7 суммирования поступает

и резервный 2 блоки памяти, схемы 3i-3л контроля (например, по нечетности), группы 4|-4л элементов И, дополнительную схему 5 контроля, генератор 6 тактовых импульсов, блок 7 суммирования, блок 8

информация 0001, на вторую группу входов 0010, на третью группу - 1101, а с выходов резервного блока 2 памяти на четвертую группу входов блока 7 суммирования поступает информация 1110, равная поразрядименных разрядов трех первых групп входов, с выходов блока 7 суммирования поступает информация, равная 0000.

В случае неисправности одного из раформирования сигналов неи справностей, ком- ной сумме по модулю два информации одномутаторы 9i-9«, группы 10: -10„ выходных

схем И (количество элементов И в группе

равно количеству разрядов в ячейке блока)

и вспомогательный блок 11 суммирования с

соответствующим информационным входом 20 бочих блоков 1| -1„ памяти, обнаруженной

резервного блока памяти при реализациисоответствующей схемой 3i-3„ контроля, по

функции ОЗУ.

Блок 8 формирования сигналов неисправностей содержит элемент ИЛИ 12, выдающий единичный сигнал, если информасигналу схемы контроля происходит переключение соответствующего коммутатора 9i 9.,, и запрещается прохождение информации неисправного блока памяти через соответция с выхода блока суммирования 7 от- 25 ствующую группу 4i-4„ элементов И на

личная от нуля, элемент И 13, выдающий единичный сигнал, если сигналы схем 3i - Зге и 5 контроля, заведенные на другие входы элементы И, соответствуют наличию необнаруженной неисправности в информа- , ции, и элемент И 14, обеспечивающий вы- дачу из устройства достоверного сигнала неисправности, привязанного к импульсному питанию.

Резервированное запоминающее устройство работает следующим образом.

Обращение при записи и считывании производится одновременно к рабочим li - 1л и резервному 2 блокам памяти.

В режиме записи в рабочие блоки li -1„ памяти записываются соответствующие групблок 7 суммирования. На выходе блока суммирования Б этом случае восстанавливается информация неисправного блока памяти, которая поступает на выход устройства через соответствующий коммутатор 9i - 9„ и группу lOi-Юл выходных элементов И.

В этом случае ненулевая информация на входе блока 8 формирования сигнала неисправности, приводит к появлению единичного сигнала на выходе элемента ИЛИ 12. Однако через элементы И 13 и 14 данный сигнал на управляющий выход устройства не проходит, так как соответствующая схема контроля запрещает его прохождение через элемент И 13. При этом считанпы разрядов информации, одновременно в запоминающего устройства информарезервный блок 2 памяти с выхода вспомо- является достоверной, гательного блока 1i суммирования записы-В случае неисправности резервного бловается резервная информация, равная по- ка 2 памяти, обнаруженной схемой 5 контразрядной сумме по модулю два инфор-роля, по ее сигналу происходит запрещение

мации, записанной в соответствующих ячей- дгвыдачи на управляющий выход устройст,. . , 11 .Э „ „„.„ .,.,,,,,.,,,-.

ках рабочих блоков li - „ памяти.

В режиме считывания информация из рабочих блоков li - 1л памяти поступает на входы соответствующих схем 3i-3„ контроля, входы соответствующих групп 4| - 4п элементов И и при отсутствии выявленных 50 схемами 3i-3л контроля ощибок через соответствующие комлчутаторы 9i-9„ и группы lOi -10п выходных элементов И по сигналу разрещения с выхода генератора 6 тактовых импульсов на входы устройства.

ва признака недостоверной информации аналогично (Описанному. При этом на информационные выходы устройства поступает достоверная информация, считанная с соответствующих рабочих блоков - 1л памяти. В случае неисправности одного из рабочих или резервного 2 блоков памяти, не обнаруженной соответствующей схемой 3i-3„ и 5 контроля, ненулевая информация на выходе блока 7 суммирования приводит к появлению на .выходе элемента ИЛИ 12

Одновременно информация, считанная 55 единичного сигнала, который проходит через

из рабочих блоков памяти, через соответствующие группы 4|-4л -Элементов И поступает на соответствующие п групп вхоэлемент И 13, так как сигналы запрета со схем контроля 5 не поступают, и далее через элемент И 14 на управляющий

дов блока 7 суммирования, а информация, считанная из резервного блока 2 памяти, подается на (n-f-l) группу входов блока 7 суммирования. Поразрядная сумма по модулю два информации одноименных разрядов с (п + 1) групп входов блока 7 суммирования поступает на другие входы коммутаторов 9i-9„ и на входы блока 8 формирования сигнала неисправности устройства. Так, при , если на первую группу

входов блока 7 суммирования поступает

входов блока 7 суммирования поступает

информация 0001, на вторую группу входов 0010, на третью группу - 1101, а с выходов резервного блока 2 памяти на четвертую группу входов блока 7 суммирования поступает информация 1110, равная поразрядной сумме по модулю два информации одноименных разрядов трех первых групп входов, с выходов блока 7 суммирования поступает информация, равная 0000.

В случае неисправности одного из расигналу схемы контроля происходит переключение соответствующего коммутатора 9i 9.,, и запрещается прохождение информации неисправного блока памяти через соответствующую группу 4i-4„ элементов И на

ствующую группу 4i-4„ элементов И на

блок 7 суммирования. На выходе блока суммирования Б этом случае восстанавливается информация неисправного блока памяти, которая поступает на выход устройства через соответствующий коммутатор 9i - 9„ и группу lOi-Юл выходных элементов И.

В этом случае ненулевая информация на входе блока 8 формирования сигнала неисправности, приводит к появлению единичного сигнала на выходе элемента ИЛИ 12. Однако через элементы И 13 и 14 данный сигнал на управляющий выход устройства не проходит, так как соответствующая схема контроля запрещает его прохождение через элемент И 13. При этом считан « запоминающего устройства информавыдачи на управляющий выход устройст „ „„.„ .,.,,,,,.,,,-.

ва признака недостоверной информации аналогично (Описанному. При этом на информационные выходы устройства поступает достоверная информация, считанная с соответствующих рабочих блоков - 1л памяти. В случае неисправности одного из рабочих или резервного 2 блоков памяти, не обнаруженной соответствующей схемой 3i-3„ и 5 контроля, ненулевая информация на выходе блока 7 суммирования приводит к появлению на .выходе элемента ИЛИ 12

единичного сигнала, который проходит через

элемент И 13, так как сигналы запрета со схем контроля 5 не поступают, и далее через элемент И 14 на управляющий

выход устройства. Считанная из запоминающего устройства информация считается в этом случае недостоверной.

Таким образом, повышение надежности устройства обеспечивается за счет исключения бракования информации на его выходах при отказе резервного блока памяти, обнаруженного вновь введенной схемой контроля.

Формула изобретения

1. Резервированное запоминающее устройство по авт. св. № 1195391, отличающееся тем, что, с целью повыщения надежности устройства, оно содержит допол- нительную схему контроля, входы которой подключены к выходам резервного блока

памяти, выходы схем контроля и выход дополнительной схемы контроля подключены к второй группе входов блока формирования сигналов неисправностей.

2. Устройство по п. 1, отличающееся тем, что блок формирования сигналов неисправностей содержит первый и второй элементы И и элемент ИЛИ, входы которого являются входами первой группы блойа формирования сигналов неисправностей, выход элемента ИЛИ подключен к входу первого элемента И, выход которого подключен к первому входу второго элемента И, второй вход и входы группы первого элемента И являются входами второй группы блока формирования сигналов неисправностей, выход второго элемента И является выходом блока формирования сигналов неисправностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1982 |

|

SU1195391A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1076953A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1129658A1 |

| Резервированное запоминающее устройство | 1979 |

|

SU881875A2 |

| Резервированное запоминающее устройство | 1981 |

|

SU983752A1 |

| Резервированное запоминающее устройство | 1984 |

|

SU1239751A2 |

| Резервированное запоминающее устройство | 1980 |

|

SU936034A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1510012A1 |

Изобретение относится к вычислительной технике, а именно к области запоминающих устройств. Целью изобретения является повышение надежности устройства. Устройство содержит п рабочих - „ и резервный 2 блоки памяти, схемы контроля 3|-3л, группы 4i-4п элементов И, дополнительную схему 5 контроля, генератор 6 тактовых импульсов, блок- 7 суммирования, блок 8 формирования сигналов неисправностей, коммутаторы 9i-9л, группы lOi - 10л выходных элементов И, блок 11 суммирования. Изобретение обеспечивает повышение надежности устройства за счет исключения бракования информации на его выходах при отказе резервного блока памяти, обнаруженного введенной схемой контроля. 1 з.п. ф-лы, 2 ил.

ff/77Jr0/77 Jn ff/777ffffjS

| Резервированное запоминающее устройство | 1982 |

|

SU1195391A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-20—Подача