Изобретение относится к вычислительной технике и цифровым системам управления и может быть применено, в частности, для повторения серии управляющих сигналов путем их задержки на заданный интервал времени, задаваемый с высокой точностью и в широком диапазоне.

Цель изобретения - упрощение устройства при задержке пачек импульсов с высокой точностью в широком диапазоне задержек.

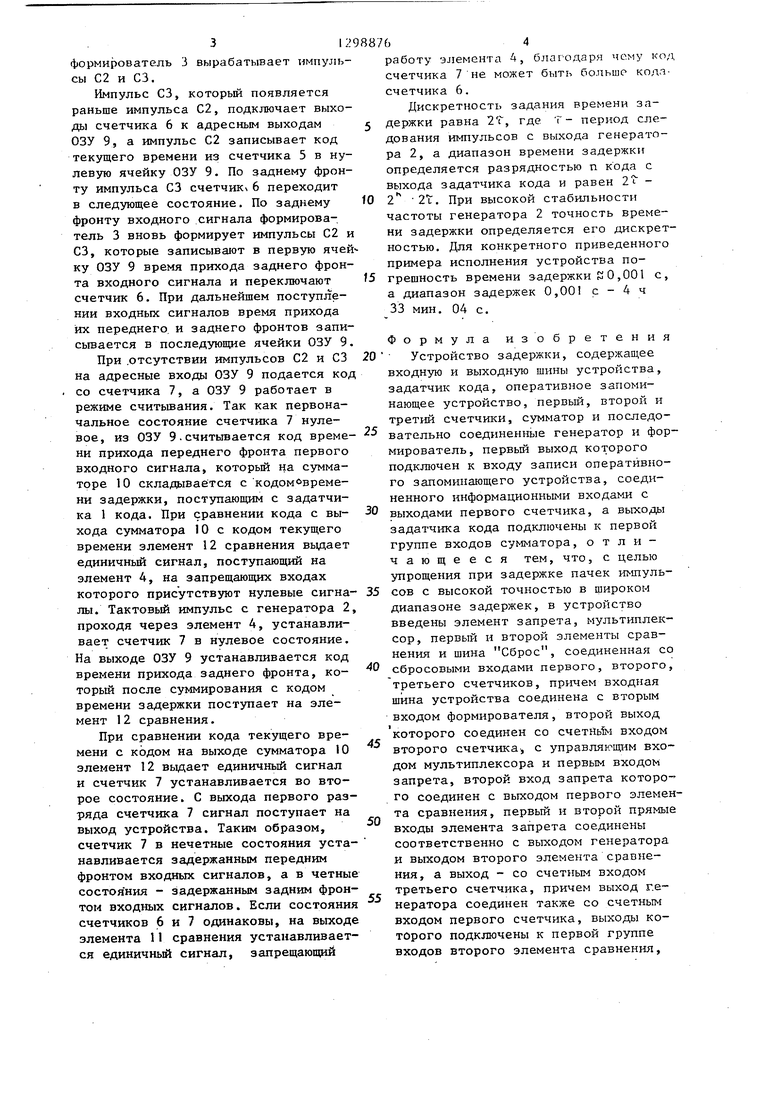

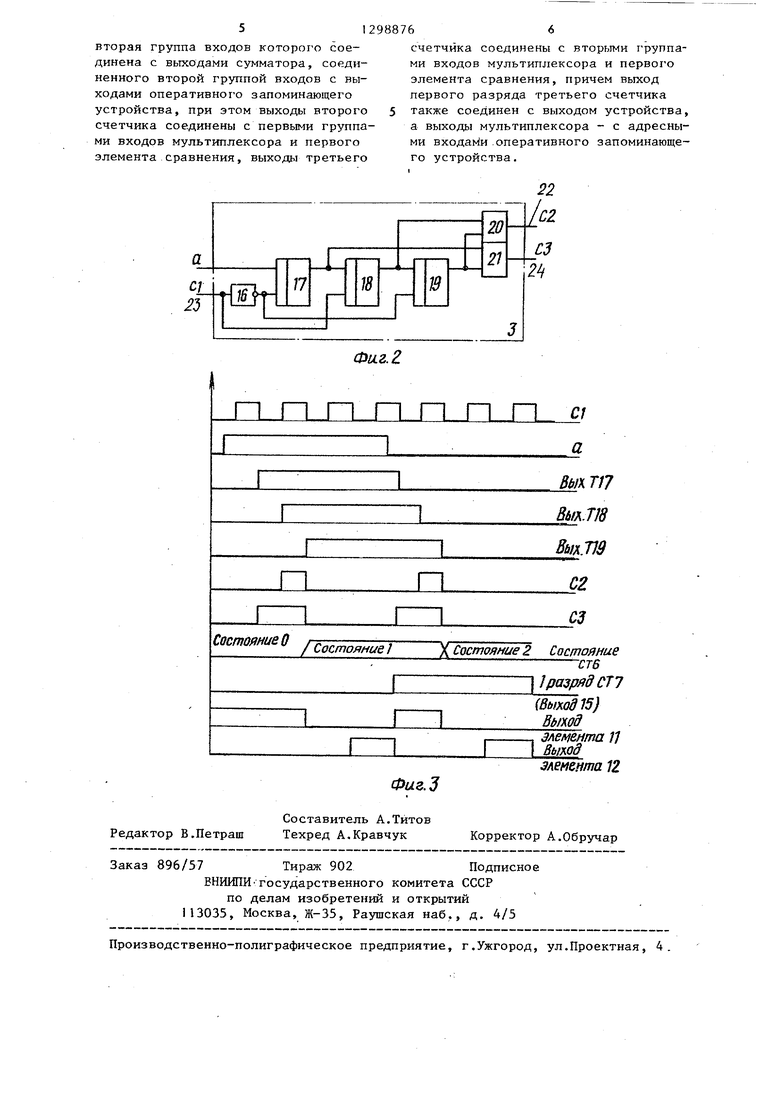

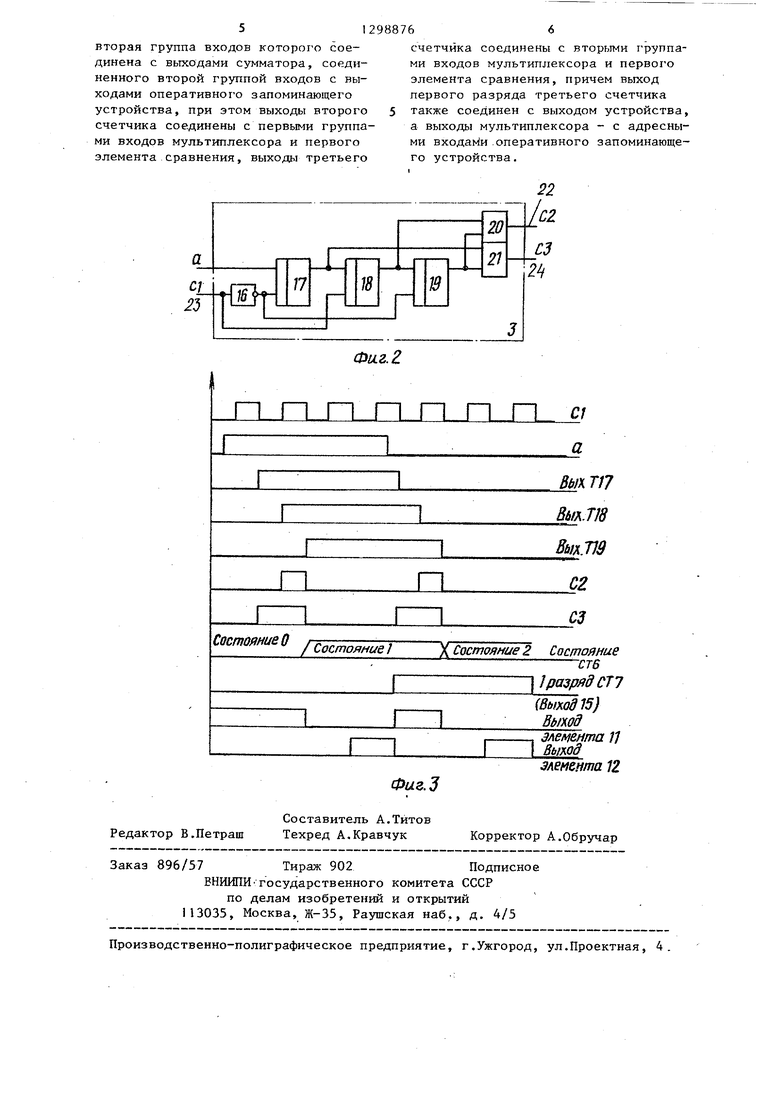

На фиг.1 представлена функциональная схема устройства задержки; на фиг.2 - схема формирователя; на фиг.3 - временные диаграммы работы устройства задержки.

Устройство задержки содержит за- датчик 1 кода, генератор 2, формирователь 3, элемент 4 запрета, счетчики 5 - 7, мультиплексор 8, оперативное запоминающее устройство (ОЗУ) 9, сумматор 10, элементы 11 и 12 сравнения, входную шину 13 устройства, шину 14 Сброс и выходную шину 15 устройства.

Входная шина 13 соединена с входом формирователя 3, второй вход которого подключен к выходу генератора 2, к счетному входу счетчика 5 и к перовому прямому входу элемента 4 запрета. Первьй выход формирователя 3 соединен с входом записи ОЗУ .9, а второй - со счетным входом счетчик 6, с управляющим входом мультиплексора 8 и с первым входом запрета элемента 4. Шина 14 Сброс устройства соединена со сбросовыми входами счетчиков 5 - 7. Выходы задатчика 1 кода соединены с первсж группой входов- сумматора 10, выходы счетчика 5 - с первфй группой входов элемента 12 сравнения и через ОЗУ 9 с второй группой входов сумматора 10, соединенного выходами с второй группой входов элемента i 2 сравнения, соединенного вь1хсдом с вторым прямым входом элемента 4. Выходы счетчика 6 соединены с первыми группами входов мультиплексора 8 и элемента 11 сравнения, а выходы счетчика 7 - с вторыми группами входов мультиплексора 8 и элемента 11 сравнения. Выход первого разряда счетчика 7 соединен с выходом устройства, а выход элемента 11 сравнения - с вторым входом запрета элемента 4, соединенного выходом со .счетным входом счетчика 7.

2988762

В1лходы мультиплексора 8 соединены с адресными входами ОЗУ 9.

содержит, I6, D-триггеры

O

5

0

5

0

5

0

5

0

5

Формирователь 3 (фиг.2) например, элемент НЕ 17 - 19 и элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 20 и 21. При подаче на вход а формирователя импульсного сигнала на выходе 22 формируются два импульсных, сигнала по фронту и по срезу входного сигнала длительностью, равной длительности импульса на входе 23 (CI), а на выходе 24(03) - два импульсных сигнала длительностью, равной периоду следования импульсов на входе 23. Триггеры 17 - 19 обеспечивают задержку фронта и среза входного сигнала, а элементы 20 и 21 формируют сигналы, когда состояния триггеров 18 и 19 и соответственно триггеров 17 и 19 не равны.

На временной диаграмме (фиг.З) поясняется процесс формирования импульсов на выходах 22 и 24. Задатчик 1 кода выдает двоичный код времени задержки, который может устанавливаться, например, переключателями. Генератор 2 формирует тактовые импульсы с высокой стабильностью частоты f. Счетчики 5-7 срабатывают по заднему фрокту счетного импульса. Мультиплексор 8 при единичном сигнале Р пропускает код с первой группы входов, а при нулевом сигнале Р - с второй группы входов. ОЗУ 9 при единичном сигнале на входе V осуществляет запись информации В,...В2ч по ад- ресу А...А,а при нулевом - считывание., Конкретные параметры приведенного устройства следующие: f- 2 Гц, счетчик 5 имеет 25 разрядов. Код на выходе задатчика I 24- разрядньй; сумматор 10 и элемеАт 12 сравнения 24-разрядные; счетчики 6 и 7 имеют по 4 разряда.

Устройство работает следзоощим образом.

После включения устройства на шину 14 необходимо подать сигнал Сброс, устанавливающий счетчики 5 - 7 в нулевые состояния. Тактовые импульсы с генератора 2 поступают на счетчик 5, на выходе которого формируется изменяющийся во времени двоичный код текущего времени. На адресных входах ОЗУ 9 поддерживается нулевой код, так как состояние- счетчиков 6 и 7 нулевое. При поступлении переднего фронта входного сигнала

формирователь 3 вырабатывает нмиуль- сы С2 и СЗ.

Импульс СЗ, которьй появляется раньше импульса С2, подключает выходы счетчика 6 к адресным выходам ОЗУ 9, а импульс С2 записывает код текущего времени из счетчика 5 в нулевую ячейку ОЗУ 9. По заднему фронту импульса СЗ счетчикч 6 переходит в следующее состояние. По заднему фронту входного сигнала формирователь 3 вновь формирует импульсы С2 и СЗ, которые записывают в первую ячейку ОЗУ 9 время прихода заднего фронта входного сигнала и переключают счетчик 6. При дальнейшем поступлении входных сигналов время прихода их переднего, и заднего фронтов записывается в последующие ячейки ОЗУ 9

При .отсутствии импульсов С2 и СЗ на адресные входы ОЗУ 9 подается код со счетчика 7, а ОЗУ 9 работает в режиме считьшания. Так как первоначальное состояние счетчика 7 нулевое, из ОЗУ 9.считывается код времени прихода переднего фронта первого входного сигнала, который на сумматоре 10 складывается с кодом време- ни задержки, поступающим с задатчи- ка 1 кода. При сравнении кода с выхода сумматора 10 с кодом текущего времени злемент 12 сравнения выдает единичньш сигнал, поступающий на элемент 4, на запрещающих входах которого присутствуют нулевые сигналы. Тактовый импульс с генератора 2, проходя через элемент 4, устанавливает счетчик 7 в нулевое состояние. На выходе ОЗУ 9 устанавливается код времени прихода заднего фронта, который после суммирования с кодом времени задержки поступает на элемент 12 сравнения.

При сравнении кода текущего времени с кодом на выходе сумматора Ш элемент 12 вьщает единичный сигнал и счетчик 7 устанавливается во второе состояние. С выхода первого разряда счетчика 7 сигнал поступает на выход устройства. Таким образом, счетчик 7 в нечетные состояния устанавливается задержанным передним фронтом входных сигналов, а в четные состоя ния - задержанным задним фронтом входных сигналов. Если состояния счетчиков 6 и 7 одинаковы, на выходе элемента 11 сравнения устанавливается единичный сигнал, запрещающий

0

5

0

5

0

5

0

5

0

5

работу элемента А, благодаря чему код счетчика 7 не может быть больше кодл- счетчика 6.

Дискретность задания времени задержки равна 2, где Т- период следования импульсов с выхода генератора 2, а диапазон времени задержки определяется разрядностью п кода с выхода задатчика кода и равен Z l - 2 2t. При высокой стабильности частоты генератора 2 точность времени задержки определяется его дискретностью. Для конкретного приведенного примера исполнения устройства погрешность времени задержки Р 0,001 с, а диапазон задержек 0,001 с - 4 ч 33 мин. 04 с.

Формула изобретения

Устройство задержки, содержащее входную и выходную шины устройства, задатчик кода, оперативное запоминающее устройство, первьш, второй и третий счетчики, сумматор и последовательно соединенные генератор и формирователь, первый выход которого подключен к входу записи оперативного запоминающего устройства, соединенного информационными входами с выходами первого счетчика, а выходы задатчика кода подключены к первой группе входов сумматора, отличающееся тем, что, с целью упрощения при задержке пачек и туль- сов с высокой точностью в широком диапазоне задержек, в устройство введены элемент запрета, мультиплексор, первый и второй элементы сравнения и шина Сброс, соединенная со сбросовыми входами первого, второго, третьего счетчиков, причем входная шина устройства соединена с вторым входом формирователя, второй выход которого соединен со счетНь1м входом второго счетчика, с управляющим входом мультиплексора и первым входом запрета, второй вход запрета которо- го соединен с выходом первого элемента сравнения, первый н второй прямые входы элемента запрета соединены соответственно с выходом генератора и выходом второго элемента сравнения, а выход - со счетным входом третьего счетчика, причем выход генератора соединен также со счетным входом первого счетчика, выходы которого подключены к первой группе входов второго элемента сравнения.

вторая группа входов которого соединена с выходами сумматора, соединенного второй группой входов с выходами оперативного запоминающего устройства, при этом выходы второго счетчика соединены с первыми группами входов мультиплексора и первого элемента сравнения, выходы третьего

счетчика соединены с вторыми группами входов мультиплексора и первого элемента сравнения, причем выход первого разряда третьего счетчика также соединен с выходом устройства, а выходы мультиплексора - с адресными входа1 и .оперативного запоминающего устройства,

гпгпгг Г1 п г1

Г

Состояние о

/ Состояние 1

Редактор В.Петраш

Составитель А.Титов Техред А.Кравчук

Заказ 896/57 Тираж 902Подписное

ЕНИИПИ государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фи.г.г

С1

Вык Т17

Вш.Лд

8шЛ9

П.

С2

.1 I

сз

X Состояние 2 Састояние

СТ6

1 разряд СЛ

(Выход 15) Вымд

элемента П

злемента 12

Фиг.З

Корректор А.Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММНОЕ ВРЕМЕННОЕ УСТРОЙСТВО | 1994 |

|

RU2097820C1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2004 |

|

RU2269866C2 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

Изобретение относится к вычислительной технике и цифровым системам : управления. Цель изобретения - упрощение устройства при задержке пачек импульсов с высокой точностью в широком диапазоне задержек. Устройство задержек содержьг задатчик I кода, генератор 2, формирователь 3, счетчики 5-7, оперативное запоминающее устройство 9, сумматор 10 и входную 13 и выходную 15 шины.. В устройство введены злемент 4 запрета, мультиплексор 8, элементы 1I и 12 сравнения и шина 14 Сброс. Для конкретно приведенного примера исполнения устройства погрешность времени задержки равна ,001 с, а диапазон задержек 0,001 - 4 ч 33 мин 04 с. 3 ил. i (Л Фиг.1

| Цифровая линия задержки | 1983 |

|

SU1109895A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство задержки | 1982 |

|

SU1144188A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1985-11-11—Подача