со эо эо

00

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации блоков памяти | 1986 |

|

SU1394217A1 |

| Устройство для адресации памяти | 1985 |

|

SU1298755A1 |

| Устройство для адресации блоков памяти | 1988 |

|

SU1580375A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1388875A2 |

| Многопрограммный регулятор температуры | 1983 |

|

SU1087951A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для обработки данных | 1979 |

|

SU849222A1 |

| Устройство для адресации памяти | 1986 |

|

SU1355977A2 |

| Устройство адресации | 1989 |

|

SU1619281A1 |

Изобретение относится к области вычислительной техники и является усовершенствованием устройства по авт.св. № 1298755. Целью изобретения является расширение функциональных возможностей за счет реализации дистанционного управления переключателем годности блока памяти, что позволяет использовать устройство для построения автономных систем памяти с большим числом адресуемых блоков памяти. Поставленная цель достигается путем введения в устройство, сос- из последовательно соединенных по адресным цепям m каналов, управляющие входы которых соединены па- раллелдьно, по одному элементу ИЛИ в каждьй канал. Кроме того, переключатель годности блока памяти каждого канала подключается вновь введенными входами к адресу своего канала и к входам записи и сброса устройства, общим для всех каналов, что и по- зволяет дистанционно управлять работой устройства, 1 ил. (Л

14)

Изобретение относится к вычислительной технике, предназначено для адресации блоков в системе памяти и является дополнительным к авт.св. № 1298755.

. Целью изобретения является расширение функциональных возможностей за счет реализации дистанционного управления переключателем годности блока памяти.

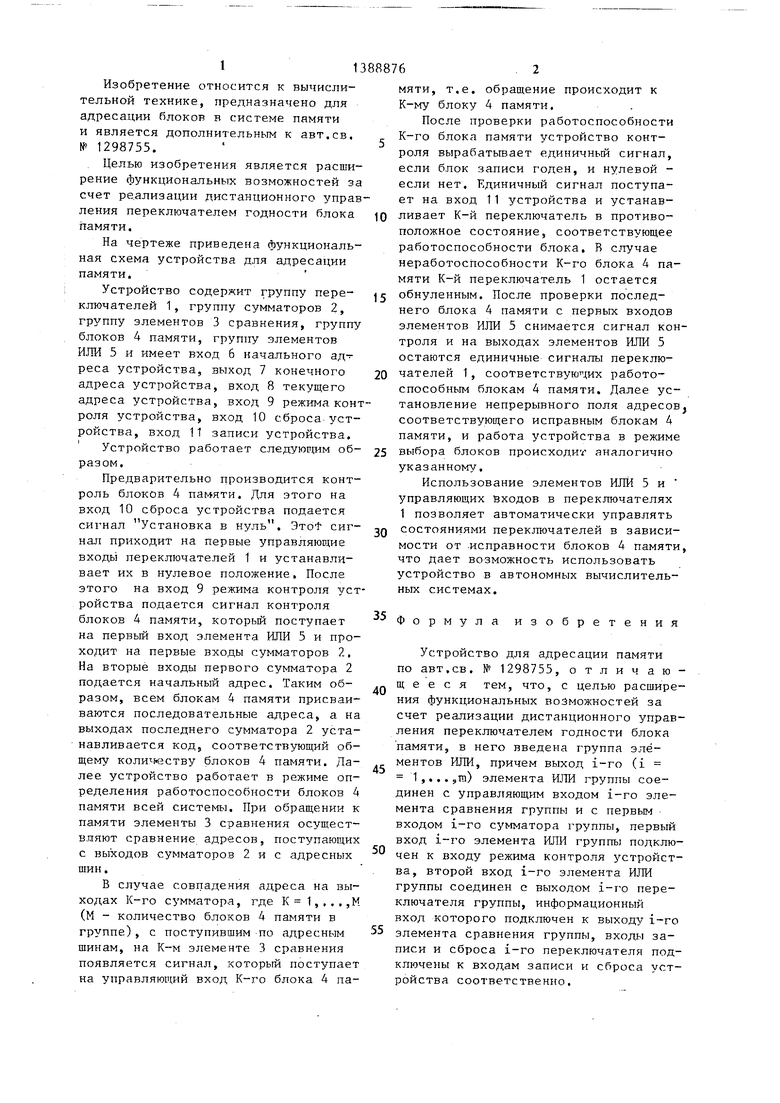

На чертеже приведена функциональная схема устройства для адресации памяти.

Устройство содержит группу переключателей 1, группу сумматоров 2, группу элементов 3 сравнения, группу блоков 4 памяти, группу элементов ИЛИ 5 и имеет вход 6 начального адреса устройства, выход 7 конечного адреса устройства, вход 8 текущего адреса устройства, вход 9 режима контроля устройства, вход 10 сброса устройства, вход 11 записи устройства.

Устройство работает следующим образом.

Предварительно производится контроль блоков 4 памяти. Для этого на вход 10 сброса устройства подается сигнал Установка в нуль. 3Tot сигнал приходит на первые управляюсдие входы переключателей 1 и устанавливает их в нулевое положение. После этого на вход 9 режима контроля устройства подается сигнал контроля блоков 4 памяти, который поступает на первый вход элемента ИЛИ 5 и проходит на первые входы сумматоров 2, На вторые входы первого cyNwaTopa 2 подается начальный адрес. Таким образом, всем блокам 4 памяти присваиваются последовательные адреса, а на выходах последнего сумматора 2 устанавливается код, соответствующий общему количеству блоков 4 памяти. Далее устройство работает в режиме определения работоспособности блоков 4 памяти всей системы. Лри обращении к памяти элементы 3 сравнения осуществляют сравнение адресов, поступающих с выходов сумматоров 2 и с адресных шин.

В случае совцадения адреса на выходах К-го сумматора, где К 1, , , . ,М (М - количество блоков 4 в группе), с поступившим по адресным шинам, на К-м элементе 3 сравнения появляется сигнал, который поступает на управляющий вход К-го блока 4 памяти, т.е. обращение происходит к К-му блоку 4 памяти.

После проверки работоспособности К-го блока памяти устройство контроля вырабатьгоает единичный сигнал, если блок записи годен, и нулевой - если нет. Кдиничный сигнал поступает на вход 11 устройства и устанавливает К-й переключатель в противоположное состояние, соответствующее работоспособности блока, В случае неработоспособности К-го блока 4 памяти К-й переключатель 1 остается

обнуленным. После проверки последнего блока 4 памяти с первых входов элементов ИЛИ 5 снимается сигнал контроля и на выходах элементов ИЛИ 5 остаются единичные сигналы переключателей 1, соответствующих работоспособным блокам 4 памяти. Далее установление непрерывного поля адресов соответствующего исправным блокам 4 памяти, и работа устройства в режиме

выбора блоков происходит аналогично указанному.

Использование элементов ИЛИ 5 и управляющих Входов в переключателях 1 позволяет автоматически управлять

состояниями переключателей в зависимости от .исправности блоков 4 памяти, что дает возможность использовать устройство в автономных вычислительных системах.

35

Формула изобретения

5

Устройство для адресации памяти по авт.ев, № 1298755, отличаю- -. щ е е с я тем, что, с целью расширения функциональных возможностей за счет реализации дистанционного управления переключателем годности блока памяти, в него введена группа элементов ИЛИ, причем выход i-ro Ci 1 ,,,. .,rn) элемента ИЛИ группы соединен с управляющим входом i-ro элемента сравнения группы и с первым входом i-ro сумматора группы, первый

вход i-ro элемента ИЛИ группы подклю0

чен к входу режима контроля устройства, второй вход i-ro элемента ИТМ группы соединен с выходом i-ro переключателя группы, информационный вход которого подключен к выходу i-ro

элемента сравнения группы, входы записи и сброса i-ro переключателя подключены к входам записи и сброса устройства соответственно.

S 9 1011

| Устройство для адресации памяти | 1985 |

|

SU1298755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-15—Публикация

1986-09-15—Подача