Изобретение относится к автоматике и вычислительной технике и может быть применено для адресации блоков памяти в стандартных платах на базе частично годных кристаллов.

Целью изобретения является расширение области применения и упрощение устройства за счет уменьшения количества корпусов микросхем, участвующих в организации непрерывного поля адресов в стандартных платах памяти на базе частично годных кристаллов.

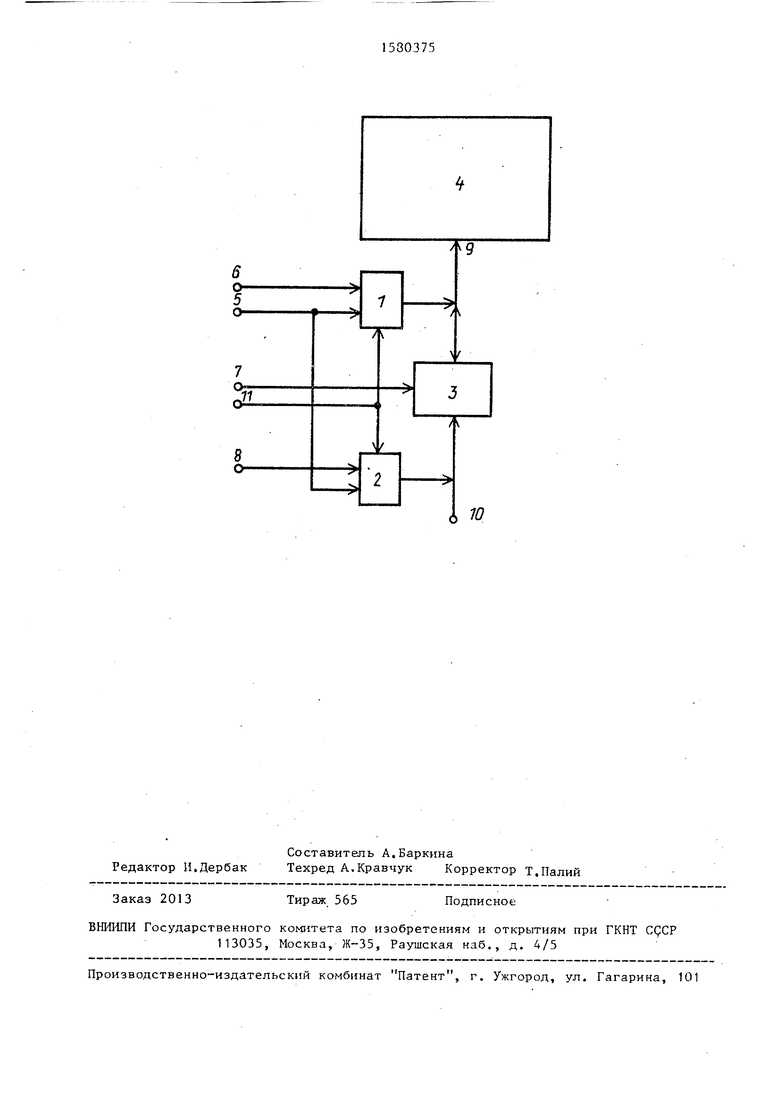

На чертеже представлена функциональная схема устройства для адресации блоков памяти.

Устройство содержит счетчики 1 и 2, блок 3 оперативной памяти, систему 4 памяти, вход 5 сброса устройства, тактируемый вход б устройства, вход 7 записи-считывания устройства, вход 8 установки флага годности устройства, адресные выход 9 и вход 10 устройства, вход 11 режима работы устройства.

Устройство может работать в режиме присвоения условных непрерывных адресов работоспособным блокам - подматрицам системы 4 памяти и в режиме обращения к блокам системы 4 памяти.

Режим присвоения условных непрерывных адресов работоспособным блокам памяти осуществляется следующим образом,

Сигналом Сброс с входа 5 устройства производится установка в начальное состояние счетчиков 1 и 2,

На вход 11 режима работы устройства подается сигнал Контроль, который поступает на управляющие входы счетчиков 1 и 2 и убирает третье состояние, адресный вход 10 устройства в режиме контроля устанавливается в третье состояние.

На вход счетчика 1 поступает тактовый импульс с входа 6 устройства и устанавливает первый адрес обращения к системе 4 памяти, который поступа(Л

ел

00

о

СО

1

СП

3153

от на адресные входы 9 системы памяти vi возбуждает ее первый блок - подматрицу .

Если блок работоспособен, то по окончании контроля на вход счетчика 2 с вхсда 8 устройства поступает сигнал годности первого блока системы 4 памяти, который устанавливает на выходе счетчика 2 первый адрес годного блока,Эта информация поступает на адресные входы блока 3 памяти, а на его управляющие входы с входа 7 записи- считывания устройства приходит син- хросерия сигналов записи в блок 3 па- мяти и производится запись информации со счетчика 2 по адресу со счетчи- . ка 1.

В случае, если первый блок негоден, запись в блок 3 памяти не производится, а на вход 6 устройства поступает следующий второй тактовый импульс, который увеличивает содержимое счетчика 1 на единицу, и начинается контроль второго блока системы 4 памяти,

Если второй блок работоспособен (а первый нет), то по окончании контроля на вход счетчика 2 с входа 8 устройства поступает сигнал годности второго блока, который устанавливает на выходе счетчика 2 информацию о пер- i вом годном блоке, Эта информация поступает на адресные входы блока 3 па- мяти, а на входы 7 записи-считывания приходит синхросерия сигналов (сигнал записи + синхроимпульс) в блок 3 памяти и по первому адресу пришедшего со счетчика 2 производится запись информации со счетчика (код проверенного блока). Таким образом, по первому адресу в блоке 3 памяти, записан физический адрес первого годного блока системы 4 памяти, по второму адресу - второго блока и т.д.

Го окончании контроля последнего блока памяти блок 3 памяти хранит последовательность кодов адресов годных блоков системы 4 памяти, т.е.по i-му адресу в блоке 3 памяти хранит54

ся j-й код (адрес) j-ro годного блока системы 4 памяти,

В режиме обращения к годным блокам системы 4 памяти с входа 11 режима работы устройства сигнал Контроль убирается и счетчики 1 и 2 устанавливаются в третье состояние.

На адресный вход 10 устройства поступает текущий адрес обращения. На вход 7 устройства поступает синхросе- рия сигналов считывания (считывание + синхроимпульс). По i-му логическому адресу из блока 3 считывается j-й физический адрес годного блока системы памяти, который с адресного выхода 9 устройства поступает на адресный вход системы 4 памяти и возбуждает j-й год- ный блок Время обращения к j-му годному блоку определяется временем считывания из блока 3 памяти.

Формула изобретения

Устройство для адресации блоков памяти, содержащее первый и второй счетчики и блок оперативной памяти, о тл и ч ающе ее я тем, что, с целью расширения областиприменения иупроще- иия устройства за счет уменьшения количества корпусов микросхем в стандартных платах по базе частично годных кристаллов, вход сброса устройства соединен с входами сброса первого и второго счетчиков, тактируемый вход устройства соединен со счетным входом первого счетчика, вход записи-чтения устройства соединен с управляющим входом блока оперативной памяти, вход режима работы устройства соединен с управляющими входами первого и второго счетчиков, вход установки флага годности устройства соединен со счетным входом второго счетчика, адресный вход устройства соединен с выходом второго счетчика и адресным входом блока оперативной памяти, информационный выход блока оперативной памяти соединен с выходом первого счетчика и адресным выходом устройства.

6 О

5 о

А

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации блоков памяти | 1986 |

|

SU1394217A1 |

| Устройство для адресации памяти | 1986 |

|

SU1388876A2 |

| Устройство для адресации блоков памяти | 1989 |

|

SU1679490A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для адресации памяти | 1989 |

|

SU1656543A1 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1388875A2 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для адресации блоков памяти | 1988 |

|

SU1575189A1 |

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при изготовлении стандартных плат памяти на базе частично годных кристаллов. Целью изобретения является расширение области применения и упрощение устройства за счет уменьшения количества корпусов микросхем, участвующих в организации непрерывного поля адресов в стандартных платах памяти на базе частично годных кристаллов. Устройство может работать в режиме присвоения условных непрерывных адресов годным блоком памяти и в режиме обращения к годным блокам памяти. 1 ил.

7 о

Л

Редактор И.Дербак

Составитель А.Баркина

Техред А.Кравчук Корректор Т.Палий

Заказ 2013

Тираж 565

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ С(СР 113035, Москва, Ж-35, Раушская нлб., д. 4/5

Подписное

| Приспособление для настройки струнного музыкального инструмента | 1983 |

|

SU1293755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4627016, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-11-21—Подача