1

(21)4637714/24

(22)13.01.89

(46) 07.01.91. Бюп. № 1

(72) А.И.Беляков, С.Е.Прошин

и В.В.Чернов

(53)681.325(088.8)

(56)Авторское свидетельство СССР № 1417003, кл. G 06 F 12/08, 1986.

Шевкопляс В.В. Микропроцессорные структуры. Инженерные решения. - М.: Радио и связь, 1986, с.44.

(54)УСТРОЙСТВО АДРЕСАЦИИ

(57)Изобретение относится к вычислительной технике и может быть использовано для построения систем оперативной памяти ЭВМ большой информационной емкости. Целью изобретения является расширение функциональных возможностей путем динамического изменения размеров и расположения физических областей памяти. Устрой- ство содержит блоки 1-3 регистров, мультиплексоры 4, 5, блок 6 сравнения, блок 7 памяти таблиц адресации, сумматор 8. Поставленная цель достигается введением новых элементов и связей. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство адресации оперативной памяти | 1987 |

|

SU1417003A1 |

| Устройство адресации оперативной памяти | 1985 |

|

SU1262497A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

Данные

зш

ч

У|

-ё

-% -5

Адрес М л

Qnflof

tf

J/iaEmu

коэфсрици ffffg перекрытия

л+г

Art

Изобретение относится к вычислительной технике и может быть использовано для построения систем оперативной памяти ЭВМ большой информационной емкости.

Цель изобретения - расширение функциональных возможностей за счет динамического изменения размеров и расположения физических областей памяти.

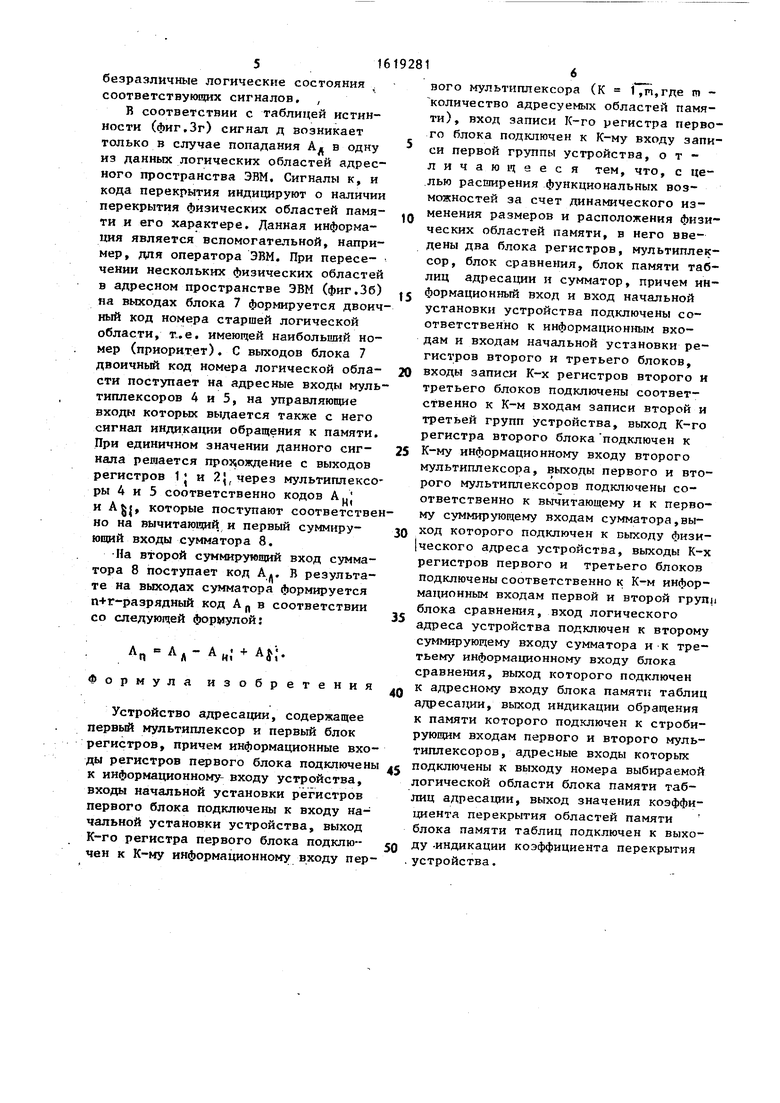

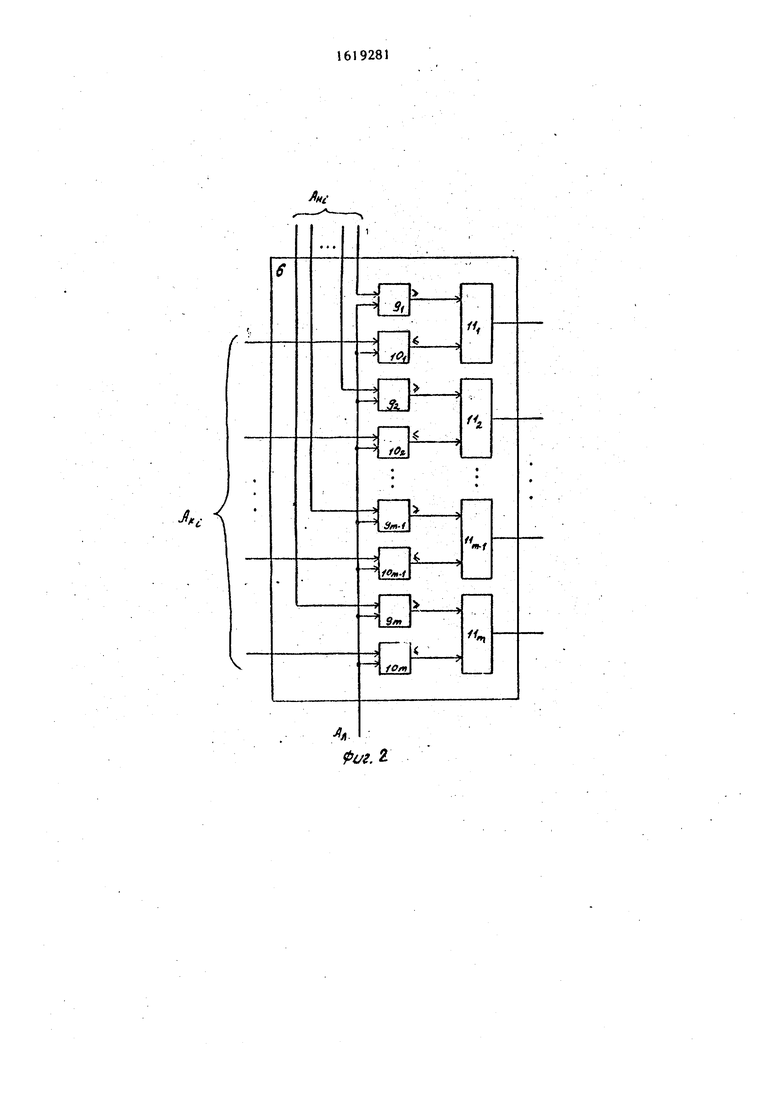

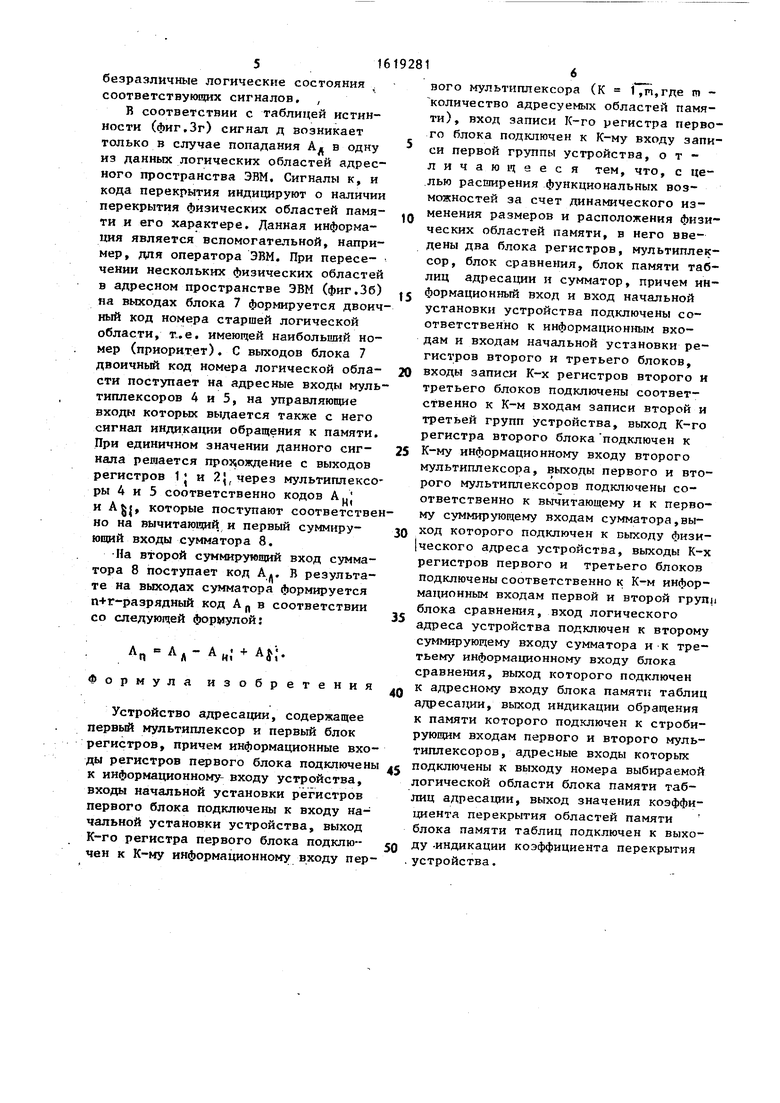

На фиг.1 приведена структурная схема устройства; на фиг.2 - функциональная схема блока сравнения; на фиг.З - пример структурной схемы бло ка памяти таблиц адресации и примеры записанных в нем таблиц.

Устройство содержит блок 1 регистров , блок 2 регистров 2,-2т, блок 3 регистров 3ffl, мультиплек соры А и 5, блок 6 сравнения, блок 7 памяти таблиц адресации, сумматор 8, схемы элементы И 11,- 11т

и Ю,-10т сравнения,

Устройство работает следующим образом.

По сигналу Сброс, вырабатываемому после включения питания ЭВМ, производится установка регистров блоков 1-3 в исходное нулевое состояние (цепи начальной установки регистров не показаны). При этом в адресном пространстве ЭВМ активизируется начальная физическая область адресного пространства памяти. При необходимости изменения конфигурации размещения физических областей в адресном пространстве ЭВМ в регистры блоков 1-3 заносится следующая информация : в регистры блока 1 - соответ- ственно начальные адреса A W)% (,m) логических областей адресного пространства ЭВМ; в регистры блока 3 - соответственно конечные адреса А «, (i 17го) логических областей адресного пространства ЭВМ;в регистры блока 2 - соответственно базовые физические адреса А (i 17гё) физических областе памяти, активизируемых в одноименных логических областях адресного прост-, ранства ЭВМ. Запись в регистры блоков 1-3 осуществляется путем подачи на входы записи регистров блоков соответственно сигналов записи зап,н1 - зап.нтп, зап.к - зап.ктч, зап.61 - зап.бгС Записываемая в регистры информация поступает на их входы с информационного входа устройства.

5

0

При подаче на адресный вход устройства n-разрядного логического адреса обращения А, производится его преобразование в n+r-разрядный физический адрес памяти АП в зависимости от установленного варианта распределения физических областей памяти в адресном пространстве ЭВМ.

При поступлении текущего Ад на первый вход блока 6 сравнения производится определение номера логической области памяти в адресном пространстве ЭВМ, которой принадлежит данное значение Ад. Для этого производится сравнение значения А, с

Аи,(

и А ц| каждой

i-й (i 1 ,тп) логической области адресного пространства ЭВМ. При этом на выходах схем 9 сравнения первой группы и 10, второй группы возникают единичные сигналы соответственно при

5

5

0

0 5 Q

5

А л А

Л АИ

и А

И1 VM

и А л Ј A|J. Коды адресов поступают на первые входы

, и 10, сравне- выходов соответствующих регистсоответствующих схем 9

ния

ров 1, и 3, блоков 1 и 3. Код адреса Ад поступает на объединенные вторые входы схем 9 и 10 сравнения. При попадании значения А д в i-ю логическую область адресного пространства ЭТО соответственно на выходах схем 9 J и 10, сравнения и элемента И 11 возникает единичный сигнал. При этом на выходах остальных элементов И 11 присутствуют нулевые сигналы,Таким образом на выходах блока б сравнения мируется унитарный позиционный код номера логической области адресного пространства ЭВМ. Этот код поступает на входы блока 7, на соответствующих выходах которого формируются сигнал индикации обращения к памяти, двоичный код номера логической области адресного пространства ЭВМ и код коэффициента перекрытия физических областей адресного пространства памяти в данной логической области адресного пространства ЭВМ.

i

На фиг.За-Зг показаны таблицы истинности выходных сигналов блока 7 (фиг.За), где а, б, в, г - сигналы унитарного кода номера логической области; е, ж - сигналы двоичного кода номера логической области; д - сигнал индикации обращения к памяти; и, к - сигналы кода коэффициента перекрытия физических областей. Знаком -И обозначены произвольные либо

безразличные логические состояния соответствующих сигналов, ,

В соответствии с таблицей истинности (фиг.Зг) сигнал д возникает только в случае попадания Ад в одну из данных логических областей адресного пространства ЭВМ. Сигналы к, и кода перекрытия индицируют о наличии перекрытия физических областей памяти и его характере. Данная информация является вспомогательной, например, для оператора ЭВМ. При пересечении нескольких физических областей в адресном пространстве ЭВМ (фиг.36) на выходах блока 7 формируется двоичный код номера старшей логической области, т.е. имеющей наибольший номер (приоритет), С выходов блока 7 двоичный код номера логической области поступает на адресные входы мультиплексоров 4 и 5, на управляющие входы которых выдается также с него сигнал индикации обращения к памяти. При единичном значении данного сигнала решается прохождение с выходов регистров 1j и 2{, через мультиплексоры 4 и 5 соответственно кодов A..J и Аь«, которые поступают соответствено на вычитающий и первый суммирующий входы сумматора 8.

На второй суммирующий вход сумматора 8 поступает код А. В результате на выходах сумматора формируется n+r-разрядный код А„ в соответствии со следующей формулой:

1п

Ад- АМ1AtfФормула изобретения

Устройство адресации, содержащее первый мультиплексор и первый блок регистров, причем информационные входы регистров первого блока подключены де подключены к выходу номера выбираемой

к информационному- входу устройства, входы начальной установки регистров первого блока подключены к входу начальной установки устройства, выход К-го регистра первого блока подклю50

логической области блока памяти таблиц адресации, выход значения коэффициента перекрытия областей памяти блока памяти таблиц подключен к выходу -индикации коэффициента перекрытия

чен к К-му информационному входу пер- .устройства.

0

5

0

5

0

5

0

вого мультиплексора (К 1,я,где m - количество адресуемых областей памяти), вход записи IC-ro регистра первого блока подключен к К-му входу записи первой группы устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет динамического изменения размеров и расположения физических областей памяти, в него введены два блока регистров, мультиплексор, блок сравнения, блок памяти таблиц адресации и сумматор, причем информационный вход и вход начальной установки устройства подключены соответственно к информационным входам и входам начальной установки регистров второго и третьего блоков, входы записи К-х регистров второго и третьего блоков подключены соответственно к К-м входам записи второй и третьей групп устройства, выход К-го регистра второго блока подключен к К-му информационному входу второго мультиплексора, выходы первого и второго мультиплексоров подключены соответственно к вычитающему и к первому суммирующему входам сумматора,выход которого подключен к выходу физи- |ческого адреса устройства, выходы К-х регистров первого и третьего блоков подключены соответственно к К-м информационным входам первой и второй групп блока сравнения, вход логического адреса устройства подключен к второму суммирующему входу сумматора и к третьему информационному входу блока сравнения, выход которого подключен к адресному входу блока памяти таблиц адресации, выход индикации обращения к памяти которого подключен к строби- рующим входам первого и второго мультиплексоров, адресные входы которых

подключены к выходу номера выбираемой

логической области блока памяти таблиц адресации, выход значения коэффициента перекрытия областей памяти блока памяти таблиц подключен к выходу -индикации коэффициента перекрытия

Л

,

Авторы

Даты

1991-01-07—Публикация

1989-01-13—Подача