в соответствующие циклы происходит прием информации в блок 26 приема команд. Если входной тракт активизирован (пришла команда управления проключением), вся следующая информация передается в память 7, в тол числе и следующие команды управления проключением, предназначенные для других коммутаторов. Активизация входного тракта снимается при пос- туплении команды разъединения.

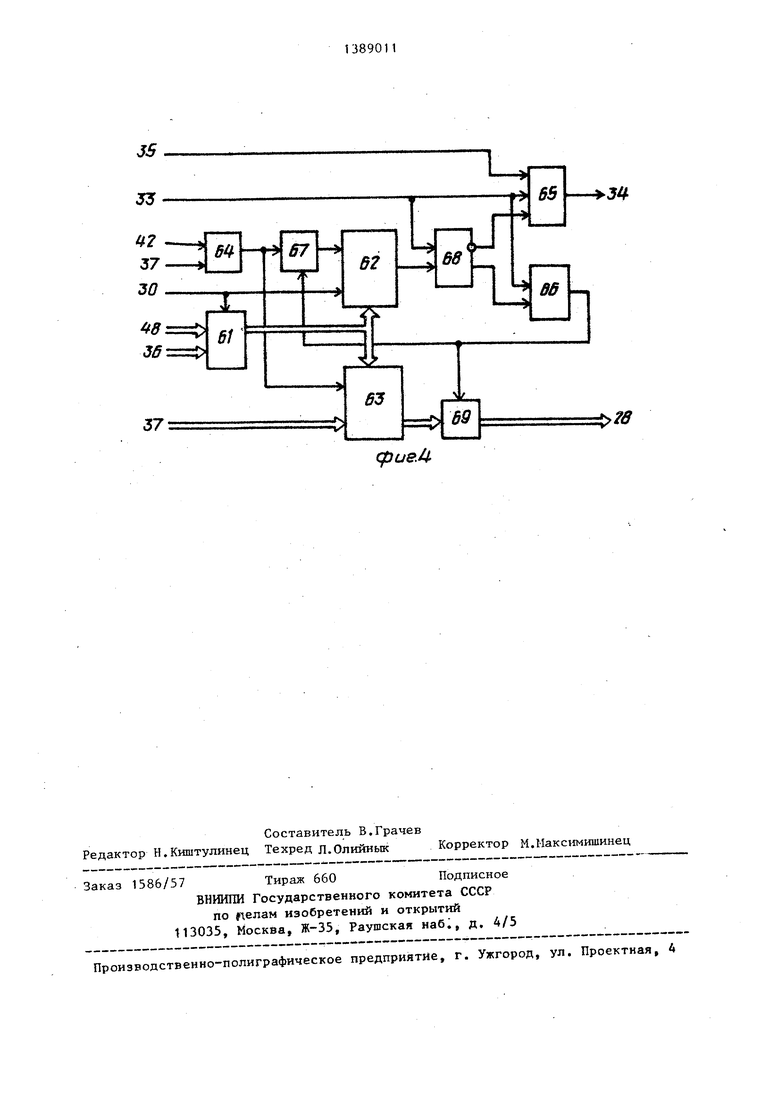

Если процессор записал команду подтверждения в блок 27 передачи команд, то одновременно с этим в памят 62 (указатель выходных команд) запишется 1, При чтении 1 с выхода памяти 62 в триггер 68 запишется 1 что приводит к , что регистр 21 будет в такте ТЗ, а регистр 69 открыт, пропуская информацию на шину 28. Регистр 21 открывается только тогда, когда из памяти 62 считывается О, а из одного из разрядов памяти 8, определяющего факт проключе- ния тракта, считывается 1. Если ;тракт не проключен (на выходе регистра 22, соединенного с элементом И 65 - О), регистр 21 закрыт. В этом случае в преобразователь 6 запишется информация, которая определена как команда разъединения (все разряды ну левые). Это обеспечивает автоматическое разъединение пути всеми коммутаторами коммутационного поля.

Режим приема команд.

т-

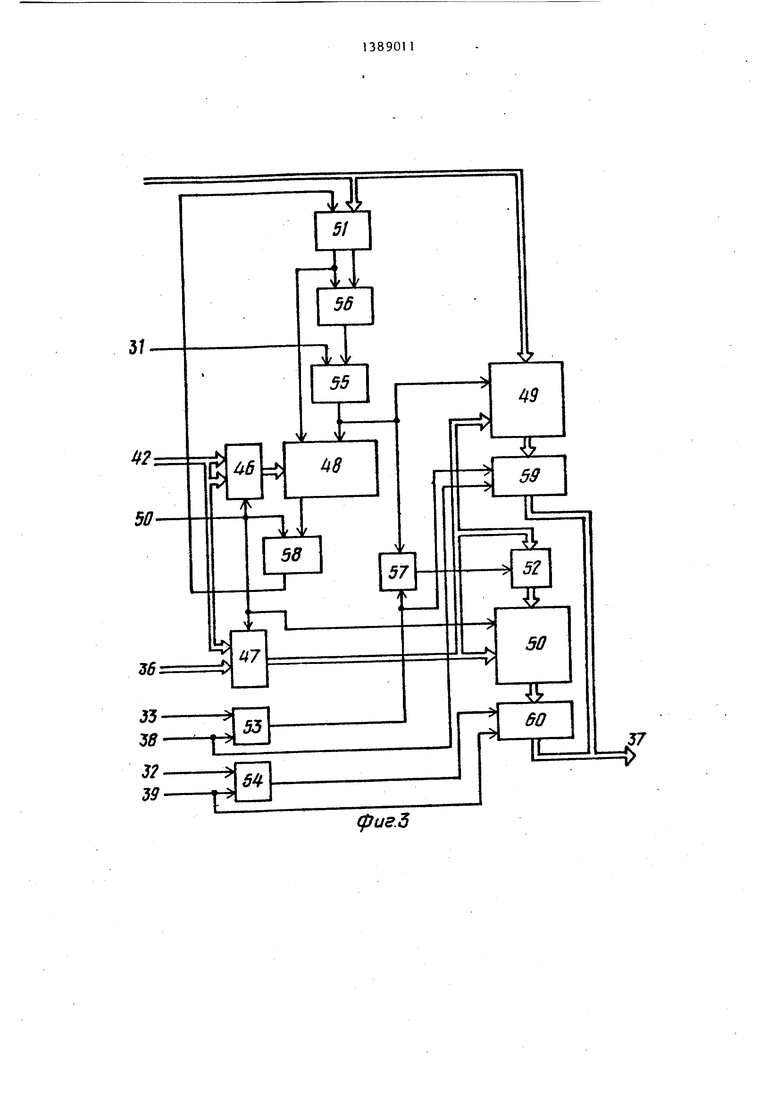

Функцию вьщеления команд выполня ет дешифратор 51. Он выделяет два типа команд: команду управления проключением и команду разъединения. В на

команды управления проключением. Во время активности тракта дешифратор 51 не реагирует на поступающие команды управления и реагирует ни ко- манды разъединения, а в неактивном

состоянии входного тракта дешифратор 51 не реагирует на команды разъеди- ,нения и реагирует на команды управления, приходящих по данному тракту. Это обеспечивает выделение только тех команд, на которые должен реагировать коммутатор, вернее, процессор, управляющий ко1-1мутатором. Все остальные

команды проходят в память 7. .

5

5

40

5

Обнаружив команду, совокупность - - блоков 51, 55, 56 формирует импульсы записи, поступающих на входы записи памятей 48-49 и через элемент ШШ 57 и дешифратор 52 - на один из входов записи памяти 50 указателя входных команд, где накапливаются 1, сигнализирующие о поступивших в память 49 команд. Процессор, прочитав через блок 10 информацию из памяти 50, знает сразу о нескольких поступивших командах, Адрес, по которому поступили команды в память 49, определяется совокупностью адреса, по которому осуществлялось чтение па- мяти 50, и номера разряда, в котором записана 1. Далее процессор по этому адресу может прочитать команду из памяти 49 и выполнить ее. Результат выполнения должен выразится в записи в памяти 8 соединений соответствующей информации: либо проключение тракта с определенной коммутацией, либо отключение тракта. Одновременно с чте

1113

выход которого соединен с управляющи входом буферного регистра, управляющий выход второго регистра соединен .с входом разрешения блока передачи команд, первый тактовый выход блока синхронизации соединен с первыми тактовыми входами блоков приема и передачи команд и тактовым входом речевой памяти, второй тактовый выход бло ка синхронизации соединен с вторым тактовым входом блока приема команд, третий тактовый выход блока синхронизации соединен с третьим тактовым входом блока приема команд, вторым тактовым входом блока передачи коман и вторым входом элемента И, а адресный вход памяти соединений соединен с выходом второго мультиплексора.

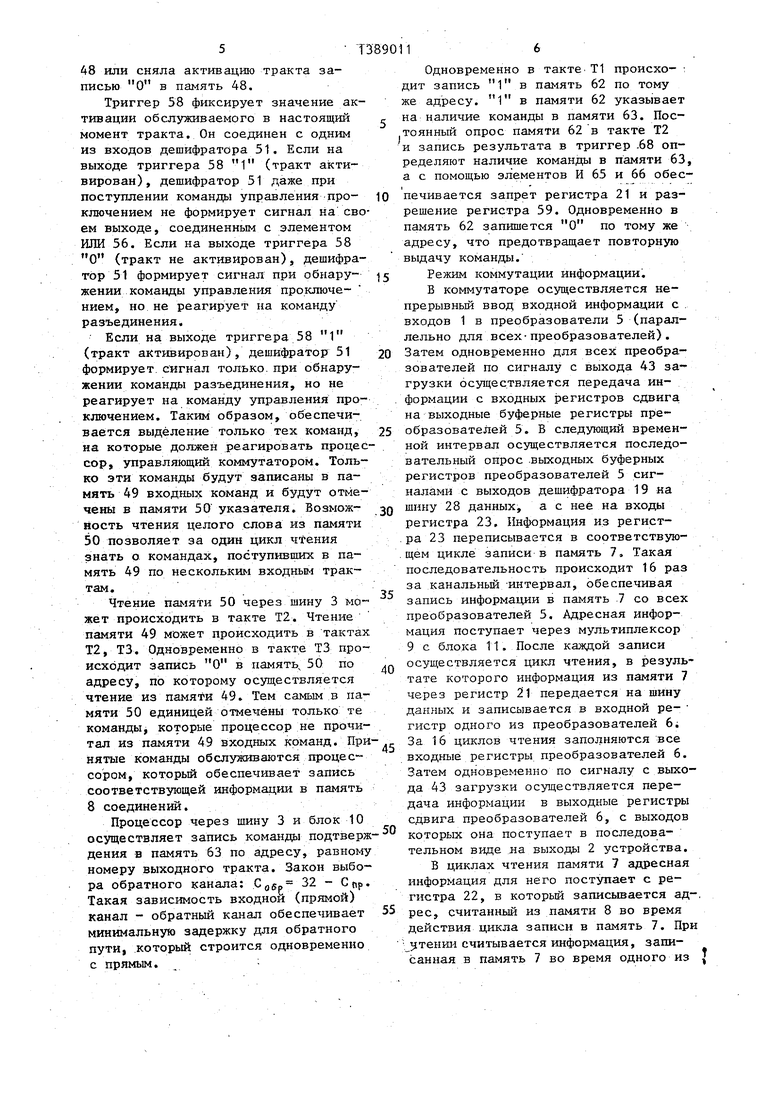

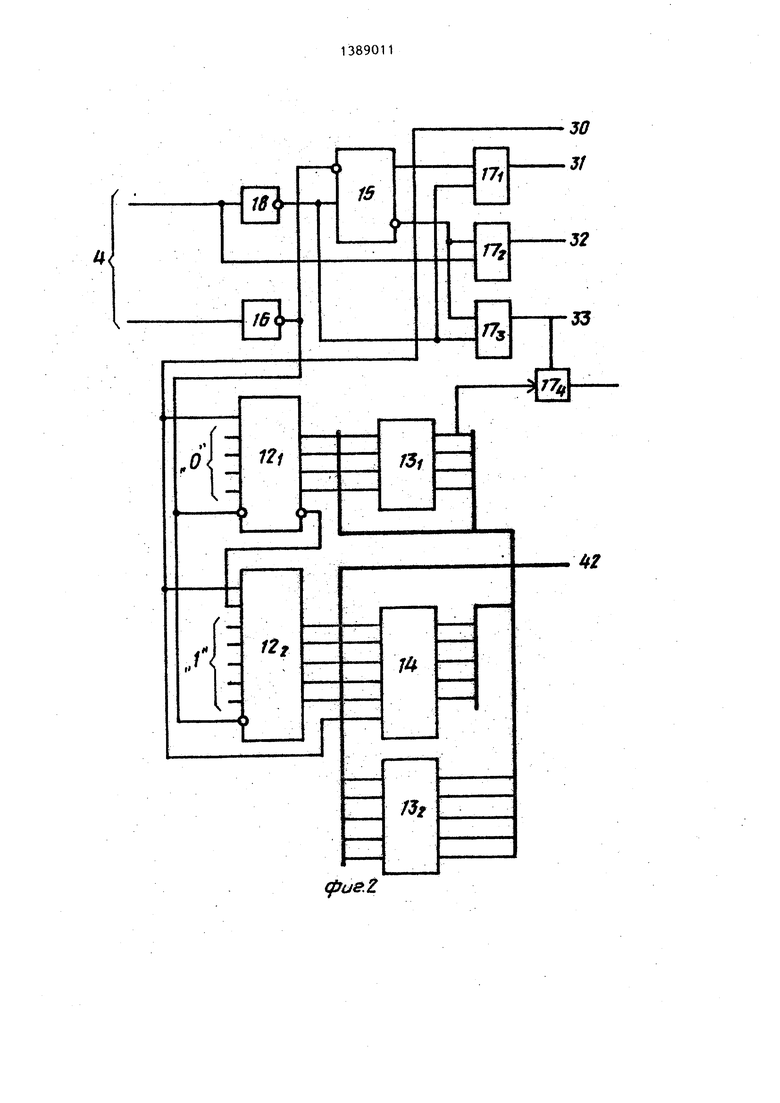

2, Коммутатор по п. 1, о т л и - чающийся тем, что.блок приема команд содержит память входных команд память активности входных трактов, память указателей, два регистра, два мультиплексора, два де- шифратора, триггер, два элемента ИЛИ три элемента И, причем информационный вход блока соединен с информационными входами памяти входных ко- манд и первого дешифратора, выходы которого соединены с информационным входом памяти активности входных трактов и входами первого элемента ИЛИ, выход которого и первый тактовый вход блока через первый элемент И соединены с управляющими входами памяти входных команд, памяти активности входных трактов и первым входом второго элемента ИЛИ, выход которого соединен с управляющим входом второго дешифратора, выход которого соединен с информационным входом памяти указателей, выход которого соединен с информационным входом первого регистра, выходы которого и второго регистра соединены с информаци- онным выходом блока, первый адресный вход которого соединен с первым информационным входом первого мультиплексора и информационным входом второго мультиплексора, выход которого соединен с адресным входом памяти активности входных трактов, выход кото рой соединен с входом триггера, выход которого соединен с управляющим входом первого дешифратора, синхро- вход блока соединен с синхровходами первого и второго мультиплексоров, триггера и памяти указателей, второй адресный вход блока соединен с вторы

1-12

информационным входом первого мультиплексора, выход которого соединен с информационным входом второго дешифратора и адресными входами памяти указателей и памяти входных команд, выход которой соединен с информацион- . ным входом второго регистра, первый управляющий вход блока соединен с первым входом второго элемента И и первым управляющим входом второго регистра, второй управляющий вход блока соединен с первым входом третьего элемента И и первым управляющим входом первого регистра, второй тактовый вход блока соединен с вторым входом третьего элемента И, выход которого соединен с вторым управляющим входом первого регистра, третий тактовый вход блока соединен с вторым входом второго элемента И, выход которого соединен с вторым управляющим входом второго регистра и вторым входом второго элемента ИЛИ.

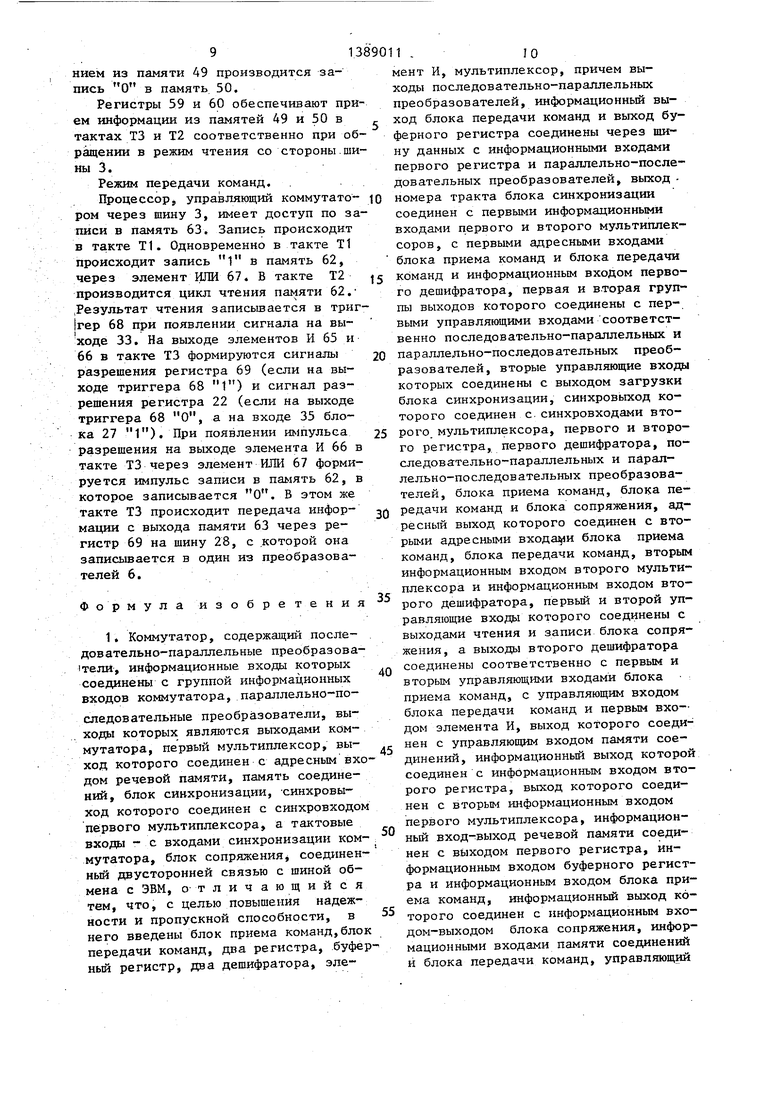

3. Коммутатор по п.

отли

чающийся тем, что блок передачи команд содержит память выходных команд, память указателей, триггер, мультиплексор, регистр, элемент ИЛИ, три элемента И, причем информационный вход блока соединен с информационным входом памяти выходных команд, выход которой соединен через регистр с информационным выходом блока, первый и второй адресные входы которого через мультиплексор соединены с адресными входами памяти выходных команд к памяти указателей, син- хровход которой соединен с синхро- входом блока и синхровходом мультиплексора, управляющий и первый тактовый входы блока через первый элемент И соединены с управляющим входом памяти выходных команд и первым входом элемента ИЛИ, выход которого соединен с управляющим входом памяти указателей, выход которой соединен с первым входом триггера, выходы которого соединены с первыми входами соответственно второго и третьего элементов И, второй тактовьм вход блока соединен с вторым входом триггера и вторыми входами второго и третьего элементов И, вход разрешения соединен с третьим входом третьего элемента И, выход которого соединен с заправляющим выходом блока, выход второ - го элемента И соединен с управляющим входом регистра и вторым входом эле-; мента ИЛИ.

Iff

/Д

ni

17f

/7,

У О J/

J

33

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1989 |

|

SU1716622A2 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Многоканальный временной коммутатор | 1988 |

|

SU1647922A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Диспетчер памяти ЭВМ | 1990 |

|

SU1718225A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1997 |

|

RU2121754C1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

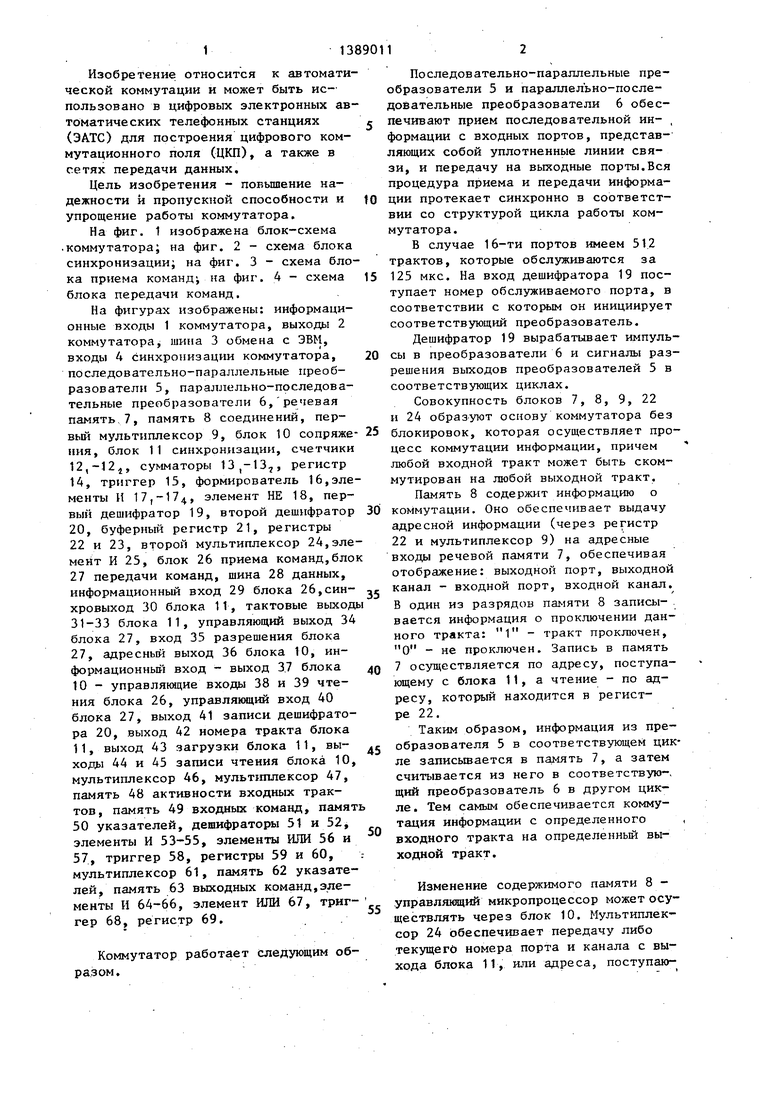

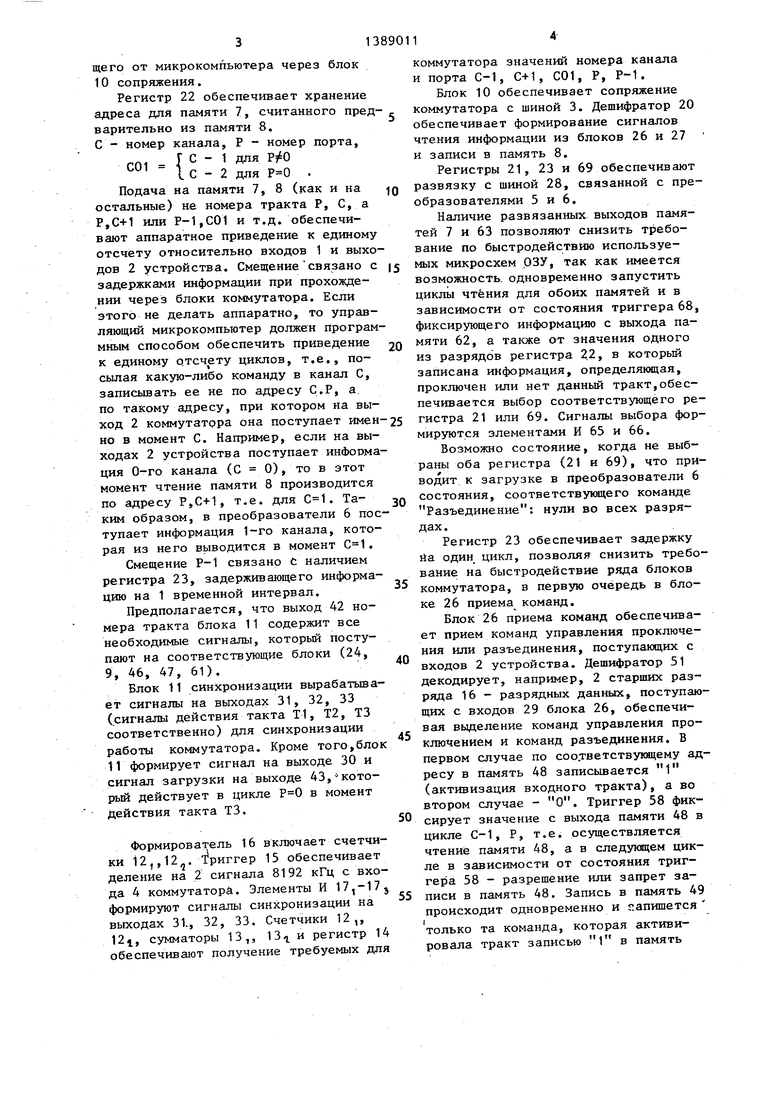

Изобретение относится к автоматической коммутации и может быть использовано в цифровых электронных автоматических телефонных станциях для построения цифрового коммутационного поля,а также в сетях передачи данных. Цель изобретения - повышение надежности и пропускной способности и упрощение работы коммутатора. Для достижения цели в устройство введены блок приема команд 26, блок передачи команд 27, два дешифратора 19, 20, буферный регистр 21, два регистра 22, 23, мультиплексор 24, элемент И 25. Блок приема команд 26 содержит память входных команд, память актив- ио(;ти входных трактов, память указателей, два регистра, два мультиплексора, два дешифратора, триггер, два элемента ИЛИ, три элемента И. Блок передачи команд 27 содержит память выходных команд, память указателей, триггер-, мультиплексор, регистр, элемент ИЛИ, три элемента И. Коммутатор работает в трех режимах: в режиме коммутации информации, в режиме приема команд, и в режиме передачи команд. 2 з.п. ф-лы, 4 ил. С/)

0

12i

12,

(pu&.Z

Й

rsi

n

(pue.S

(риеЛ

| Патент ФРГ № 3109808, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ изготовления и применения масс для многоцветного печатания | 1924 |

|

SU2040A1 |

| - Электроники, 1982, № 24, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

Авторы

Даты

1988-04-15—Публикация

1987-01-04—Подача