Изобретение относится к вычислительной технике и может быть использовано в специализированных микропроцессорных системах для параллельной обработки больших массивов информации в реальном масштабе времени.

Цель изобретения - повьшение быстродействия устройства.

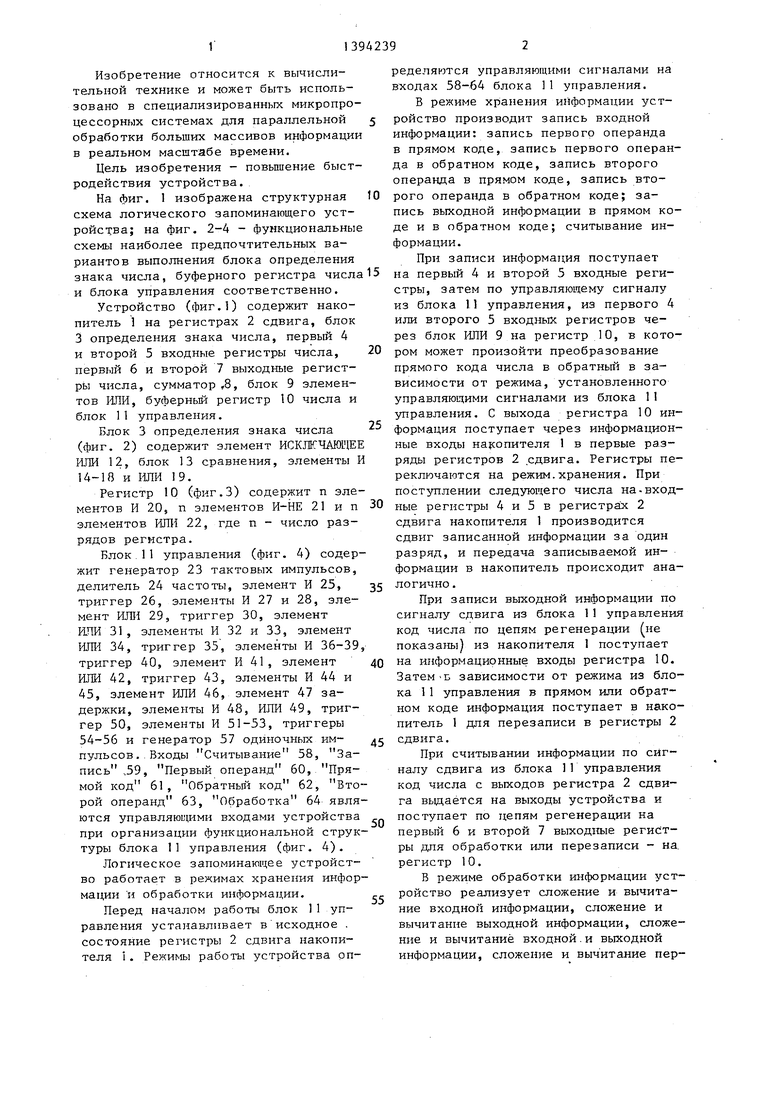

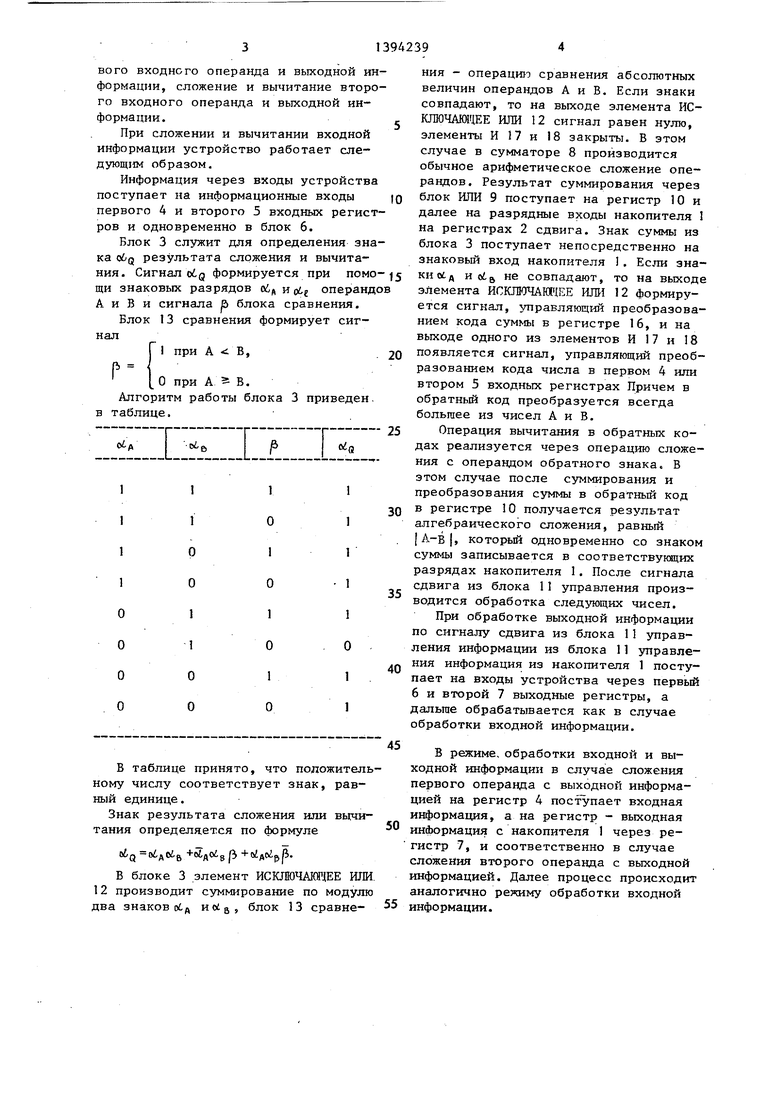

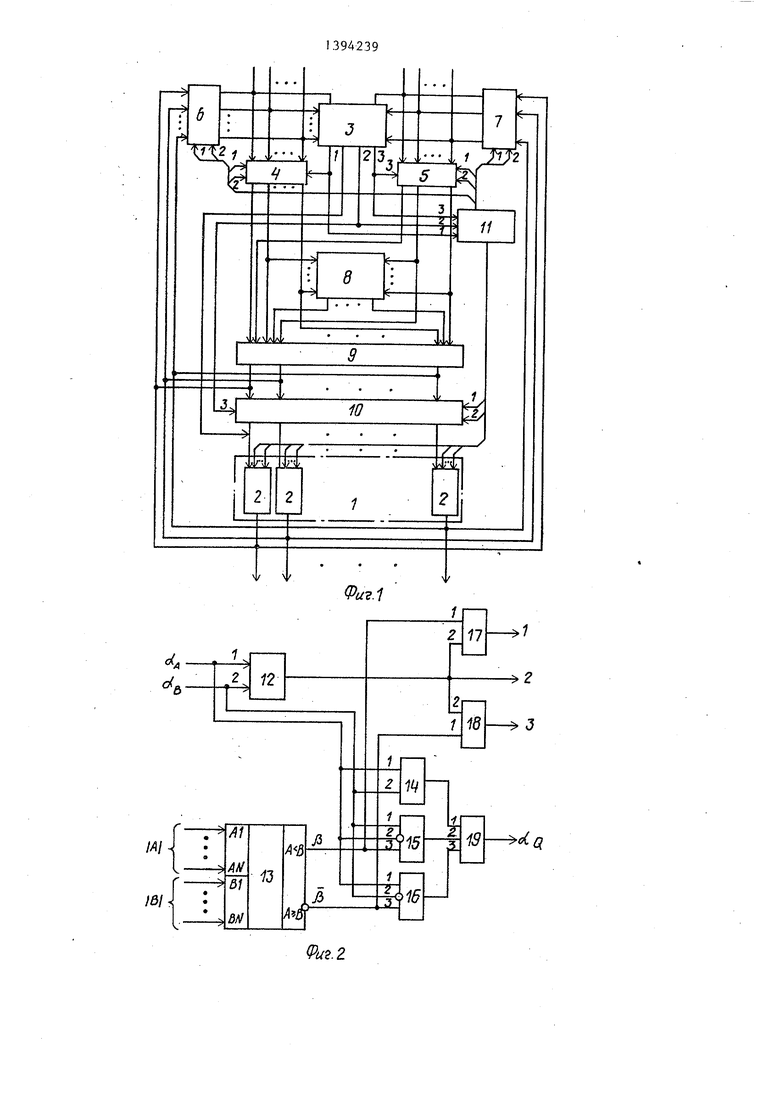

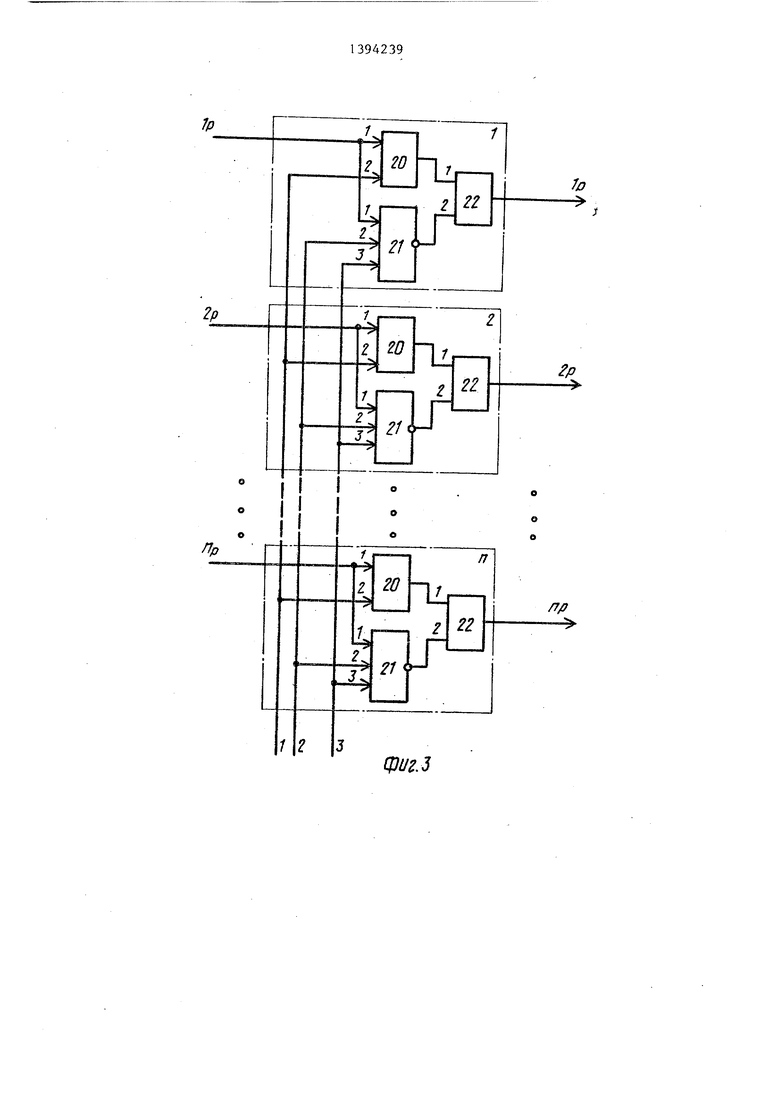

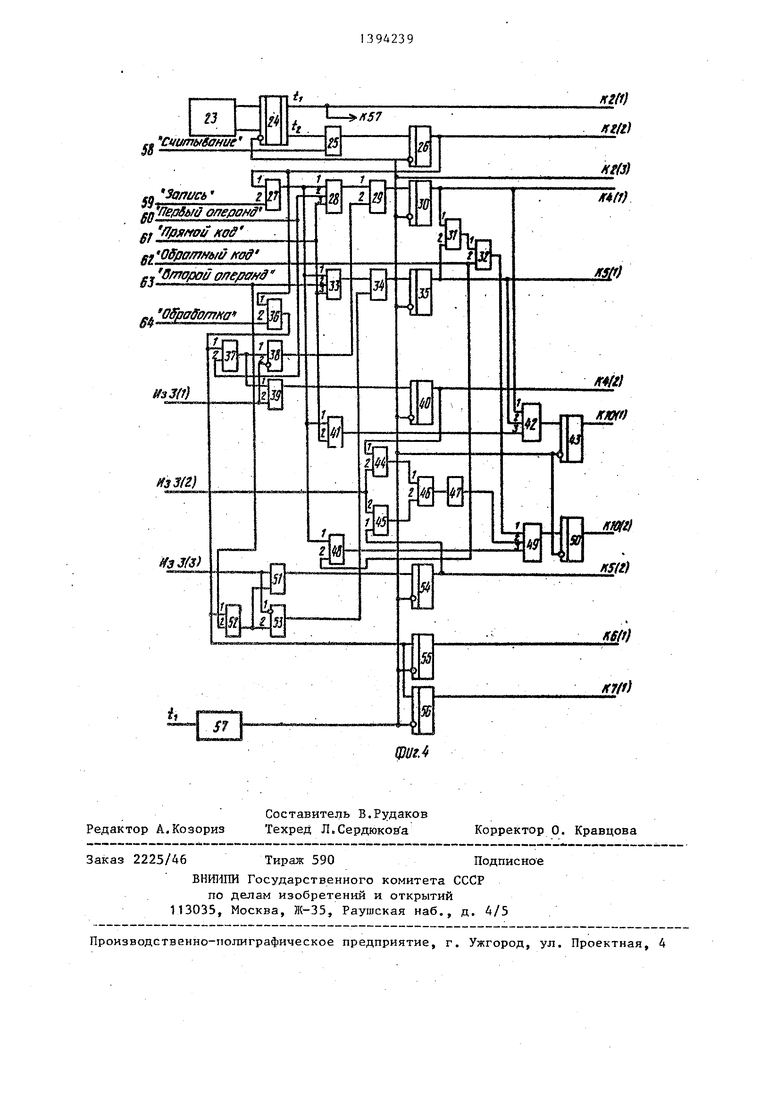

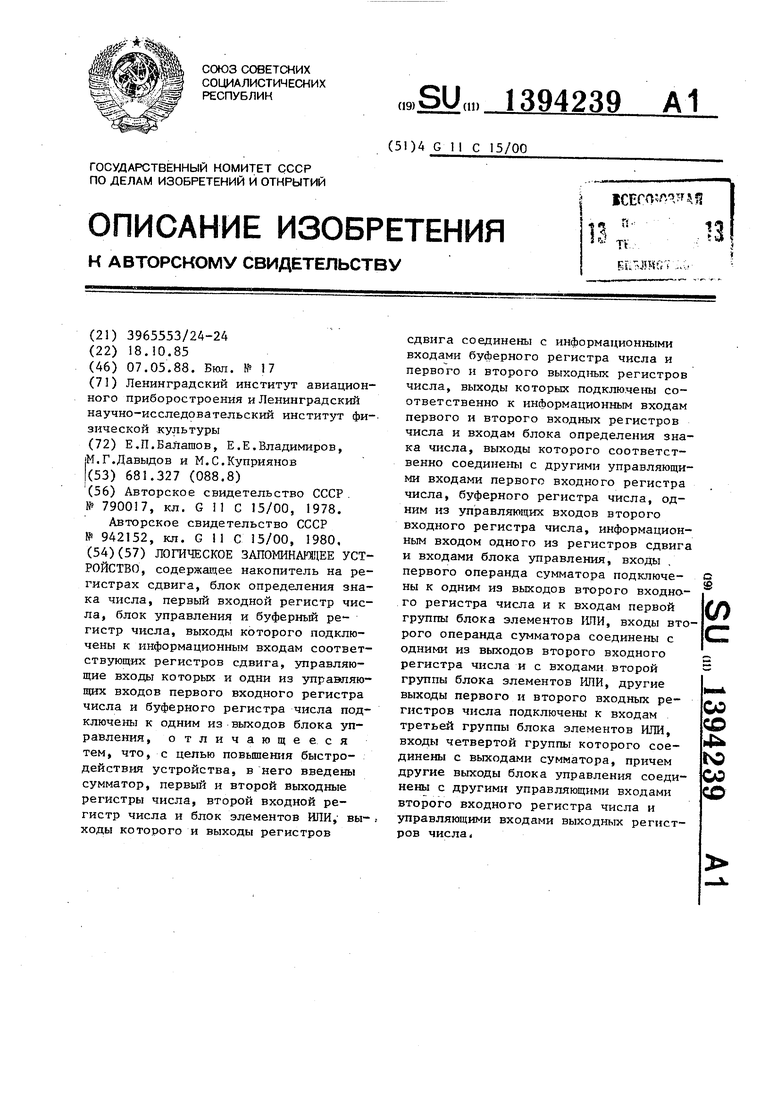

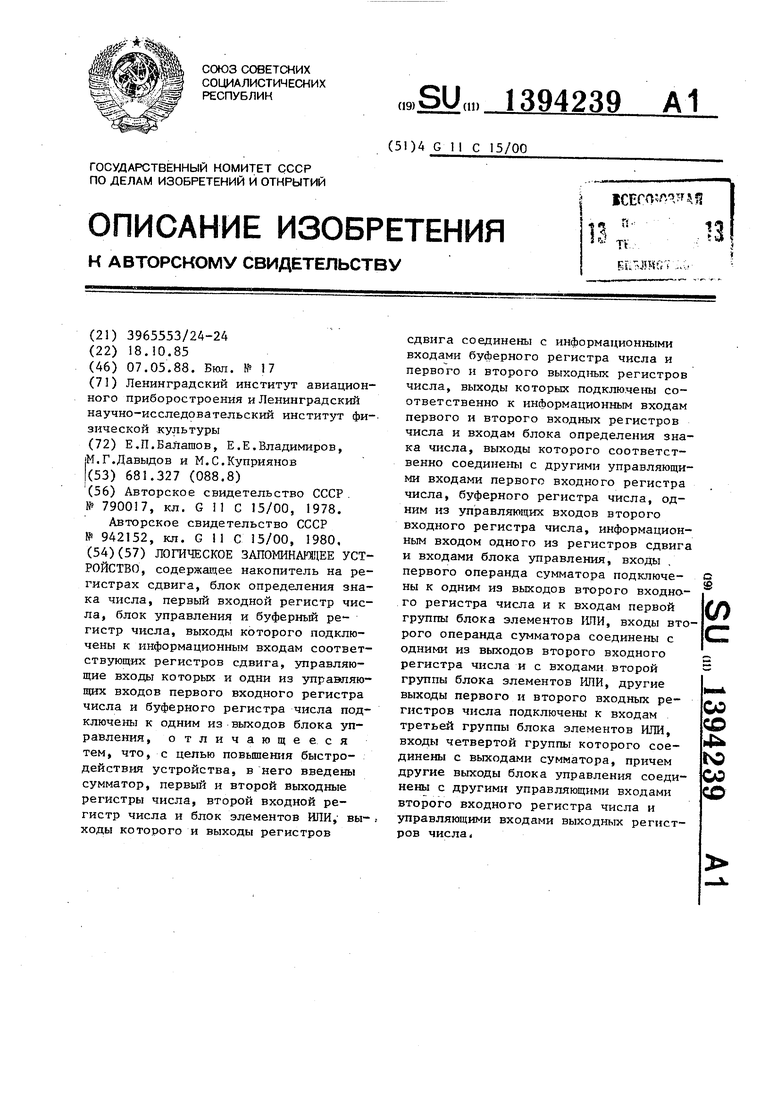

На фиг. 1 изображена структурная схема логического запоминающего устройства; на фиг. 2-4 - функциональные схемы наиболее предпочтительных вариантов выполнения блока определения знака числа, буферного регистра числа и блока управления соответственно.

Устройство (фиг.1) содержит накопитель 1 на регистрах 2 сдвига, блок 3 определения знака числа, первый 4 и второй 5 входные регистры числа, первый 6 и второй 7 выходные регистры числа, сумматор,8, блок 9 элементов ИЛИ, буферный регистр 10 числа и блок 11 управления.

Блок 3 определения знака числа (фиг. 2) содержит элемент ИСКЖЧАЮЩЕЕ ИЛИ 12, блок 13 сравнения, элементы И 14-18 и ИЛИ 19.

Регистр 10 (фиг.З) содержит п элементов И 20, п элементов И-НЕ 21 и п элементов ИЛИ 22, где п - число разрядов регистра.

Блок 11 управления (фиг. 4) содержит генератор 23 тактовых импульсов, делитель 24 частоты, элемент И 25, триггер 26, элементы И 27 и 28, элемент ИЛИ 29, триггер 30, элемент ИЛИ 31, элементы И 32 и 33, элемент ИЛИ 34, триггер 35, элементы И 36-39, триггер 40, элемент И 41, элемент ИЛИ 42, триггер 43, элементы И 44 и 45, элемент ИЛИ 46, элемент 47 задержки, элементы И 48, ИЛИ 49, триггер 50, элементы И 51-53, триггеры 54-56 и генератор 57 одиночных им- пульсов..Входы Считывание 58, Запись ,59, Первый операнд 60,,Прямой код 61, Обратньй код 62, Второй операнд 63, Обработка 64 являются управляющими входами устройства при организации функциональной структуры блока 11 управления (фиг. 4).

Логическое запоминающее устройство работает в режимах хранения информации и обработки информации.

Перед началом работы блок 11 управления устанавливает в исходное . состояние регистры 2 сдвига накопителя 1. Режимы работы устройства оп

5

0 5

0

0

5 0 j

0

5

ределянэтся управляющими сигналами на входах 58-64 блока 11 управления.

В режиме хранения информации устройство производит запись входной информации: запись первого операнда в прямом коде, запись первого операнда в обратном коде, запись второго операнда в прямом коде, запись второго операнда в обратном коде; запись выходной информации в прямом коде и в обратном коде; считывание информации.

При записи информация поступает на первый 4 и второй 5 входные регистры, затем по управляющему сигналу из блока 11 управления, из первого 4 или второго 5 входных регистров через блок ИЛИ 9 на регистр 10, в котором может произойти преобразование прямого кода числа в обратньй в зависимости от режима, установленного управляющими сигналами из блока 11 управления. С выхода регистра 10 информация поступает через информационные входы на{сопителя 1 в первые разряды регистров 2 сдвига. Регистры переключаются на режим.хранения. При поступлении следующего числа на-входные регистры 4 и 5 в регистра: 2 сдвига накопителя 1 производится сдвиг записанной информации за один разряд, и передача записываемой информации в накопитель происходит аналогично.

При записи выходной информации по сигналу сдвига из блока 11 управления код числа по цепям регенерации (lie показаны) из накопителя 1 поступает на информационные входы регистра 10. Затем-Б зависимости от режима из блока 11 управления в прямом или обратном коде информация поступает в накопитель 1 для перезаписи в регистры 2 сдвига.

При считывании информации по сигналу сдвига из блока 11 управления код числа с выходов регистра 2 сдвига выдаётся на выходы устройства и поступает по цепям регенерации на первый 6 и второй 7 вьпсодные регистры для обработки или перезаписи - на. регистр 10.

В режиме обработки информации устройство реализует сложение и вычитание входной информации, сложение и вычитание выходной информации, сложение и вычитание входной.и выходной информации, сложение и вычитание первого входного операнда и выходной информации, сложение и вычитание второго входного операнда и выходной информации.

При сложении и вычитании входной информации устройство работает следующим образом.

Информация через входы устройства поступает на информационные входы первого 4 и второго 5 входных регистров и одновременно в блок 6.

Блок 3 служит для определения знака 06(5 результата сложения и вычитания. Сигнал oig формируется при помощи знаковых разрядов oi и otj операндо А и В и сигнала |а блока сравнения.

Блок 13 сравнения формирует сигнал

I при А i в,

Р

О при А 5: в.

Алгоритм работы блока 3 приведен. в таблице.

L -±- --I-f-L

В таблице принято, что положительному числу соответствует знак, равный единице.

Знак результата сложения или вычитания определяется по формуле

Обд +ЙдОг8 р блоке 3 элемент ИСКЛЮЧАОТЛЕЕ ИЛИ. 12 производит суммирование по модулю два знаков обд и блок 13 сравне5

ю в

20

25

30

35

40

45

.

50

55

ния - операцию сравнения абсолютных величин операндов А и В. Если знаки совпадают, то на выходе элемента ИС- КЛЮЧАКвЦЕЕ ИЛИ 12 сигнал равен нулю, злементы И 17 н 18 закрыты. В зтом случае в сумматоре 8 производится обычное арифметическое сложение операндов. Результат суммирования через блок ИЛИ 9 поступает на регистр 10 и далее на разрядные входы накопителя 1 на регистрах 2 сдвига. Знак суммы из блока 3 поступает непосредственно на знаковьш вход накопителя . Если знаки Ыд и нб совпадают, то на выходе элемента ИСКЛЮЧАЩЕЕ ИЛИ 12 формируется сигнал, управляющий преобразованием кода суммы в регистре 16, и на выходе одного из элементов И 17 и 18 появляется сигнал, управляющий преобразованием кода числа в первом 4 или втором 5 входных регистрах Причем в обратный код преобразуется всегда больгаее из чисел А и В.

Операция вычитания в обратных кодах реализуется через операцию сложения с операндом обратного знака. В зтом случае после суммирования и преобразования суммы в обратный код в регистре 10 получается результат алгебраического сложения, равный А-Б|, которьй одновременно со знаком суммы записывается в соответствукхцих разрядах накопителя 1. После сигнала сдвига из блока 1I управления производится обработка следующих чисел.

При обработке выходной информации по сигналу сдвига из блока 11 управления информации из блока 11 управления информация из накопителя 1 поступает на входы устройства через первый 6 и второй 7 выходные регистры, а дальгае обрабатывается как в случае обработки входной информации.

В режиме, обработки входной и выходной информации в случае сложения первого операнда с выходной информацией на регистр 4 поступает входная информация, а на регистр - выходная информация с накопителя 1 через ре- гистр 7, и соответственно в случае сложения второго операзада с выходной информацией. Далее процесс происходит аналогично режиму обработки входной информации.

фиг.з

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1980 |

|

SU942152A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1451772A1 |

| Логическое запоминающее устройство | 1979 |

|

SU790017A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Логическое запоминающее устройство | 1974 |

|

SU507899A1 |

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Авторское свидетельство СССР | |||

| Логическое запоминающее устройство | 1979 |

|

SU790017A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Логическое запоминающее устройство | 1980 |

|

SU942152A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-05-07—Публикация

1985-10-18—Подача