СО

со со

00

со 4

Изобретение относится к электросвязи и может быть использовано в системах передачи данных для кодирования инверсного кода.

Целью изобретения является повьше ние быстродействия кодера.

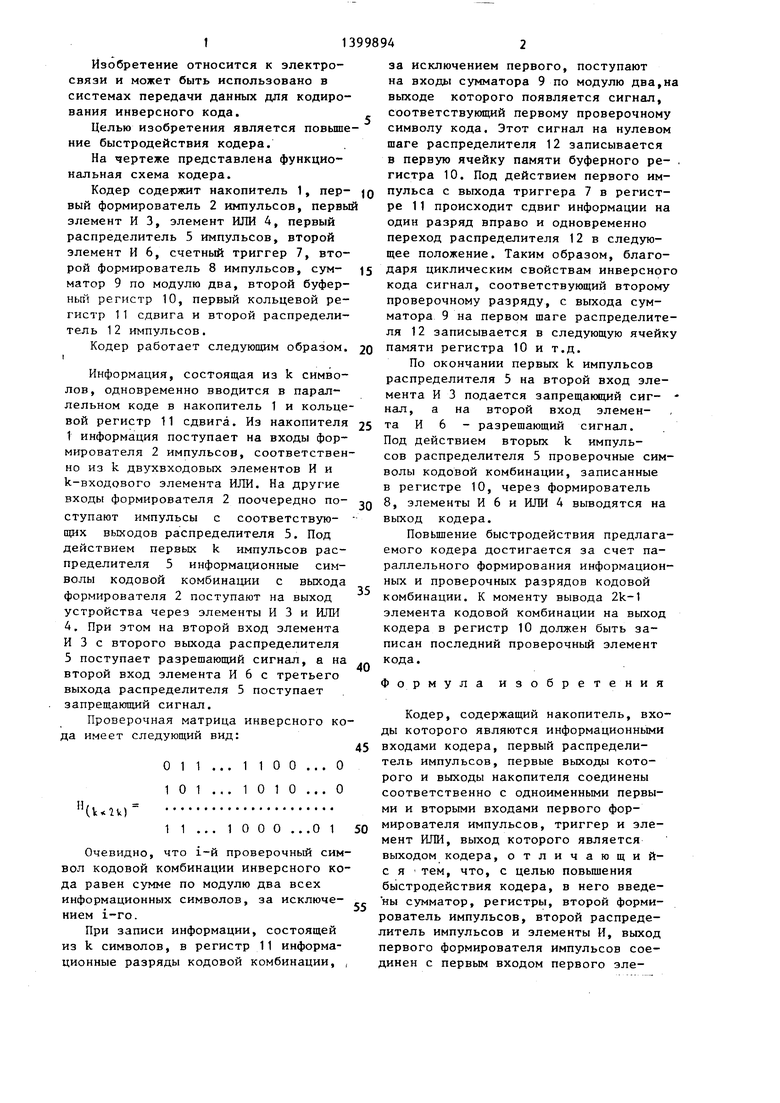

На чертеже представлена функциональная схема кодера.

Кодер содержит накопитель 1, пер- вый формирователь 2 импульсов, первы элемент И 3, элемент ИЛИ 4, первый распределитель 5 импульсов, второй элемент И 6, счетный триггер 7, второй формирователь 8 импульсов, сум- матер 9 по модулю два, второй буферный регистр 10, первый кольцевой регистр 11 сдвига и второй распределитель 12 импульсов.

Кодер работает следующим образом.

I

Информация, состоящая из k символов, одновременно вводится в параллельном коде в накопитель 1 и кольцевой регистр 11 сдвига. Из накопителя 1 информация поступает на входы формирователя 2 импульсов, соответственно из k двухвходовых элементов И и k-входового элемента ИЛИ. На другие входы формирователя 2 поочередно по- ступают импульсы с соответствую- цих выходов распределителя 5. Под действием первых k импульсов распределителя 5 информационные символы кодовой комбинации с выхода формирователя 2 поступают на выход устройства через элементы И 3 и ИЛИ 4. При этом на второй вход элемента И 3 с второго выхода распределителя 5 поступает разрешающий сигнал, а на второй вход элемента И 6 с третьего выхода распределителя 5 поступает запрещающий сигнал.

Проверочная матрица инверсного кода имеет следующий вид:

011... 1100...О

1 О 1

. 1 о 1 о ... о

н

()

1 1

1 о о о ...о 1 50

Очевидно, что i-й проверочный символ кодовой комбинации инверсного кода равен сумме по модулю два всех информационных символов, за исключением i-ro.

При записи информации, состоящей из k символов, в регистр 11 информационные разряды кодовой комбинации, ,

.

g 5

0

5 Q

5

5

0

5

за исключением первого, поступают на входы сумматора 9 по модулю два,на выходе которого появляется сигнал, соответствующий первому проверочному символу кода. Этот сигнал на нулевом шаге распределителя 12 записывается в первую ячейку памяти буферного ре- . гистра 10. Под действием первого импульса с выхода триггера 7 в регистре 11 происходит сдвиг информации на один разряд вправо и одновременно переход распределителя 12 в следующее положение. Таким образом, благодаря циклическим свойствам инверсного кода сигнал, соответствующий второму проверочному разряду, с выхода сумматора 9 на первом шаге распределителя 12 записывается в следующую ячейку памяти регистра 10 и т.д.

По окончании первых k импульсов распределителя 5 на второй вход элемента И 3 подается запрещающий сиг- - нал, а на второй вход элемента И 6 - разрешающий сигнал. Под действием вторых k импульсов распределителя 5 проверочные символы кодовой комбинации, записанные в регистре 10, через формирователь 8, элементы И 6 и ИЛИ 4 выводятся на выход кодера.

Повьппение быстродействия предлагаемого кодера достигается за счет параллельного формирования информационных и проверочных разрядов кодовой комбинации. К моменту вывода 2k-1 элемента кодовой комбинации на выход кодера в регистр 10 должен быть записан последний проверочный элемент кода.

Формула изобретения

Кодер, содержащий накопитель, входы которого являются информационными входами кодера, первый распределитель импульсов, первые выходы которого и выходы накопителя соединены соответственно с одноименньми первыми и вторыми входами первого формирователя импульсов, триггер и элемент ИЛИ, выход которого является выходом кодера, отличающий- с я тем, что, с целью повьщ1ения быстродействия кодера, в него введены сумматор, регистры, второй формирователь импульсов, второй распределитель импульсов и элементы И, выход первого формирователя импульсов соединен с первым входом первого эле313998944

мента И, выход которого соединен содноименными управляющими входами первым входом элемента ИЛИ входывторого регистра, выходы которого триггера и первого распределителясоединены с одноименными первыми вхо- импульсов объединены и являются син-дами второго формирователя импульсов, хронизирующим .входом кодера, выходвторые входы которого подключены к триггера соединен с тактовым входомодноименным первым выходам первого первого регистра и входом второго рас-распределителя импульсов, выход вто- пределителя импульсов, информацион-рого формирователя импульсов сое- ные входы первого регистра подпюче- jgдинен с первым входом второго эле- ны к одноименньи информационным вхо-мента И, выход которого соединен с дам кодера, выходы первого регистравторым входом элемента ИЛИ, второй и соединены с одноименными входамитретий выходы первого распределителя сумматора, выходы сумматора и второ-импульсов соединены с вторыми входа- го распределителя импульсов соединены ми соответственно первого и второго соответственно с информационным иэлементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер | 1990 |

|

SU1783623A1 |

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| АДАПТИВНЫЙ КОДЕР ГИПЕРКОДА РАЗМЕРНОСТИ 3D | 2011 |

|

RU2480918C1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Кодер балансного кода 3B2Q | 1987 |

|

SU1531223A1 |

| Устройство для кодирования цифровой информации циклическими кодами | 1986 |

|

SU1336255A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

Изобретение относится к электросвязи и может использоваться в системах передачи информации для кодирования инверсного кода. Изобретение позволяет повысить быстродействие кодера за Счет параллельного формирования информационных и проверочных разрядов кодовой комбинации. Кодер содержит накопитель 1, формирователи 2, 8 импульсов, элементы И 3,6, элемент ИЛИ 4, распределители 5, 12 импульсов, триггер 7, сумматор 9 и регистры 10, 11. 1 ил.

| Блейхут Р | |||

| Теория и практика кодов, контролирующих ошибки | |||

| М.: Мир, 1986, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР | |||

| Кодирующее устройство для инверсного кода | 1974 |

|

SU540391A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-05-30—Публикация

1987-01-04—Подача