4;:ь

о ел

Изобретение относится к технике физического эксперимента и может быт использовано в ядерной физике нри разработке быстродействующих аналого-цифровых преобразователей (АЦП), например, для измерения амплитуды импульсов в ионизационных спектрометрах на основе дрейфовых камер.

Целью изобретения является повышение точности преобразования.

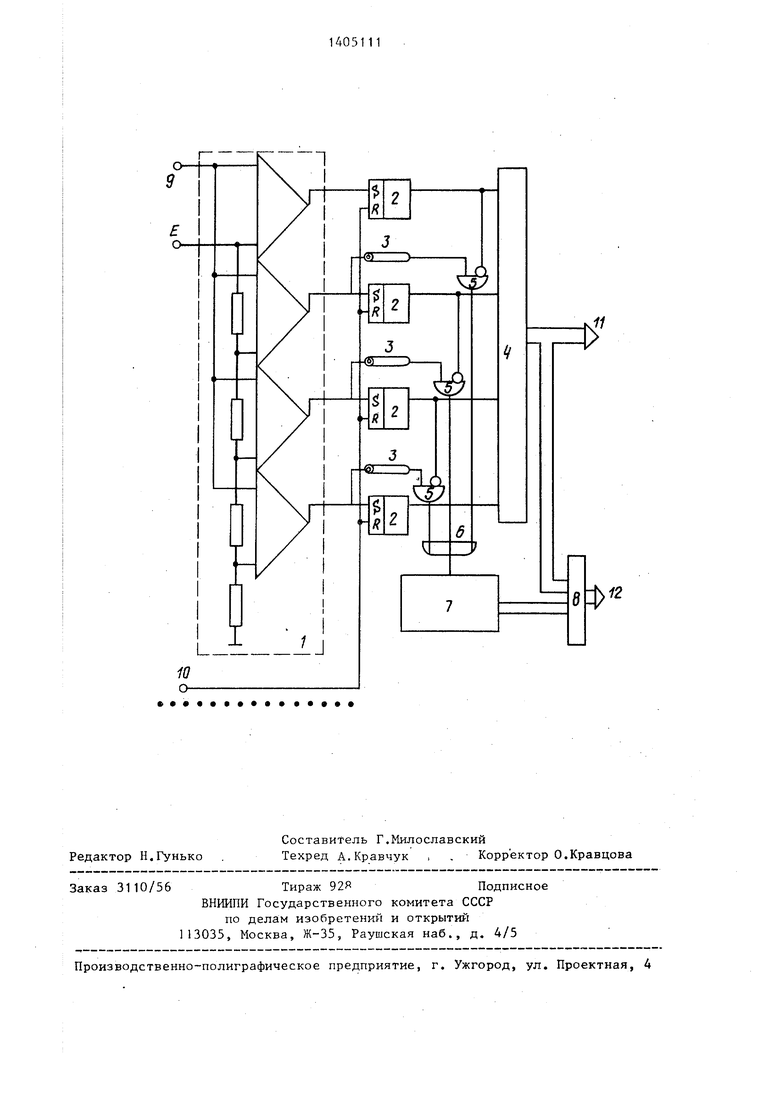

На чертеже представлена функциональная схема устройства для реализации данного способа.

Сущность способа преобразования коротких импульсов известной формы в код заключается в том, что с помощью набора эталонных уровней параллельного АЦП производится предварительное (грубое) измерение амплитуды входного сигнала. При этом определяются старшие разряды выходного кода. По результатам работы параллельного АЦП определяется номер п самого верхнего достигнутого эталонного уровня, относительно которого осуществляется измерение длительности входного импульса /ut на этом п-м уровне. При этом превышение амплитуды импульса над п-м эталонным уровнем и соответствующие ему младшие разряды выходного кода находят по формуле (п, &t), исходя из заранее известной формы входного сигнала. Цри использовании данного способа в ядер ной электронике известность формы I входного сигнала определяется тем, I что на АЦП сигналы поступают со спек рометрического усилителя, где осу- ществляется их формирование.

В частном случае для входного сигнала, имеющего форму равнобедренного треугольника, зависимость ЛЬ f

(п, ut) выглядит как лh 2 nh ---

где h - величина одного уровня квантования, Т - длительность входного сигнала в основании„

Для гауссовского сигнала эту зависимость можно получить разложением гауссовской кривой в ряд Тейлора около.точки, соответствующей максимуму кривой:

uh п-ьГ2(-) -12 (-т|)+...55

где G - стандартное отклонение гауссовской кривой.

5

0

5

0

5

0

5

O

5

Устройство для реализации данного способа преобразования содержит па- раллельньй АЦП 1, два RS-триггера 2, линии 3 задержки, шифратор 4, элементы 5- антисовпадения, элемент Ш1И 6, хронотрон 7 и постоянное запоминающее устройство (ПЗУ) 8.

При этом вход АЦП 1 соединен с входом 9 устройства, шина 10 Сброс устройства соединена с Рч.-входами RS-триггеров 2, выходы шифратора 4 являются первой группой выходов 11 устройства, а выходы ПЗУ 8 - второй группой выходов 12 устройства.

Устройство работает следующим образом.

Пусть на вход 9 устройства поступил входной импульс, например, треугольной формы. На начальном этапе работы устройства срабатывает параллельный АПП 1, это приведет к тому, что на определенных выходах его в зависимости от амплитуды входного сигнала появится код его старших разрядов. Этот код приведет к срабатыванию соответствующих RS-триггеров 2, предварительно по шине 10 Сброс установленных в нулевое состояние. По состоянию RS-триггеров 2, соединенных с входами шифратор а 4, на. первой группе выходов 11 устройства формируется код старших разрядов амплитуды входного сигнала. При этом независимо от значений уровней напряжения на выходах параллельного АЦП 1 информация в RS-триггерах 2 хранится в течение всего цикла измерения и умножается только по следукщему сигналу Сброс по шине 10 Сброс устройства.

Длительность выходного сигнала с самого старшего сработавшего выхода параллельного АЦП 1 соответствует длительности основания остатка входного импульса. Этот сигнал проходит через соответствующую линию 3 задержки и элемент 5 антисовпадения на элемент ИЛИ 6. Линии 3 задержки включены для того, чтобы исключить прохождение на элемент ИЛИ 6 коротких сигналов, которые могут возникнуть вследствие задержки срабатывания в схемах параллельного АЦП 1. При этом длительность временной задержки для самого младшего выхода параллельного АЦП 1 необходимо выбрать порядка половины времени нарастания входного импульса, для бо.лее старших выходов

31

параллельного АЦП 1 она постепешк) уменьшается и для самого старшсг о выхода параллельного АЦП 1 ее можно выбрать в п раз меньше, где п - число выходов параллельного АЦП 1.

Таким образом, длительность сигнала на выходе элемента ИЛИ 6 точно соответствует длительности основания остатка. Для входных импульсов с ту- пой вершиной, например для гауссов- ской формы, лучше измерять длительность срабатывания параллельного АЦП 1 не на самом верхнем уровне для данного импульса, а на втором, третьем уровне сверху. При этом точность измерения будет вьш1е.

В качестве измерителя временного интервала в устройстве использован хронотрон 7. ПЗУ 8 включено для кор- рекции нелинейности, которая возникает КЗ-за того, что длительность остатка от амплитуды зависит нелинейно. На первую группу входов ПЗУ Ь поступает код старших разрядов с вы- хода шифратора 4, на вторую группу входов - код измерения длительности остатка с хронотрона 7, при этом на выходе ПЗУ 8, а следовательно, и на второй группе выходов 12 устройства формируется код младших разрядов амплитуды входного сигнала.

Формула изобретения 1, Способ преобразования коротких импульсов известной формы в код, включающий сравнение амплитуды импульса с набором эталонных уровней, по результатам которого определяют номер п верхнего достигнутого уровня и соответствующие ему старшие разряды выходного кода, отличающий

Q

n 5

0

5

0

114

с я тем, что, с целью повышения точности преобразования, одновременно с определе нием старших разрядов измеряют длительность входного импульса дс на п-м уровне, а превышение амплитуды импульса Л h над п-м уровнем и соответствующие ему младшие разряды выходного кода вычисляют, исходя из известной формы входного импульса

2. Устройство для преобразования коротких импульсов известной формы в код, содержащее п компараторов, первые входы которых объединены и подключены к шине входного сигнала, а вторые входы - к соответствующим, резисторам делителя напряжения, подключенного к шине опорного напряжения, выходы компараторов подключены соответственно к S-входам RS-триггеров, число которых равно п, R-входы RS- триггеров объединены и подключены к шине Сброс, а единичные выходы соединены с соответствующими входами шифратора, выходы которого соединены с шинами старших разрядов устройства, S-входы RS-триггеров, кроме первого, соединены через линии задержки соответственно с прямыми входами (п-1) элементов антисовпадения, инверсные входы которых соединены соответственно с единичными выходами RS-триггеров, кроме п-го, выходы элементов антисовпадения соединены с входами элемента ИЛИ, выход которого соединен с входом хронотрона, выходы которого подключены к одной группе входов постоянного запоминающего устройства, другая группа входов которого соединена с выходами шифратора, а выходы подключены к шинам младших разрядов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Устройство для регистрации аналогового процесса | 1989 |

|

SU1774379A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| Способ преобразования максимума амплитуды электрического импульса в цифровую форму и устройство для его осуществления | 1986 |

|

SU1387194A1 |

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Устройство сигнатурной проверки аналого-цифровых преобразователей | 1979 |

|

SU790293A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

Изобретение относится к технике физического эксперимента и может быть использовано в ядерной физике при разработке быстродействующих аналого-цифровых преобразователей (АЦП), например, для измерения амплитуды импульсов в ионизационных спектрометрах на основе дрейфовых камер. Целью изобретения является повышение точности преобразования. Способ преобразования коротких импульсов известной формы в код заключается в том, что одновременно с определением старших разрядов измеряют длительность преобразуемого импульса лt на верхнем п-м эталонном уровне и находят пре- вьпиение амплитуды импульса uh над п-м эталонным уровнем и соответствующие ему младшие разряды выходного кода по формуле ЛЬ .f(n, ut). Устройство для реализации данного способа содержит параллельньй АЦП, два RS-триггера, шифратор, элементы антисовпадения, элемент ИЛИ, линии задержки, хронотрон и постоянное запоминающее устройство. 2 с.п. ф-лы, 1 ил. с (Л

| РЫБОЗАЩИТНОЕ СООРУЖЕНИЕ | 2006 |

|

RU2310036C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Устройство для двухступенчатогоАНАлОгО-цифРОВОгО пРЕОбРАзОВАТЕля | 1977 |

|

SU809543A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-23—Публикация

1982-08-19—Подача