1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при построении БИС ОЗУ и ЗУ на их основе со встроенными средствами проверки работоспособности.

Целью изобретения является упрощение устройства.

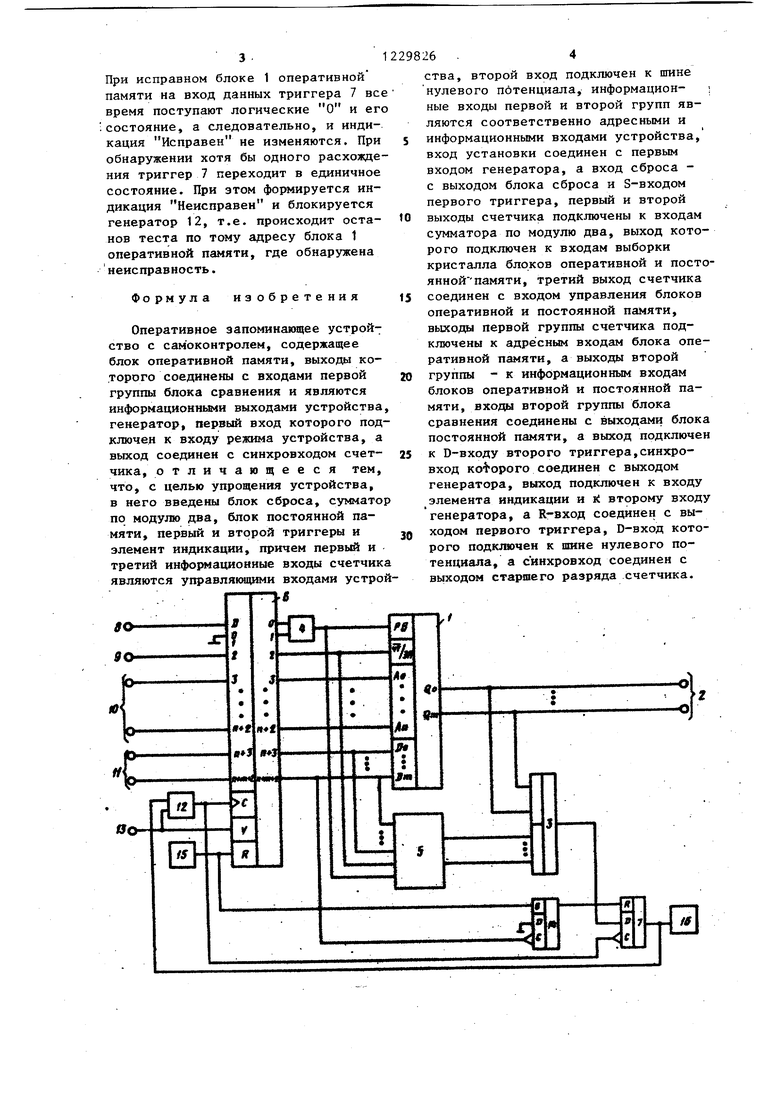

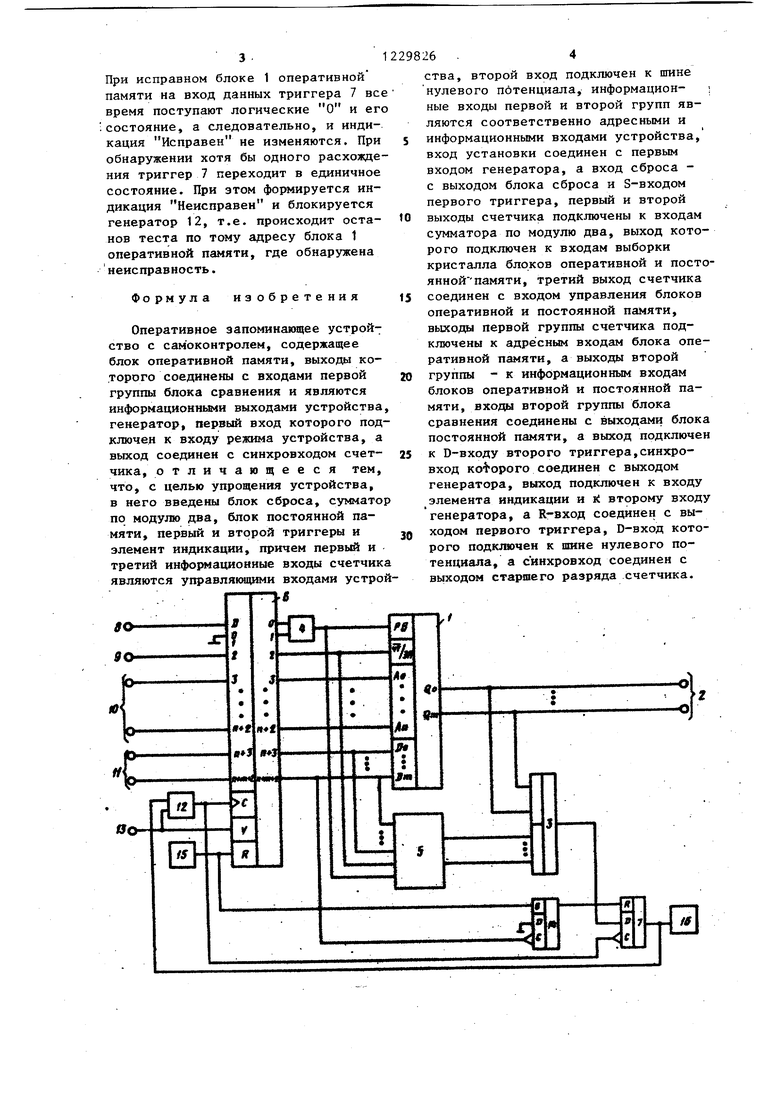

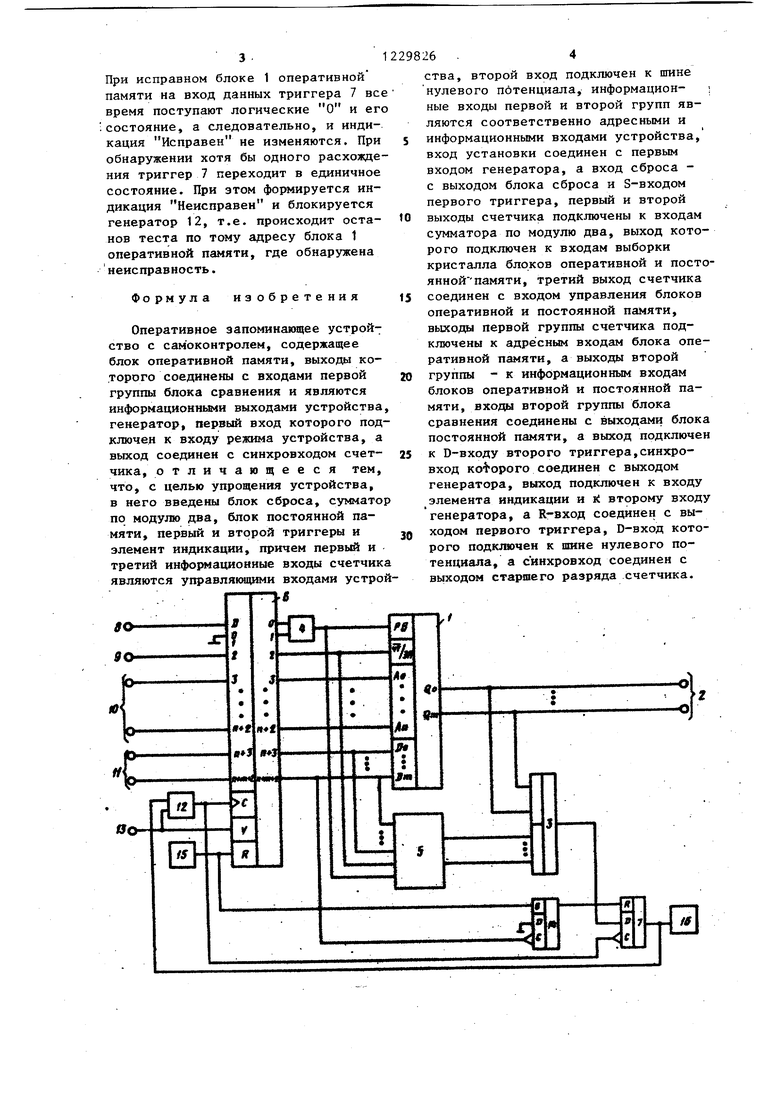

На чертеже представлена схема one ративного запоминающего устройства с самоконтролем.

Устройство содержит блок 1 оперативной памяти, информационные выходы 2, блок 3 сравнения, сумматор 4 по модулю-два, блок 5 постоянной памяти, счетчик 6, второй триггер 7, управляющие входы 8 и 9, адресные входы 10, информационные входы 11, генератор 12, вход 13 режима, первый триггер 14, блок 15 сброса и элемент 16 индикации.

Блок 15 сброса (например, RC-цепь обеспечивает сигналы начальной ус- , тановки при включении питания.

Устройство работает следующим образом.

1

При подаче питания импульс с блока 15 сброса устанавливает счетчик 6 в ноль и триггер 14 в единицу. Последнее вызывает сброс триггера 7 и |формирование индикации Исправно. Дальнейшая работа определяется сигналом на входе 13 режима Контроль/работа. В режиме Работа логическая 1 на входе 13 режима блокирует генератор 12 и определяет работу счетчика 6 в режиме асинхронной установки по входам данных. Таким образом, сигналы РВ, ЧТ/ЗП (чертеж), адреса и данные поступают с входов счетчика 6 на соответствующие его выходы, что обеспечивает работу блока 1 оперативной памяти в обычном режиме. Поскольку на входы сумматора 4 по модулю два поступают сигналы РВ и логический О, то его выход повторяет сигнал Р.В. Так как генератор 12 заблокирован, то состояние триггера

7и индикации остается неизменным.

8режиме Контроль логический О на входе 13 режима разрешает работу генератора и определяет работу счетчика 6 в режиме непрерывного пересчета (генератор 12 работает в автоколебательном режиме). При этом состояние счетчика 6 изменяется незави- .симо сигналов на его входах дан5

О

15

229826 .2

ных. Поскольку стимуляция адресных входов блока 1 памяти осуществляется разрядами счетчика 6, начиная с третьего,то длительность обращения к каждому адресу составляет 8 тактов синхросигнала генератора 12 (состояние счетчика изменяется по переднему фронту синхроимпульса). В течение первых четырех тактов осзлцествляется операция Чтение, в течение вторых - Запись. Внутрь каждой четырехтактной операции вложен двухтактный сигнал РВ (обеспечивается сумматором 4 по модулю два), который принимает активный уровень при неизменных остальных сигналах, поданных на блок 1 оперативной памяти (тем самым достигается корректная временная диаграмма). Проход адресного пространства осуществляется при неизменных входных данных, после чего они изменяются и начинается новый проход и т.д.

Подобная последовательность операций характерна для теста Марш при полном переборе входных данных. Поскольку при подаче питания ячейки блока 1 оперативной памяти ориентируются произвольно, то за время первого выполнения теста контроль выходных реакций не производится (триггер 14 сохраняет единичное сос20

25

30

сигнала на входе сброса триггера 7). Завершение цикла тестирования вызывает возврат всех разрядов счетчика 6 в нулевое состояние. При зтом задний фронт на выходе его (п+т+2)-го разряда переводит триггер 14 в нулевое состояние, разрешая работу триггера 7 по синхровходу. Таким образом, при втором и последующих выполнениях теста триггера 7 по заднему фронту каждого синхроимпульса генератор 12 (подача стимулирующего воздействия и контроль выходной реакции разнесены во времени) осуществляет регистрацию сигнала с выхода блока 3 сравнения. Сигнал сравнения равен нулю при совпадении данных на первых входах блока 3 сравнения (реакция блока 1 оперативной памяти) с данными на вторых его входах (эталонная реакция) и равен единице при их несовпадении.

Эталонная реакция формируется блоком 5 постоянной памяти на основе сигналов РВ, ЧТ/ЗП и Do,...,D, поданных на блок 1 оперативной памяти.

3

При исправном блоке 1 оперативной памяти на вход данных триггера 7 все время поступают логические О и его : состояние, а следовательно, и индикация Исправен не изменяются. При обнаружении хотя бы одного расхозкде- ния триггер 7 переходит в единичное состояние. При этом формируется индикация Неисправен и блокируется генератор 12, т.е. происходит останов теста по тому адресу блока 1 оперативной памяти, где обнаружена неисправность.

Формула изобретения

Оперативное запоминаищее устройство с самоконтролем, содержащее блок оперативной памяти, выходы ко- .торого соединены с входами первой группы блока сравнения и являются информационными выходами устройства, генератор, первый вход которого подключен к входу режима устройства, а выход соединен с синхровходом счетчика, отличающееся тем, что, с целью упрощения устройства, в него введены блок сброса, сумматор по модулю два, блок постоянной памяти, первый и второй триггеры и элемент индикации, причем первый и третий инфо1 4ационные входы счетчика являются управлякйцими входами устрой

229826 .4

ства, второй вход подключен к шине нулевого потенциала, информацион- ; ные входы первой и второй групп являются соответственно адресными и 5 информационными входами устройства, вход установки соединен с первым входом генератора, а вход сброса - с выходом блока сброса и S-входом первого триггера, первый и второй

10 выходы счетчика подключены к входам сумматора по модулю два, выход которого подключен к входам выборки кристалла блоков оперативной и постоянной памяти, третий выход счетчика

15 соединен с входом управления блоков оперативной и постоянной памяти, выходы первой группы счетчика подключены к адресным входам блока оперативной памяти, а выходы второй

20 группы - к информационньлм входам блоков оперативной и постоянной памяти, входы второй группы блока сравнения соединены с выходами блока постоянной памяти, а выход подключен

25 к D-входу второго триггера,синхро- вход которого соединен с выходом генератора, выход подключен к входу элемента индикации и i второму входу генератора, а R-вход соединен с вы30 ходом первого триггера, D-вход которого подклвочен к шине нулевого потенциала, а синхровход соединен с выходом старшего разряда счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1325571A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1406640A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1647655A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1413676A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля оперативной памяти тестом Марш с двоично-нарастающим адресным шагом | 1986 |

|

SU1532978A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1317486A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1277216A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при построении БИС ОЗУ и ЗУ на их основе с встроенными средствами проверки работоспособности. Целью изобретения является упрощение устройства. Устройство содержит блоки оперативной и постоянной памяти,генератор, блок сброса, первый и второй триггеры, сумматор по модулю два, счетчик, блок сравнения и элемент индикации. В устройстве обеспечивается режим встроенного контроля блока оперативной памяти на тесте Мают, причем упрощение достигается за счет использования счетчика в режиме счета при тестировании и в режиме регистра при внешних обращениях к устройству. Зталонные данные в режиме контроля формируются блоком постоянной памяти. 1 ил. (Л N9 Ю СО 00 ю dd

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1040526A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Электронная техника | |||

| Микроэлектроника, сер | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Счетная таблица | 1919 |

|

SU104A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ,(54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ | |||

Авторы

Даты

1986-05-07—Публикация

1984-08-21—Подача