Изобретение относится к вычислительной технике и ыожет быть использовано при построении запоминающих устройств с самоконтролемо

Цель изобретения - повышение быстродействия устройства при самоконтроле.

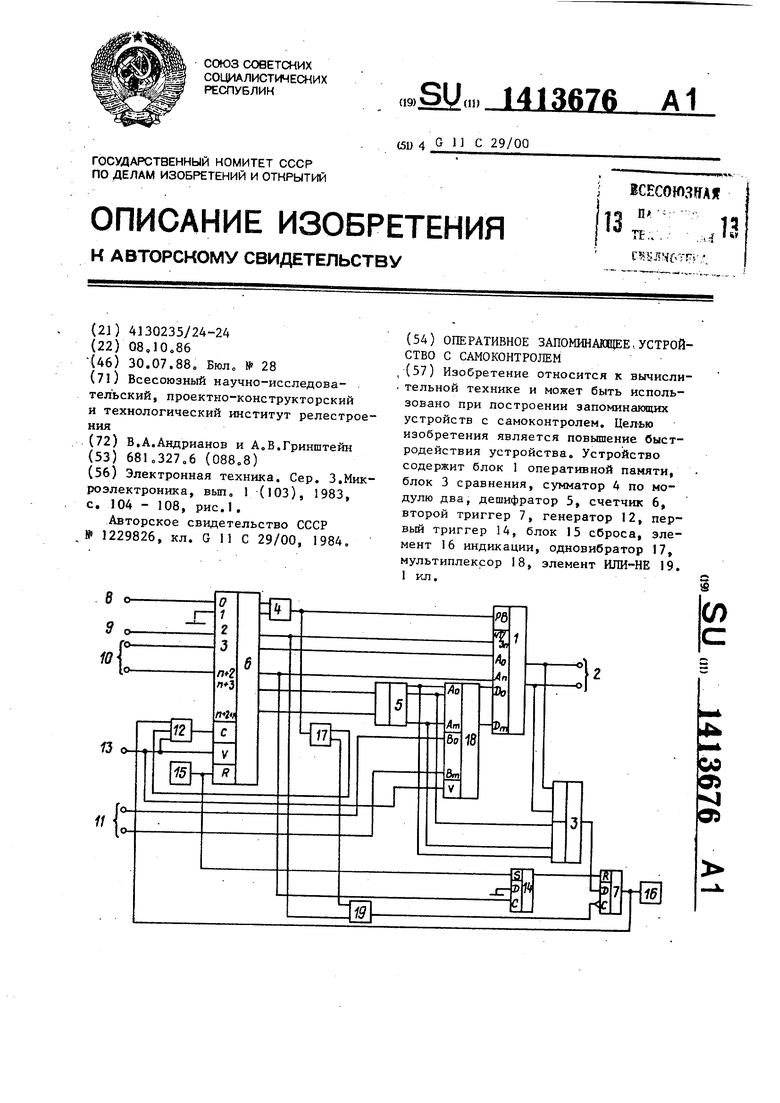

На чертеже показана структурная схема предлагаемого устройства.

Операт1-тное запоминающее устройство с самоконтролем содержит блок 1 оперативной памяти, выходы 2.данных устройства, блок 3 сравнения, сумматор 4 по модулю два дешифратор 5, счетчик 6, второй триггер 7,, вход 8 Разрешение выборки устройства,вход 9 Чтение/запись, адресные входы 10 входы 11 данныхJ генератор 12, вход 13 Контроль/работа устройств а,, пер™ вый триггер 14, блок 15 сброса, элемент 16 индикации, одновибратор 17, мультиплексор 18, элемент ИЛИ-НЕ 19,.

Блок 1 оперативной памяти построен на БИС ОЗУ- и имеет организацию N X М, где N число адресов, а М - разрядность слова данных

Известно, что алгоритм теста МАРШ для ОЗУ с организацией N х 1 закшоча ется в двух проходах адресного прост рапствао При этом в течение первого проходи по каждому ар,ресу выполняются операции Чтение Ij Запись О,, а при втором проходе Чтение О, Запись 1,.Поскольку выходная реакция ОЗУ определена таблицей истинное ти,, а входные сигналы данных в течение как первого, так и второго проходов адресов поддерживаются неизмен ными (о и 1 соответственно) для обес печения требуемых операций Запись О и Запись 1 % то на основе сигналов Разрешение выборки (РВ), ЧТ/ЗП и Dgx в любой момент времени можно указать вьЕкодной сигнал исправ ного ОЗУ, Например, при ЧТ/ЗП О и имеет место выполнение опера1.щи Разрешение () чте НИН (ЧТ/ЗП 0) нуля (Dg,.( l) и, следо вательно;, выходной сигнал исправного ОЗУ должен быть О (прямой выход)«При многоразрядном слове данных {Мх- 1) и стимуляции входов данных оперативной памяти выходами дешифратора управляемого разрядами счетчика, следующими за. разрядами, стимулирующими адреса оперативной памяти (диагональ ный перебор данных) один проход тес

та состоит из 2 . М проходов адресов , Здесь при контроле каждого разряда имеет место избыточность, заключающаяся в дополнительных операди- ях Чтение 1, Запись 1 (при активном уровне сигнала на выходе дешифратора - логический о) во всех не первых проходах адресов после смены входных данных в разряде.

При этом информация, считываемая из исправного блока 1 оперативной памяти, идентична информации, находившейся на его входах данйых в предыдущем проходе адресов, и может быть получена циклическим сдвигом информации, имеющейся на входах 20

25

30

35

оперативной памяти в текущем

40

45

50

55

ка

проходе адресов. Например, при состоянии входов Dpcoo Dm блока оперативной памяти 1 0. 1 ,,,1 циклическим сдвигом формируется эталон- ная - 1 о.. 1 0, , что соответствует Чтению О по старшему разряду и Чтению 1 по остальным разрядам „ Выходы дещифратора 5 соединены с цнклическ лм сдвигом в сторону младших выходов на входы блока 3 сравнения Младший выход дешифратора 5 соединен со старщим входом второй группы входов блока 3 сравнения, а все остальные выходы дешифратора соединены со сдвигом в сторону младших выходов на оставшиеся входы 3 сравнения.

Одновибратор 17 осуществляет тор- можение генератора 12 на время,необходимое для вы,борки блока 1 оперативной памяти. Это сделано потому, что частота генератора 3 2 выбрана такой, при которой длительность такта генератора 12 определяется только временем полного перекл}очения разрядов счетчика 6. При этом время между ближайшими сигналами Разрешение выборки сводится к минимуму. Запись во второй Tpvirrep 7 результата сравнения выходных и зталонньк реакг ий блока 1 оперативной памяти, формируемого блоком 3 сравнения;, производится только при наличии активного уровня сигнала Разрешение выборки в режиме Чтение, т,е„ контроль ведется только по считьшаемой информации.

Генератор 12 формирует синхроимпульсы для счетчика 6 при самоконтроле. Первый триггер 14 служит для

блокировки работы второго триггера 7 при первом проходе адресов Это связано с тем, что при подаче питания оперативная память ориентируется произвольно и может иметь на выходе неверную информацию. После первого прохода адресов все ячейки памяти устанавливаются в однозначное состояние

Устройство работает следующим образом.

При подаче питания импульс с блока 15 сброса устанавливает счетчик 6 в d и триггер 14 в , Последнее вызывает сброс триггера 7 и формирование индикации Исправно.Дальнейшая работа устройства определяется сигналом на входе 13 Контроль/работа. В режиме Работа логическая 1 на входе 13 блокирует генератор 12, определяет работу счетчика 6 в режиме асинхронной установки по входам данных, а работу мультиплексора 18 - в режиме передачи информации с второй группы входов Bo.,oBj. Таким образом, сигналы РВ, ЧТ/ЗП и адреса через счетчик 6, а данные через мультиплексор 18 поступают на соответствующие входы блока 1 оперативной памяти, что обеспечивает его работу в обычном режиме (поскольку на входы сумматора 4 по модулю два поступают сигналы РБ и логический о, то его выход повторяет сигнал РВ)о Так как генератор 12 заблокирован, то состояние второго триггера 7 и элемента 16 индикации остается неизменным. В режиме Контроль логический О на входе 13 разрешает ра- боту генератора 12, определяет работу счетчика 6 в режиме непрерывного пересчета (генератор 12 работает в автоколебательном режиме) и работу мультиплексора 18 в режиме передачи с входов . При этом состояни счетчика 6 не зависит от сигналов н его входах данных, а состояние выходов мультиплексора 18 не зависит от состояния сигргалов на его входах В-..,В . Так как стимуляция адресны

и ш

входов блока 1 оперативной памяти осуществляется разрядами счетчика 6 начиная с 3-го, то длительность обр щения к блоку 1 оперативной памяти составляет 8 тактов синхросигнала генератора 12 (состояние счетчика 6 изменяется по переднему фронту синхросигнала). В течение первых четырех тактов осьтцествляется операция Чтение, в течение вторых - Запись

Внутрь каждой четырехтактной операции вложен двухтактный сигнал РВ (вырабатывается суь5матором 4 по модулю два), который вырабатывает активный уровень при неизменных остальных сигнешах,

поданных на блок оперативной памяти (тем самым достигается корректная временная диаграмма).

При появлении активного уровня сигнала РВ одновибратор 17 вырабатывает импульс, в течение которого осуществляется блокировка генератора 12, а следовательно, и счетчика 6, , происходит увеличение длительности данного такта генератора, отведенпого на выполнение операции.Чтение или Запись на время импульса одно- вибратора, которое выбирается не менее времени выборки оперативной памяти Увеличение остальных трех тактов генератора 12 при отработке четырехтактных операций Запись или Чтение не происходит.

Стимуляция входов данных блока 1

оперативной памяти осуществляется через мультиплексор 18 депшфрато ром 5 f управляемым второй группой выходов счетчика 6, что соответствует тестированию блока 1 операт1шной пй-мяти по алгоритму теста МАРШ с диагональным перебором данных Поскольку при каждом проходе адресов эталон считьшаемой из блока 1 оперативной памяти информации соответствует состоянию выходов дешифратора 5 в предыдущем проходе адресов, то эталон формируется подачей циклически сдвинутых в сторону младших выходов дешифратора 5 на блок 3 сравнения. Так

как при подаче питания ячейки блока 1 оперативной памяти устанавливаются в произвольное состояние, то за время первого прохода адресов контроль выходных реакций блока 1 оперативной памяти не производится (первый триггер 14 сохраняет единичное состояние удерживая второй триггер 7 в сброшенном состоянии) Завершение первого прохода адресов вызывает возврат разрядов счетчика 6 в состояние О, При этом задний фронт на выходе его (п+2)-го разряда переводит первый триггер -14 в состояние О, разрешая работу второго тригге

pa 7 по входу синхронизации. На вход синхронизации второго триггера 7 че- Ьез элемент ИЛИ-НЕ 19, управляемый сигналом Чтение/запись, поступают импульсы с инверсного вькода одновиб- ратора 17. При выполняемой операции Чтение раэрашается прохождение импульсов с одновибратора 17 через элемент 19 на вход синхронизации Второго триггера 7, а при операции Запись - блокируется, что обеспечивает запись во второй триггер 7 Сигнала с выхода блока 3 сравнения только при считьшании информации из блока оперативной памяти. Сигнал Сравнения равен О при совпадении данных на первой группе входов блока 3 сравнения (информация, считываемая из блока Ь оперативной памяти) с дан- Йымн на второй группе его входов эталонная реакция) и равен 1 при их НесовпадениИе

: При исправном блоке 1 оперативной памяти на Б-вход второго триггера 7 поступают нули, и его состояние, |а следовательно, и состояние элемен- jra 16 индикации не изменяются. При обнаружении хотя бы одного расхождения триггер 7 устанавливается в состояние логической , При этом формируется индикации, Неисправен К блокируется генератор 12, т„е. происходит останов теста по адресу блока 1 оперативной памяти, где обнаружена неисправность о

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее блок оперативной памяти, выходы которого соединены с входами первой группы блока сравнения и являются информационными выходами устройства, генератор, первый вход которого подключен к входу Контроль/работа устройства, а выход соединен с входом синхронизации счетчика, причем нулевой и второй разряды информационного входа счетчика являются входами Разрешение выборки и Чтение/запись устройства соответственно, первый разряд информационного входа счетчика подключен

к шине нулевого потенциала, разряды с третьего по (п+2) информационных входов счетчика являются адресными входами устройства, вход установки счетчика соединен с первым входом генератора и входом установки в единичное состояние первого триггера и, является входом Сброс устройства,

0 первый и второй выходы нулевого и первого разрядов счетчика подключены к входам сумматора по модулю два, выход которого подключен к входу выборки кристалла блока оперативной

5 памяти, выходы разрядов с третьего по (п+2) счетчика подключены к адресным входам блока оперативной памяти, выход блока сравнения подключен к информационному входу второго тригге0 ра, выход которого соединен с вторым входом генератора и является индикаторным выходом устройства, а вход установки в О второго триггера соединен с выходом первого триггера,

5 отличающееся тем, что, с целью повьш1ения быстродействия при самоконтроле, в него введены дешифратор, одновибратор, элемент ИЛИ-НЕ, мультиплексор, причем входы дешифра0 тора соединены с выходами разрядов с (п+З) по (п + 2 + k) счетчика, выходы дешифратора подключены к информационным входам первой группы мультиплексора и к соответствующим входам второй группы блока сравнения, информационные входы второй группы мультиплексора являются входами данных устройства, выходы мультиплексора подключены к входам данных блока

Q оперативной памяти, управляющий вход мультиплексора соединен с входом Контроль/работа устройства, вход одновибратора соединен с выходом сумматора по модулю два, прямой выход

с одновибратора соединен с третьим

входом генератора, инверсный выход . одновибратора соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом третьего разряда счетчика, выход элемента ИПИ-НЕ подключен к входу синхронизации второго триггера, вход синхронизации первого триггера подключен к выходу (п+2) разряда счетчика.

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1647655A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1325571A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1406640A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для контроля оперативной памяти тестом Марш с двоично-нарастающим адресным шагом | 1986 |

|

SU1532978A1 |

| Электронная техника | |||

| Сер, 3.Микроэлектроника, вып | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Счетная таблица | 1919 |

|

SU104A1 |

| Оперативное запоминающее устройство с самоконтролем | 1984 |

|

SU1229826A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-30—Публикация

1986-10-08—Подача