11А

Изобретение относится к вычисли тельной технике и может быть использовано в устройствах ЦВМ последовательного действия.

Целью изобретения является расширение функциональных возможностей за счет возможности умножения в допол нительных кодах.

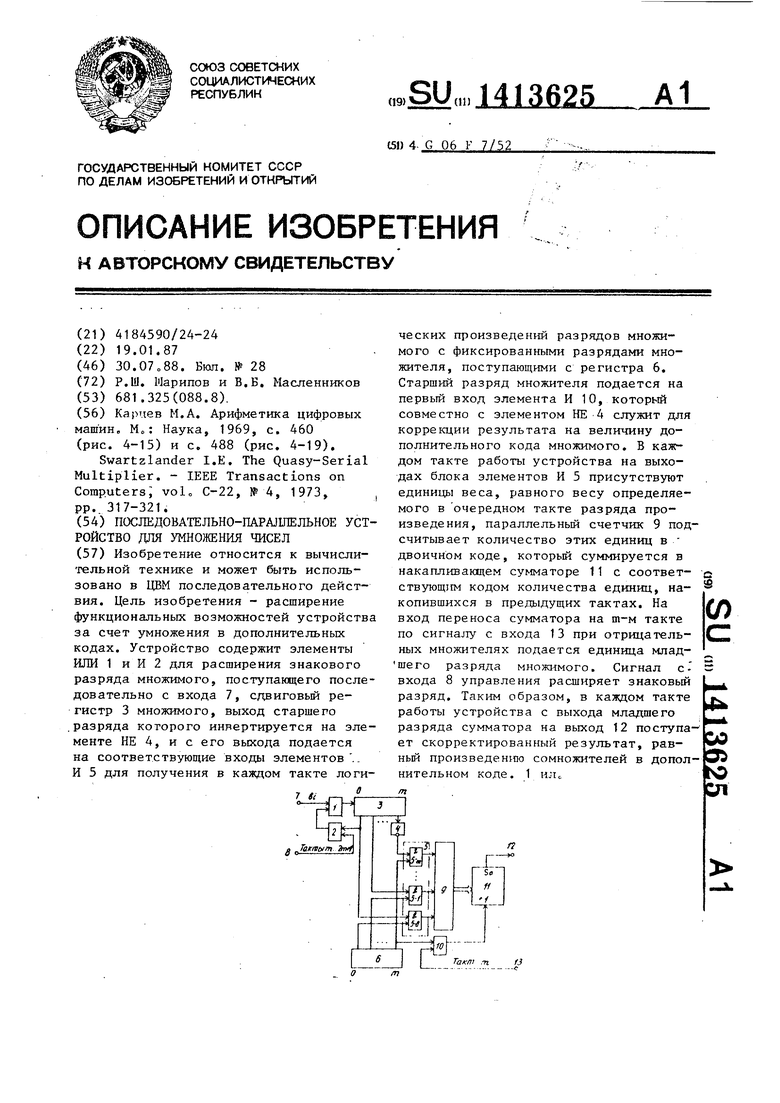

На чертеже приведена структурная схема предложенного устройства.

Устройство содержит элемент ИЛИ 1j элемент И 2 (необходимые для расширения знака множимого) сдвиговый ре- 1ГИСТР 3 множимого (предназначенный ДЛЯ хранения и сдвига множимого)э зле мент НЕ 4 (необходимый для коррекции результата на величину обратного кода множимого при отрицательных множителях) , группу элементов И 5; регистр 6 множителя, последовательный вход 7 множимого, вход 8 управления расширением знака5 параллельньй счетчик 9 (для подсчета суммы единиц с secoM, соответствующим номеру такта умножения) ,, элемент И 10 (для прибавления единицы младлего ра зряда множимого при отрицательных множителях), накапливающий сумматор 11 (для накопления результата произведения) по- следовательньй выход 12 результата (являющийся выходог разряда сумматора), вход 13 управления прибавлением единщы младшего разряда множимого Выходы регистров 3,6 соеди нены с соответствующими входами элементов И 5, причем старший разряд регистра 3 соединен через элемент НЕ 4, младший разряд регистра 3 дополнительно соединен с первым входом элемента И 2, второй вход которого соединен с входом 8, Выход элемента И 2 соединен с входом элемента ИЛИ 1, другой вход которого соединен с входом 7, а выход соединен с входом регистра 3. Старший (знаковьй) выход регистра 6 соединен с первым входом элемента И 10, второй вход которого соединен с входом 13, а выход - с входом переноса сумматора 11, Выходы элементов И 5 соединены с соответству ющими вхоц,ами параллельного счетчика 9, выходы которого соединены .со входами накапливающего сумматора 11, выход младшего разряда которого является выходом 12 результата устройства.

Устройство работает шедующим об- р.азом.

36252

Перед выполнением операции умножения производится обнуление регистра 3 и накапливающего сумматора 11, а в регистр 6 загружается множитель. При выполнении операции на вход регистра 3 в первые т-1 тактов работы поступает последовательный код множимого, а в такты с т-го по (2т+1)-й 0 знаковый разряд, эти разряды последовательно проходят через все т+1 разрядов регистра 3 и все элементы И 5, на других входах которых присутствуют фиксированные разряды множите5 ля, при этом разряды множимого, проходя через т-й разряд регистра 3, инвертируются на элементе НЕ 4 и участ вуют в коррекции результата, если множитель .

0 Таким образом, на выходах элементов И 5 присутствуют все возможные в каждом такте произведения отдельных бит сомножителей, имеющие вес, определяемьпЧ номером такта. Параллель5 ньй счетчик 9 подсчитывает количество единиц определенного веса. Накапливающий сумматор 11- формирует на выходе 12 очередной разряд произведения, суммируя переносы получившиеся

30 при сложении единиц меньшего веса с суммой единиц веса, соответствующего данному такту, при этом на выходе младглего разряда сумматора 11 присутствует очередной разряд результата, а остальные разряда1, представляющие двоичный код количества единиц большего веса, запоминаются и участвуют в формировании произведения в следующих тактах до (2т+1)-го такта. На вход переноса сумматора 11 в т-м такте в случае отрицательного множителя подается единица младшего разряда множимого, необходимая для коррекции на велргчину дополнительного кода от изображения множителя. Для ум5 ножения двух (т+1)-разрядных чисел необходимо 2т+1 тактов работы устройства. Формула изобретения

5

40

Последовательно-параллельное устройство для умножения чисел, содержащее регистр множителя, сдвиговый регистр, группу элементов И, параллельньй счетчик, накапливающий сумматор, причем выходы разрядов регистра множителя и сдвигового регистра множимого с нулевого по (т-1) (т+1).- число разрядов операндов) соединены с входами соответствующих элементов

3u.

и группы, выход m-ro разряда регистра множителя соединен с первым входом т-го элемента И группы, выходы элементов И группы соединены с входами параллельного счетчика, выходы которого соединены с входами накапливающего сумматора, выход младшего разряда которого является выходом результата устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности умножения в дополнительном коде, оно содержит элементы И, ИЛИ, HEj причем первьй вход первого элемента И соединен с выходом нулевого разряда сдвигового регистра множимого, второй вход первого

2 j

элемента И соединен с входом управления расширением знака устройства, Bbt- ход первого элемента И соединен с первым входом элемента ИЛИ, второй . вход которого соединен с входом множимого устройства, а выход соединен с входом сдвигового регистра множимого, выход т-го разряда которого соединен через элемент НЕ с вторым вхо-. дом т-го элемента И группы, первый вход которого соединен с первым входом элемента И, второй вход которого соединен с входом управления прибавлением единицы младшего разряда множимого устройства, а выход соединен с входом переноса накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Последовательно-параллельное устройство для умножения чисел в дополнительном коде | 1985 |

|

SU1259252A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для умножения на коэффициенты | 1987 |

|

SU1458872A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЦВМ последовательного действия. Цель изобретения - расширение функциональных возможностей устройства за счет умножения в дополнительных кодах. Устройство содержит элементы ИЛИ 1 и И 2 для расширения знакового разряда множимого, поступающего последовательно с входа 7, сдвиговый регистр 3 множимого, выход старшего разряда которого инвертируется на элементе НЕ А, и с его выхода подается на соответствующие входы элементов .- И 5 для получения в каждом такте логив ческих произведений разрядов множимого с фиксированными разрядами множителя, поступающими с регистра 6. Старший разряд множителя подается на первый вход элемента И 10, который совместно с элементом НЕ 4 служит для коррекции результата на величину дополнительного кода множимого, В каждом такте работы устройства на выходах блока элементов И 5 присутствуют единицы веса, равного весу определяемого в очередном такте разряда произведения, параллельный счетчик 9 подсчитывает количество этих единиц в двоичном коде, который суммируется в накапливающем сумматоре 11 с соответствующим кодом количества единиц, накопившихся в предыдущих тактах. На вход переноса сумматора на т-м такте по сигналу с входа 13 при отрицательных множителях подается единица млад- шего разряда множимого. Сигнал с- входа 8 управления расширяет знаковый разряд. Таким образом, в казадом такте работы устройства с выхода младшего разряда сумматора на выход 12 поступает скорректированный результат, равный произведению сомножителей в дополнительном коде. 1 иЛс т С (О П

| Карцев М.А, Арифметика цифровых машин, М.: Наука, 1969, с | |||

| Способ получения сульфокислот из нефтяных дестиллатов, минеральных масел, парафина или церезина, обработанных серною кислотою | 1912 |

|

SU460A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ и прибор для акустического исследования земных напластований | 1923 |

|

SU488A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Swartzlander I.E | |||

| The Quasy-Serial Multiplier | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Приспособление для обрезывания караваев теста | 1921 |

|

SU317A1 |

Авторы

Даты

1988-07-30—Публикация

1987-01-19—Подача