а

(UD

со

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического управления.

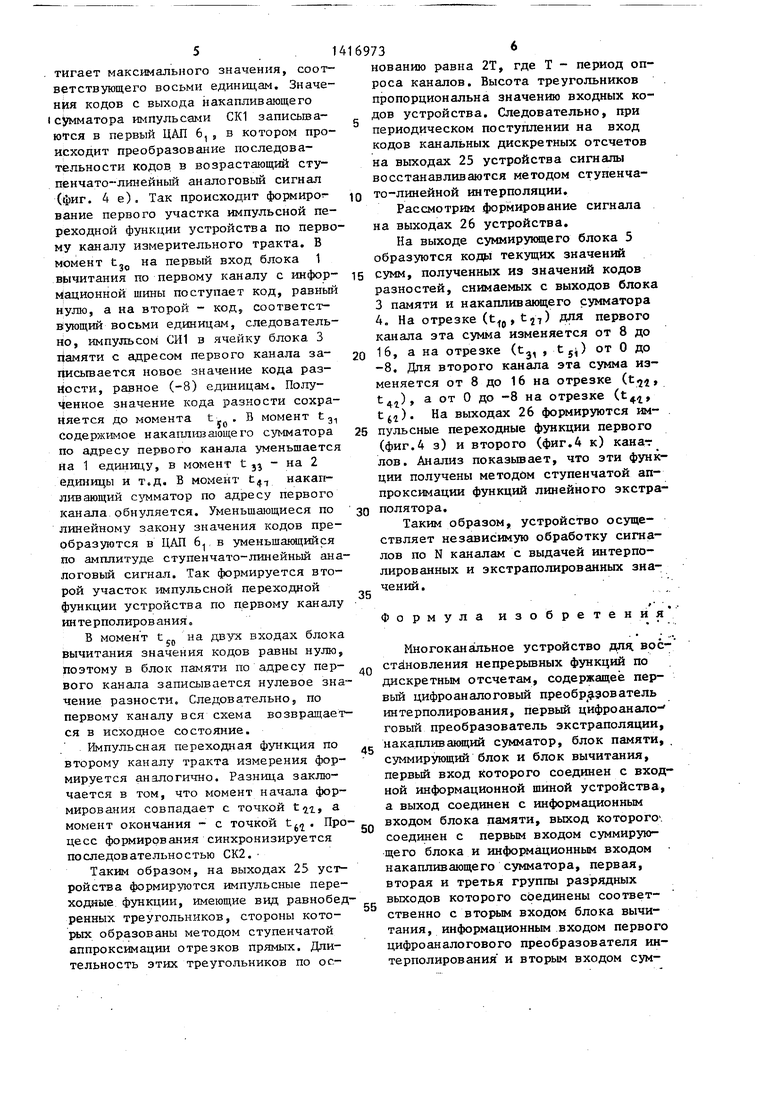

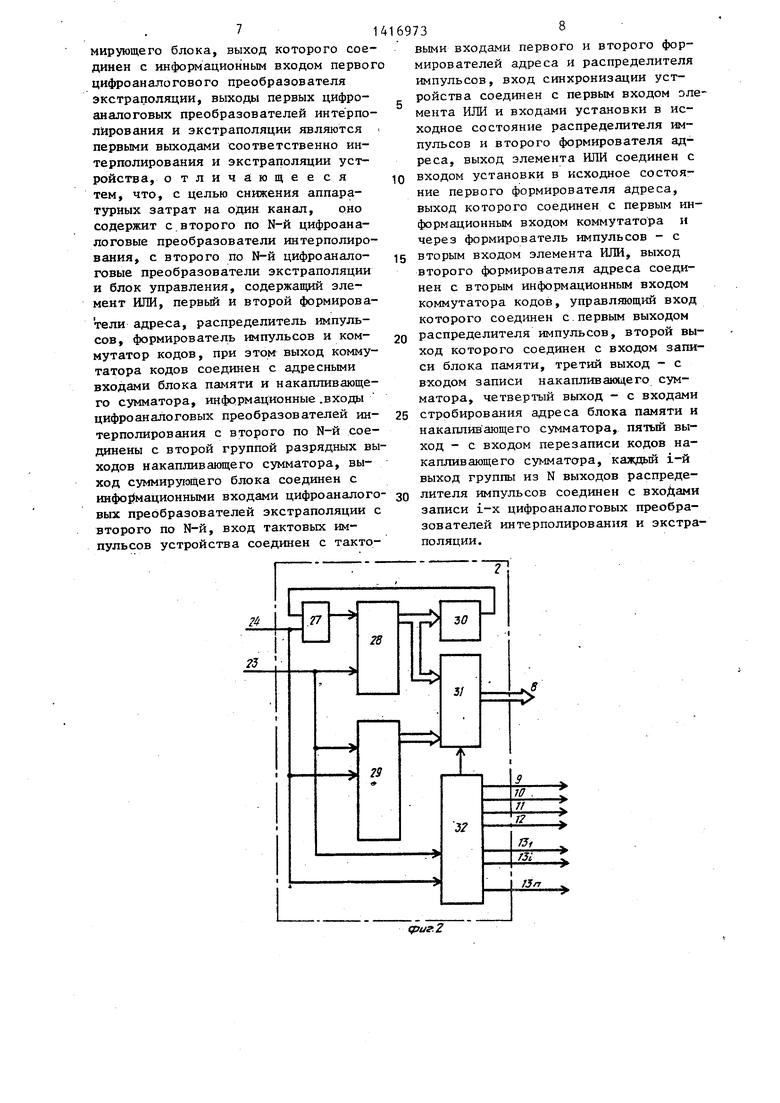

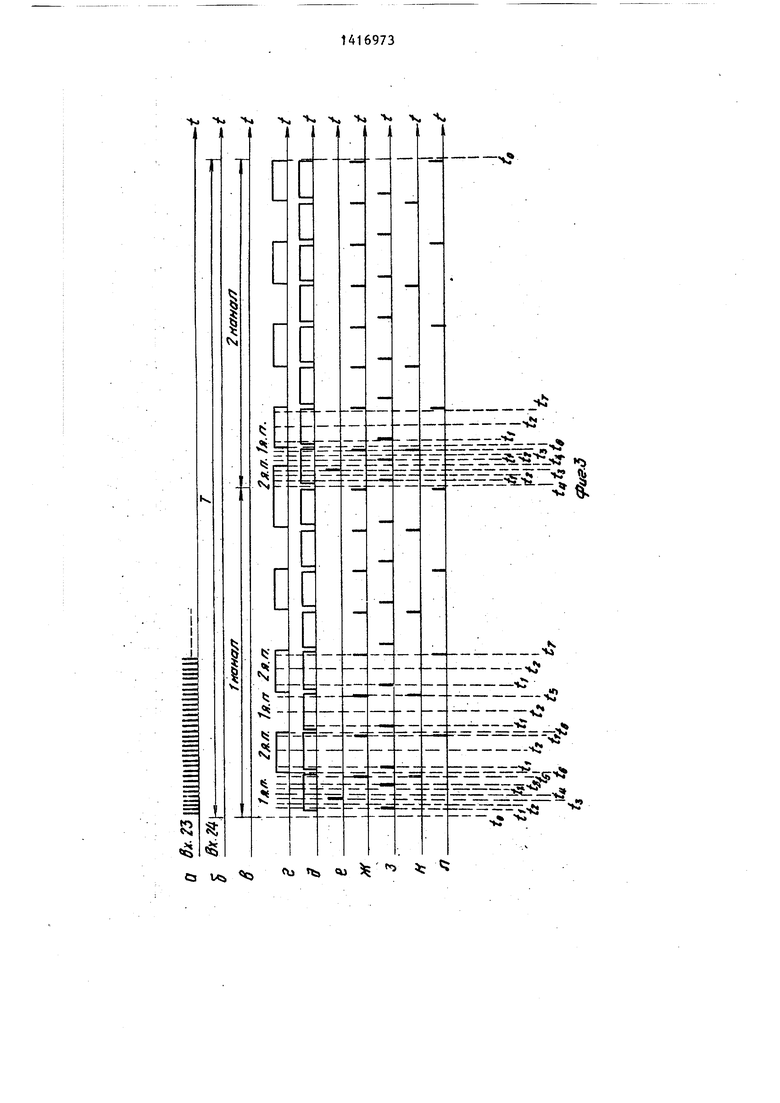

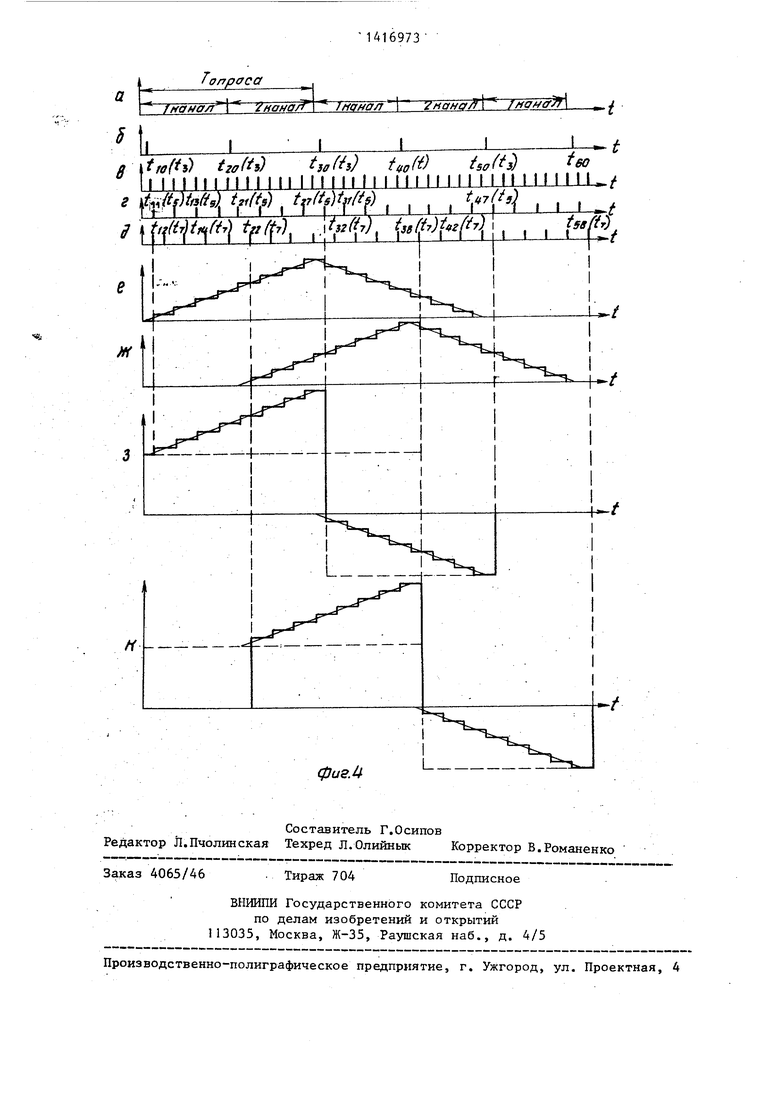

; Цель изобретения - снижение аппаратурных затрат на один канал. ; На фиг.1 приведена схема устройст- ва; на фиг.2 - схема блока управления; на фиг.З и 4 - временные диа д граммы, поясняющие работу устройства.

Устройство содержит блок 1 вычитания, блок 2 управления, блок памяти 3, накапливающий сумматор 4, суммирующий блок 5, цифроаналоговые преоб-|5 разователи (ЦАП) интерполирования, ЦАП экстраполяции, адрес- НЬЕн выход 8 блока управления, управляющие выходы 9-12 блока управления, Группу управляющих выходов 20 блока управления, информшдионный вход fl4 накапливающего сумматора, адресный рход 15, вход 16 записи, вход 17 стро- Жирования адреса, вход 18 перезаписи феодов, первая 19, вторая 20 и третья 25 21 группы разрядных выходов, информа- ционный вход 22 устройства, вход 23 тактовых импульсов, вход 24 синхронизации, выходы 25 каналов интерполирования и выходы 26 каналов экстрапо- gn пяции.

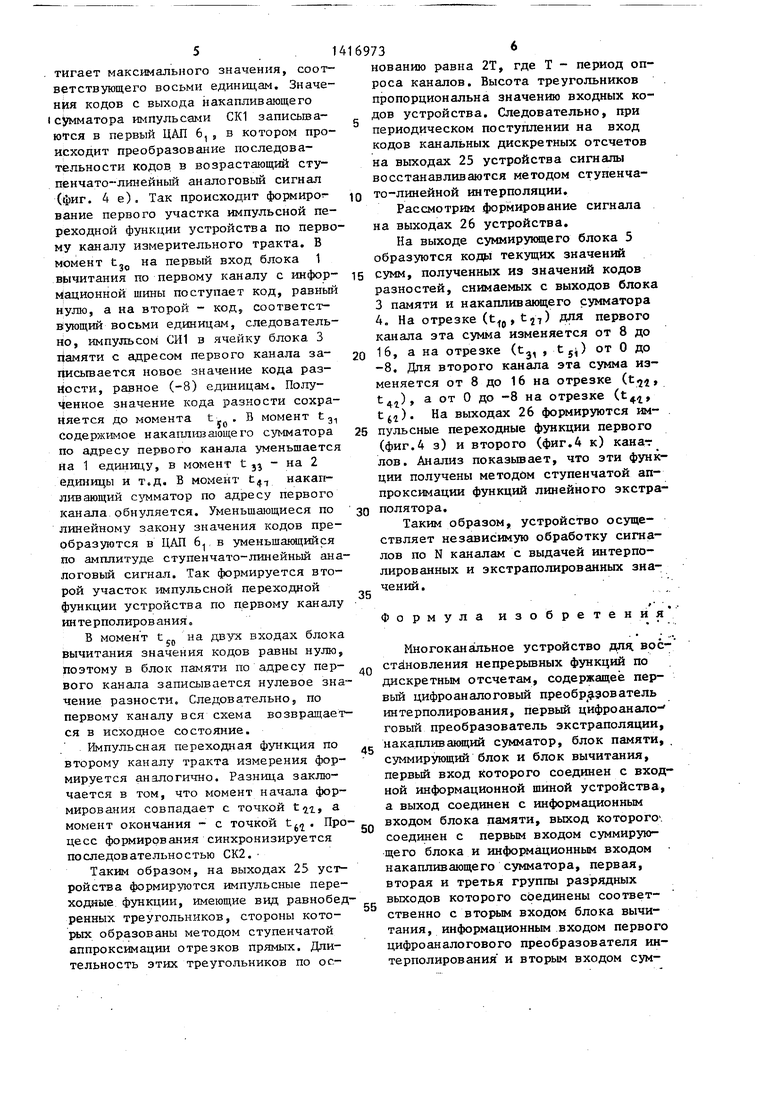

Блок 2 управления образуют элеент ИЛИ 27,, первый 28 и второй 29 формирователи адреса, формирователь 30 импульсов, коммутатор 31 кодов и : распределитель 32 импульсов.

: Устройство работает следующим об- |разом.

Ординаты восстанавливаемых функций закодированы L-разрядными параллельными кодами, которые подаются на информационный вход устройства в соответствующие канальные интервалы. Ординаты, соответствующие положительным значениям функций, представлены в прямом коде, а ординаты, соответствующие отрицательным значениям - в дополнительном коде.

Блок 1 вычитания предназначен для получения кодов разностей между кодами, поступающими на входную инфор- 50 мацирннзто шину, и кодами, поступающими с выхода 19 накапливающего сумматора 4 на второй вход блока вычитания. Блок 3 памяти хранит коды разностей, полученных в блоке вычитания 55 в ячейках с адресом соответствующего канала. Блок управления обеспечивает синхронную работу устройства при

40

45

д

5 0 5 n

:

0 5

0

5

помощи импульсов тактовой частоты, по- додаваемых на вход 23, и импульсов кадровой синхронизации, подаваемых на вход 24. Первый формирователь 28 адреса вырабатывает адреса ячеек памяти блоков 3 и 4, участвующих в процессе накопления кодов ординат восстанавливаемых функций по различным каналам. Второй формирователь 29 адреса вырабатывает адреса каналов для считывания опорных кодов opдшiaт из накапливающего сумматора 4 и записи кодов разностей ординат, полученных в блоке 1, в блок 3 памяти. В общем случае эти адресные формирователи представляют собой двоичные счетчики с тактирующим входом и возможностью установки в О. Формирователь 30 импульсов вырабатывает импульсы, соответствующие номенту окончания обработки кода текущей ординаты N-ro канала и может представлять собой дешифратор со схемой формирования короткого импульса. Элемент ИЛИ 27 предназначен для объе- динения импульсов кадровой синхронизации и импульсов конца обработки N-ro канала для обнуления формирователя 28. Распределитель 32 импульсов вырабатьшает следующие управля- ющие импульсы: импульсы СИ1 для записи кодов разностей ординат в блок 3 памяти (выход 9), импульсы СИ2 для записи текущих значений кодов ординат в накапливающем сумматоре 4 (выход 10)5 импульсы СИЗ для стробиро- ,вания адреса в блоке 3 памяти и накапливающем сумматоре 4 (выход 11), импульсы СИ4 для перезаписи текущих значений, кодов ординат в накапливающем сумматоре (выход 12), син- хронизирующие импульсы СК- (,N) для записи кйдов.: текущих значений ординат в ЦАП- трак-тоВ;,измерения и управления (выходь 13). Он может быть реализован. н,а двоичном счетчике с тактирзтощим входом и возможностью установки в О и на дешифраторах. Коммутатор 31 подключает адресные, выходы первого или второго адресного формирователя к выходу 8 блока управления. Накапливающий сумматор предназначен для получения те- I кзтдих значений кодов ординат на интервале аппроксимации. Блоки накапливающего сумматора содержат в общем случае L+M разрядов, где М - число дополнительных разрядов, определяемое допустимой погрешностью аппроксимации отрезков прямых линий ступенчато-ломаной кривой. Обычно М определяется из уравнения 2 К, где К - число тактов суммирования на интервале аппроксимации, Информацион- ньШ вход 14 содержит L разрядов, соединенных с L младшими разрядными входами (L+M)-разрядного сумматора. При таком соединении происходит деление кода разности на .

В бло ке 1 вычитания вырабатывается разность между входными кодами ординат и кодами с первой группы раз- рядных выходов накапливающего сумматора 4. Код разности записывается по адресу, задаваемому блоком управления, в блоке 3 памяти. Из блока памямент t при наличии импульсов СИЗ на выходе блока 1 вычитания образуются коды разностей, а на выходах сумматора, в накапливающем сумматоре и на выходах суммирующего блока - коды текущих значений ординат.

Пусть , . В этом случае накапливающий сумматор содержит 11 двоичных разрядов. Сигналы с выхода блока памяти 3 подаются на входы восьми младших разрядов накапливающего сумматора. Три группы выходов накапливающего сумматора объединяются в одну группу выходов (это справедливо только в рассматриваемом случае), снимаемых с восьми старших разрядов.

В исходном состоянии накапливаю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1983 |

|

SU1124338A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| УСТРОЙСТВО ДЛЯ ИНТЕРПОЛЯЦИИ | 1990 |

|

RU2042979C1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Цифровой Т-генератор функций | 1985 |

|

SU1256006A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Телеизмерительная система | 1983 |

|

SU1088049A2 |

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического управления. Цель изобретения - снижение аппаратурных затрат на один канал. Устройство содержит блок вычитания 1, блок управления 2, блок памяти 3, накапливающий сумматор 4, суммирующий блок 5, цифроаналоговые преобразователи интерполирования 6(у и экстраполяции 7,-7. Устройство осуществляет обработку многоканального сигнала в режиме разделения времени, который обеспечивается блоком управления. В каждом канале устройства осуществляется кусочно-линейное восстановление сигнала по дискретным отсчетам, поступающим на информационный вход. 4 ил. § (Л

ти.код разности считьшается и подает-2о Щ сумматор 4 и блок 3 памяти обнулены, поэтому по цепи обратной связи

ся на первый вход суммирующего блока 5 и на вход накапливающего сумматора, где получают текущие значения кодов ординат. На второй группе разрядных выходов накапливающего сумматора 4 формируются коды, соответствующие значениям функций, восстановленных методом ступенчато-линейной интерполяции. Эти коды переписьшаются с по- мощыд импульсов записи в соответствующие цифро-аналоговые.преобразователи 6.

В блоке 5 осуществляется суммирование кодов, формируемых на третьей группе разрядных выходов блока 4 и кодов, значения которых соответствуют первым разностям интерполируемых функций, поступающих с блока 3. На его выходе формируются коды, соот

ветствующие значениям функций, восстановленных методом ступенчато-линейной экстраполяции. Эти коды переписываются в соответствующие ЦАП 7, где они преобразуются в аналоговые сигналы.

Рассмотрим принцип работы блока управления при числе каналов N 2 и количестве тактов суммирования на интервале аппроксимации К 8. При N 2 адресный выход трансформируется в односигнальную линию. В моменты tp происходит установка блока 2 управления импульсом кадровой синхронизации (фиг.36) в исходное состоя- ние.. В моменты t, при совпадении импульсов СИ4 и СИЗ происходит перезапись кодов из соответствующих ячеек блока памяти накапливающего сум-

, матора4 в его буферный регистр. В мо35

в течение первого периода опроса по адресам всех ячеек на второй вход блока 1 вычитания поступают коды,рав25 ные нулю, а на первый - код, равный восьми условным единицам 00001000.

После того, как на входную информационную шину поступает параллельный код первого канала, соответст30 вующий одиночному отсчету, амплитуда которого равна, например, восьми условным единицам, а на первый управляющий вход блока памяти 3 поступает импульс СИ1 (в момент t ), в ячейке с адресом первого канала записывается код разности 00001000. Это значение кода разности по первому каналу сохраняется в блоке памяти до момента tjp поступления, следующего значения входного кода по первому каналу и получения нового значения кода разности. В момент t,, поступления импульса СИ2 на первый управлякиций : вход накапливающего сумматора в ячейке с адресом первого канала записывается код 00000001. Таким образом, в сумматоре 4 происходит деление значения полученной разности на 8 (в общем случае на 2). Это объясняется тем, что входные сигналы подаются на 8 младших разрядов, а выходные сигналы снимаются с восьми старших разрядов накапливающего сумматора. С поступлением следующих импульсов СИ2, совпадающих с СК1 (в моменты ,40

45

50

55

t,-,), значение кода на выходе накапливающего сумматора по этому адресу возрастает по линейному закону, причем в момент tn значение кода дос

в течение первого периода опроса по адресам всех ячеек на второй вход блока 1 вычитания поступают коды,равные нулю, а на первый - код, равный восьми условным единицам 00001000.

После того, как на входную информационную шину поступает параллельный код первого канала, соответствующий одиночному отсчету, амплитуда которого равна, например, восьми условным единицам, а на первый управляющий вход блока памяти 3 поступает импульс СИ1 (в момент t ), в ячейке с адресом первого канала записывается код разности 00001000. Это значение кода разности по первому каналу сохраняется в блоке памяти до момента tjp поступления, следующего значения входного кода по первому каналу и получения нового значения кода разности. В момент t,, поступления импульса СИ2 на первый управлякиций : вход накапливающего сумматора в ячейке с адресом первого канала записывается код 00000001. Таким образом, в сумматоре 4 происходит деление значения полученной разности на 8 (в общем случае на 2). Это объясняется тем, что входные сигналы подаются на 8 младших разрядов, а выходные сигналы снимаются с восьми старших разрядов накапливающего сумматора. С поступлением следующих импульсов СИ2, совпадающих с СК1 (в моменты ,

t,-,), значение кода на выходе накапливающего сумматора по этому адресу возрастает по линейному закону, причем в момент tn значение кода дос10

15

20

тигает максимального значения, соответствующего восьми единицам. Значения кодов с выхода накапливающего

сумматора импульсами СК1 записьша- ются в первый ЦАП 6,, в котором происходит преобразование последовательности кодов, в возрастающий ступенчато-линейный аналоговый сигнал (фиг. 4 е). Так происходит формиро - вание первого участка импульсной переходной функции устройства по первому каналу измерительного тракта. В момент tj на первый вход блока 1 вычитания по первому каналу с информационной шины поступает код, равный нулю, а на второй - код, соответствующий восьми единицам, следовательно, импульсом СИ1 в ячейку блока 3 йамяти с адресом первого канала за- гшсьгаается новое значение кода разнести, равное (-8) едршицам. Полученное значение кода разности сохраняется до момента t . В момент t содержимое накапливающего сумматора по адресу первого канала уменьшается иа 1 единицу, в момент t j - на 2 единицы и т.д. В момент t накапливающий сз мматор по адресу первого канала обнуляется. Уменьшающиеся по линейному закону значения кодов преобразуются в ЦАП 6 в уменьшающийся по амплитуде ступенчато-линейный ана- логовьш сигнал. Так формируется второй участок импульсной переходной функции устройства по первому каналу интерполирования,

В момент tjp на двух входах блока вычитания значения кодов равны нулю, поэтому в блок памяти по адресу первого канала записывается нулевое значение разности. Следовательно, по первому каналу вся схема возвращается в исходное состояние.

Импульсная переходная функция по второму каналу тракта измерения формируется аналогично. Разница заключается в том, что момент начала формирования совпадает с точкой t., а

момент окончания - с точкой t,« . Про- „

ci50

цесс формирования синхронизируется

последовательностью СК2.

Таким образом, на выходах 25 устройства формиру отся импульсные переходные функции, имеющие вид равнобедренных треугольников, стороны которых образованы методом ступенчатой аппроксимации отрезков прямых. Длительность этих треугольников по ос25

30

35

40

55

нованию равна 2Т, где Т - период опроса каналов. Высота треугольников пропорциональна значению входных кодов устройства. Следовательно, при периодическом поступлении на вход кодов канальных дискретных отсчетов на выходах 25 устройства сигналы восстанавливаются методом ступенчато-линейной интерполяции.

Рассмотрим формирование сигнала на выходах 26 устройства.

На выходе суммирующего блока 3 образуются коды текущих значений сумм, полученных из значений кодов разностей, снимаемых с выходов блока 3 памяти и накапливакнцего сумматора 4. На отрезке (t, tj7) ДЛя первого канала эта сумма изменяется от 8 до 16, а на отрезке (t,, , t 5 от О до -8. Для второго канала эта сумма изменяется от 8 до 16 на отрезке (t, ), а от О до -8 на отрезке (t, tji). На выходах 26 формируются им- пульсные переходные функции первого (фиг.4 з) и второго (фиг.4 к) канат лов. Анализ показьшает, что эти функции получены методом ступенчатой аппроксимации функций линейного экстра- полятора.

Таким образом, устройство осуществляет независимую обработку сигналов по N каналам с выдачей интерполированных и экстраполированных значений.

Формула изобретения

„

0

0

5

Многоканальное устройство для вое- становления непрерьшных функций по дискретным отсчетам, содержащее первый цифроаналоговый преобразователь интерполирования, первый цифроанало- говый преобразователь экстраполяции, накапливающий сумматор, блок памяти, суммирующий блок и блок вычитания, первый вход которого соединен с входной информационной шиной устройства, а выход соединен с информационным входом блока памяти, выход которого;, соединен с первым входом суммирующего блока и информационным входом накапливающего сумматора, первая, вторая и третья группы разрядных выходов которого соединены соответственно с вторым входом блока вычитания, информационным входом первого цифроаналогового преобразователя интерполирования и вторым входом суммирующего блока, выход которого соединен с информационным входом первог цифроаналогового преобразователя экстраполяции, выходы первых цифро- аналоговых преобразователей интерполирования и экстраполяции являются первыми выходами соответственно интерполирования и экстраполяции устройства, отлича;ющееся тем, что, с целью снижения аппаратурных затрат на один канал, оно содержит с второго по N-й цифроаналоговые преобразователи интерполирования, с второго по N-й цифроанало- говые преобразователи экстраполяции и блок управления, содержащий элемент ИЛИ, первый и второй формирователи адреса, распределитель импульсов, формирователь импульсов и ком- мутатор кодов, при этом выход коммутатора кодов соединен с адресными входами блока памяти и накапливающего сумматора, информационные.входы цифроаналоговых преобразователей ин- терполирования с второго по N-й соединены с второй группой разрядных выходов накапливающего сумматора, выход суммирующего блока соединен с инфо1 мационными входами цифроаналого вых преобразователей экстраполяции с второго по N-й, вход тактовых импульсов устройства соединен с тактовыми входами первого и второго формирователей адреса и распределителя импульсов, вход синхронизации устройства соединен с первым входом элемента ИЛИ и входами установки в исходное состояние распределителя импульсов и второго формирователя адреса, выход элемента ИЛИ соединен с входом установки в исходное состояние первого формирователя адреса, выход которого соединен с первым информационным входом коммутатора и через формирователь импульсов - с вторым входом элемента ИЛИ, выход второго формирователя адреса соединен с вторым информационным входом коммутатора кодов, управляющий вход которого соединен с.первым выходом распределителя импульсов, второй выход которого соединен с входом записи блока памяти, третий выход - с входом записи накапливающего сумматора, четвертый выход - с входами стробирования адреса блока памяти и накапливающего сумматора, пятый выход - с входом перезаписи кодов накапливающего сумматора, каждый i-й выход группы из N выходов распределителя импульсов соединен с вхоДами записи i-x цифроаналоговых преобразователей интерполирования и экстраполяции.

K,X,4s,, 4

fO «Ч

C3 C5

fVi Ъ W

1

1

1

(t t2o( t,a() () fso(teo

III I nil MM I II I II Ml II I III III II I in I li I г t.i:.(t . /./X.)y . , . . ../y

({ (,(н

.; I

LLS t

.

ч

фигМ

Составитель Г.Осипов Редактор Л.Пчолинская Техред Л.Олийнык Корректор В.Романенко

Заказ 4065/46

Тираж 704

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

I in I li I ./y

.; I

LLS t

:/.

Подписное

| Линейный интерполятор | 1980 |

|

SU883925A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-15—Публикация

1987-01-15—Подача