Изобретение относится к вычислительной технике и может быть использовано для контроля БИС, например, рерии КР580 , и сервисного оборудования электронной аппаратуры на базе БИС.

Цель изобретения - повышение надежности устройства за счет сокращения объема оборудования(ПЗУ для хранения тестовьтх программ).

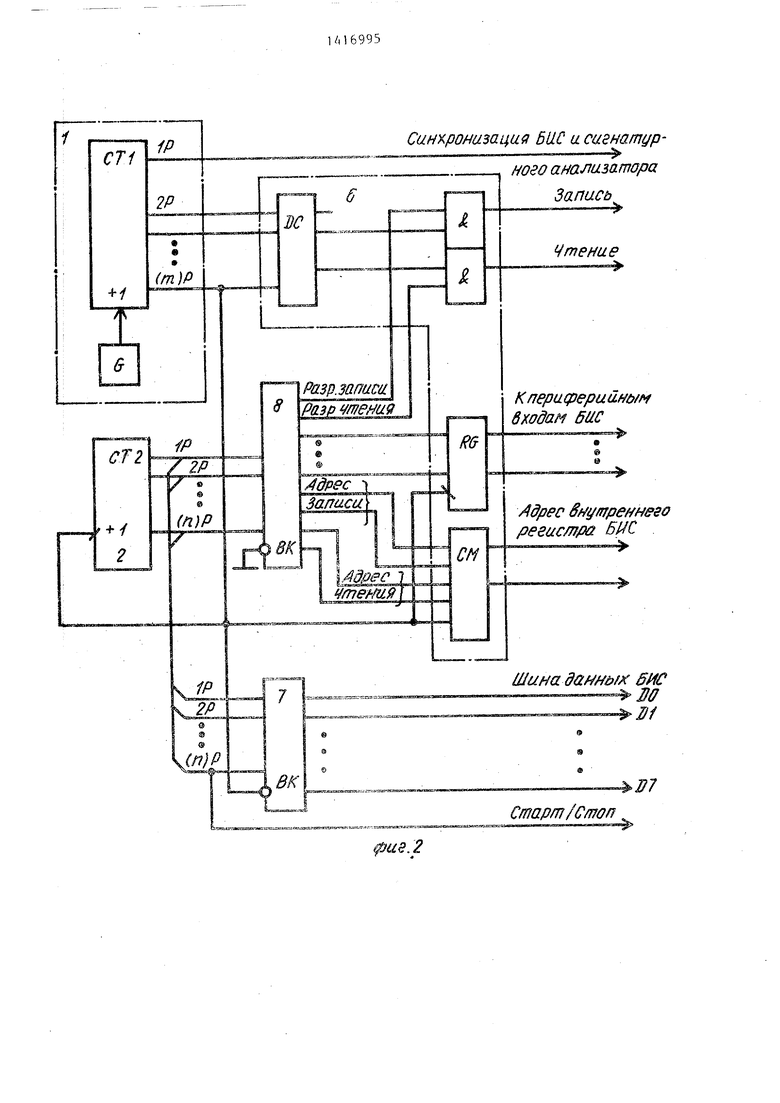

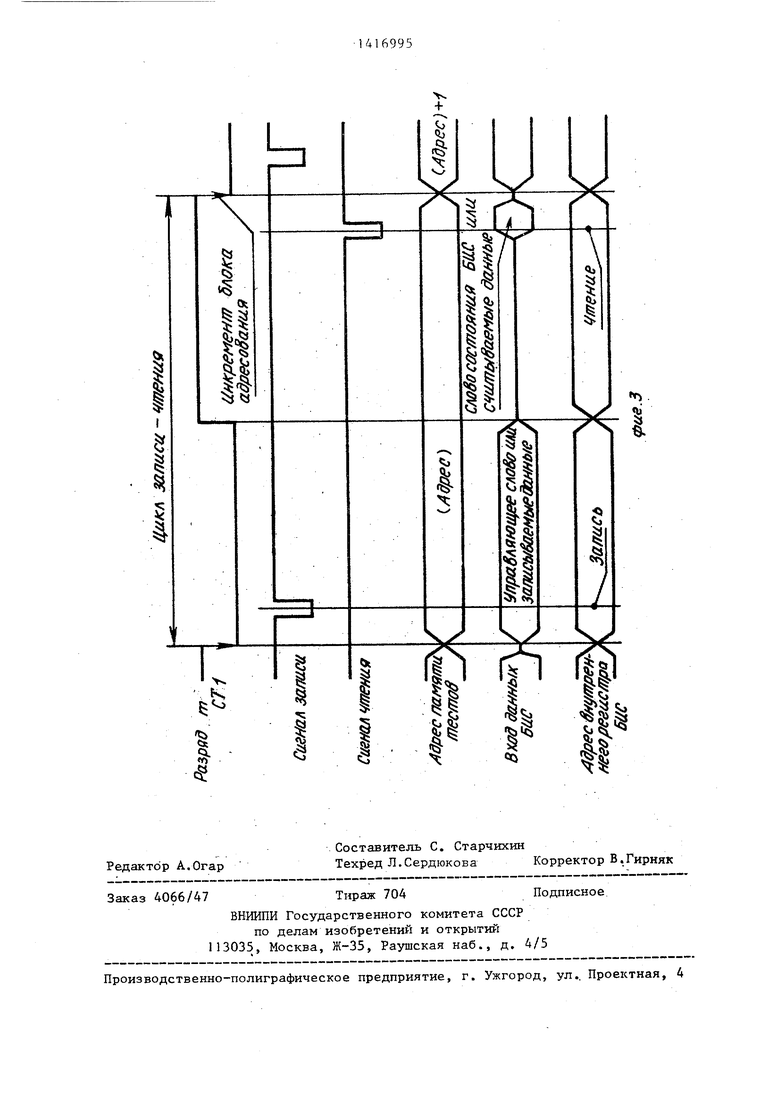

На фиг. 1 приведена струастурная схема устройства; на фиг. 2 - пример

конкретной реализации устройства; на фиг. 3 - временные диаграммы его работы.

Устройство (фиг.) содержит блок 1 синхронизации, блок 2 адресования и блок 3 памяти. Позицией 4 обозначена контролируемая БИС. Устройство содержит также сигнатурный анализатор

5и блок 6 формирования управляющих и адресных сигналов. В состав блока

3 памяти входят блок 7 памяти данных и блок 8 управляющей памяти.

Устройство работает следующим об разом. .

Для проверки программируемых БИС, например периферийных БИС микропроцессорного набора КР580, необходимо последовательно программировать различные режимы работы БИС и проверять правильность их вьтолненияс, При этом необходимо формировать последо- вательности команд и данных, записывать их в регистр команд или в регистр данных проверяемых БИС соответственно и считьшать слово состояния и регистр данных. Выбор внутреннего регистра осуществляется посредством адресных входов проверяемой БИС. Запись и чтение ; информации инициируются сигналами записи и чт.ения. В связи с тем, что время выполнения различных команд в разных регистрах различно, распределение сигналов записи и чтения во времени неравномерно и для их формирования обычно используют мгпсропроцессор или микропрог раммньй автомат. В предлагаемом устройстве сигналы записи и чтения во времени распределены равномерно, с ними синхронизирован поток данных. Такое решение при простой схеме позволяет значительно сократить объем памяти программ.

В процессе работы устройства блок

6формирования сигналов из последовательности импульсов синхронизации

0

0

5

0

выраоатьшает в заранее определенные моменты времени сих налы записи и чтения информации из проверяемой БИС 4 (фиг.З). Блок 8 управляющей памяти через блок 6 формирования сигналов оебспечивает выбор внутреннего регистра или порта БИС, в который или из которого производится запись-чтение информации, и разрешает или запрещает запись-чтение информации. Кроме того, с выходов блока 8 осуществляется воздействие на периферийные входы БИС о С выхода блока 7 на шине 5 данных контролируемой БИС 4 устанавливается управляющее слово или данные на время действия сигнала записи. Во время действия сигнала чтения выход блока 7 блокируется сигналом ВК с блока 1 синхронизации (разряд m СТ 1, фиг,2), чтобы не искажать счи- тьшаемую информацию. Блоки 7 и 8 выдают и изменяют- информацию под воздействием блока 2 адресования, который последовательно циклически изменяет свое состояние под действием импульсов синхронизации. Сигналы, поступающие на БИС по периферийным входам, обеспечивают выполнение этой БИС заданного режима работы.

Сигналы с выходов проверяемой БИС поступают на входы данных сигнатурного анализатора 5. Для их правильной обработки анализатор имеет два управляющих входа. Вход синхронизации служит для стробирования входных данных. С помощью этого сигнала анализатор принимает данные с входов во внутренний регистр и производит их логическую обработку. Сигнал окна измерения (разрещенйя приема данных) указывает на начало и окончание тестовой процедуры. В качестве сигнала синхронизации используется сигнал синхронизации БИС, чем обеспечивается регистрация откликов проверяемой БИС в каждом такте. В качестве сигнала окна измерения используется ст.арщий разряд блока 2 адресования (фиг.2),. которьш изменяет свое состояние с 1 в О при окончании теста и воз-, врате к началу тестовой программы.

В примере конкретного исполнения устройства (фиг,2) в качестве блока синзронизации используется двоичный счетчик СТ1 совместно с генератором импульсов G. Разряды счетчика используются для синхронизации контролируемой БИС и формирования с помощью

5

0

5

0

5

дешифратора DC снгналов чтения и записи. На входы БИС сигналы чтения и записи поступают со схемы совпадения, управляемой сигналами Разреше- ние записи и Разрешение чтения, что позволяет гибко формировать тестовую процедуру. Сигналы Адрес записи и Адрес чтения поступают на входы контролируемой БИС через татор сигналов СМ синхронно с сигналами записи и чтения соответственно и определяют в какой или из какого внутреннего регистра или порта БИС будет произведена запись-чтение ин- формации. Управление коммутатором осуществляется разрядом m счетчика СТ1. При равенстве его О формируется сигнал записи, при равенстве 1 - чтения (фиг.ЗК Этим же разрядом разрешается выдача информации из блока 7 памяти данных на шину данных контролируемой БИС при наличии сигнала записи и запрещается работа памяти данных при чтении информации из БИС.

Блок 2. адресования в данном устройстве представлен двоичным счетчиком СТ2, управляемым от блока синхронизации. Изменение состояния СТ2 (прибавление единицы к состоянию счетчика ) осуществляется в конце цикла записи-чтения. При этом изменяется информация на выходах блока памяти и производится очередная проверка БИС,

Управление периферийными входами проверяемой БИС осуществляется сигналами блока 8 управляющей, памяти через буферный регистр RG, расположенный в блоке 6. Регистр необходим для исключения ложных импульсов, которые югут иметь место на выходах 1икро- схем ПЗУ блока 8 управляющей памяти в MokeHT изменения адреса блоком 2 адресования (счетчик СТ2). При этом из- менение состояния счетчика СТ2 происходит по переднему фронту сигнала инкрементирования блока адресования (разряд m счетчика СТ1), а прием в регистр - по заднему, когда информа- ция на вькодах ПЗУ уже стабильна и достоверна.

Предлагаемое устройство по сравнению с известнь м характеризуется вы- сокой надежностью и малой стоимостью за счет значительно меньших затрат памяти программ. Это обеспечивается

тем, что наиболее высокочастотные и малые по длительности входные сигналы контролируемой БИС (синхронизации, чтения, записи )формируются ап- паратно, а в памяти хранятся только команды и данные, число которых невелико .

Формула изобретения

Устройство для контроля цифровых блоков,содержащее блок синхронизации блок адресования и блок памяти данных причем первьш выход блока синхронизации является выходом устройства для подключения синхровхода контролируемого блока, второй выход блока синхронизации соединен с синхровходом блока адресования, первая группа выходов которого соед1шена с группой адресных входов блока памяти данных , группа выходов которого является группой выходов устройства для подключения входов данных контролируемого блока, отличающееся тем, что, с целью повьшгения надежности устройства за счет сокращения оборудования, оно содержит блок формирования управляющих и адресных сигналов, сигнатурный анализатор и блок управляющей памяти, группа адресных входов которого объединена с группой адресных входов блока памяти данных, синхро- вход блока формирования управляющих и адресных сигналов подключен к третьему выходу блока синхронизации, группа информационных входов блока формирования управляющих и адресных сигналов подключена к группе выходов блока управляющей памяти, а первая группа выходов блока формирования управляющих и адресных сигналов является группой выходов устройства для подключения управляющих и адресных входов контролируемого блока, вторюй выход блока формирования управляющих и адресных сигналов соединен с входом разрешения блока памяти данных, синхровход сигнатурного анализатора соединен с первым восходом блока синхронизации, группа информационных входов сигнатурного анализатора является группой информационных входов устройства для подключения выходов контролируемого блока, управляющий вход окна измерения сигнатурного анализатора соединен; с вторым выходом блока адресования..

СП

ip

2Р

Санкроиизаци 5I1C и. сигнатурного анализатора Запись

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1336123A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля оперативной памяти тестом Марш с двоично-нарастающим адресным шагом | 1986 |

|

SU1532978A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1053165A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1032481A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1070607A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля периферийных БИС5 например, серии КР580. Целью изобретения является повьязение надежности устройства. Устройство содержит блок 1 сш хронизации, блок 2 адресования, сигнатурный анализатор 5, блок 6 формирования управляющих и адресных сигналов, блок 7 памяти данных и блок 8 управляющей памяти. Повышение надежности обеспечивается за счет меньших по сравнению с прототипом затрат памяти программ Это достигается тем, что наиболее высокочастотные к малые по длительности входные сигналы контролируемой,БИС (синхронизации, чтения, записи) формируются аппаратно, а в памяти хранятся только команды и данные, число которых невелико. 3 ил. с ф (Л е о со со d

+ i

(т)Р

8

Разрмпаш

Разр упоения

СТ2

7 2Р

/ в

дрес

4-/

(п)Р

Запасах

1/тет,я

Чтение

™

К nepiKpepauHtf/f входам 6UC

R&

& в

СМ

Адрес ef/y/npef Heso peeucmj Sf/C

------

UluHudaf Hiy/x ВИС

.,,.....

ff7

Старт/Стоп

$

ае. 2

| Механизация и автоматизация управления, 1983, W 3 (117, с | |||

| Механический грохот | 1922 |

|

SU41A1 |

| Средства диагностирования и отладки микропроцессорных систем: Материалы семинара, 14-15 июня 1984 г | |||

| Л..общество Знание, Лениградский Дом научно-технической пропаганды, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-08-15—Публикация

1986-07-04—Подача