00 00

Изобретение относится к вычислительной технике, может быть использовано в двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти и является усовершенствованием устройства по авт. св. № 1251176.

Цель изобретения - повьш1ение надежности и эффективной емкости устройства.

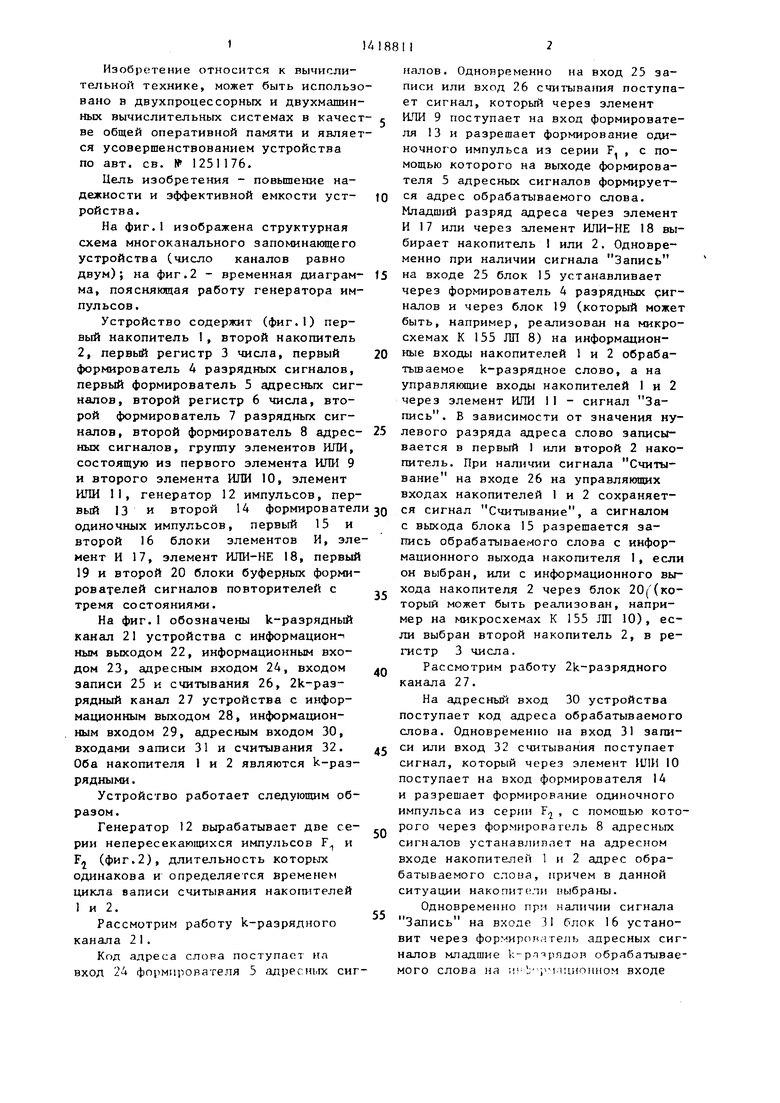

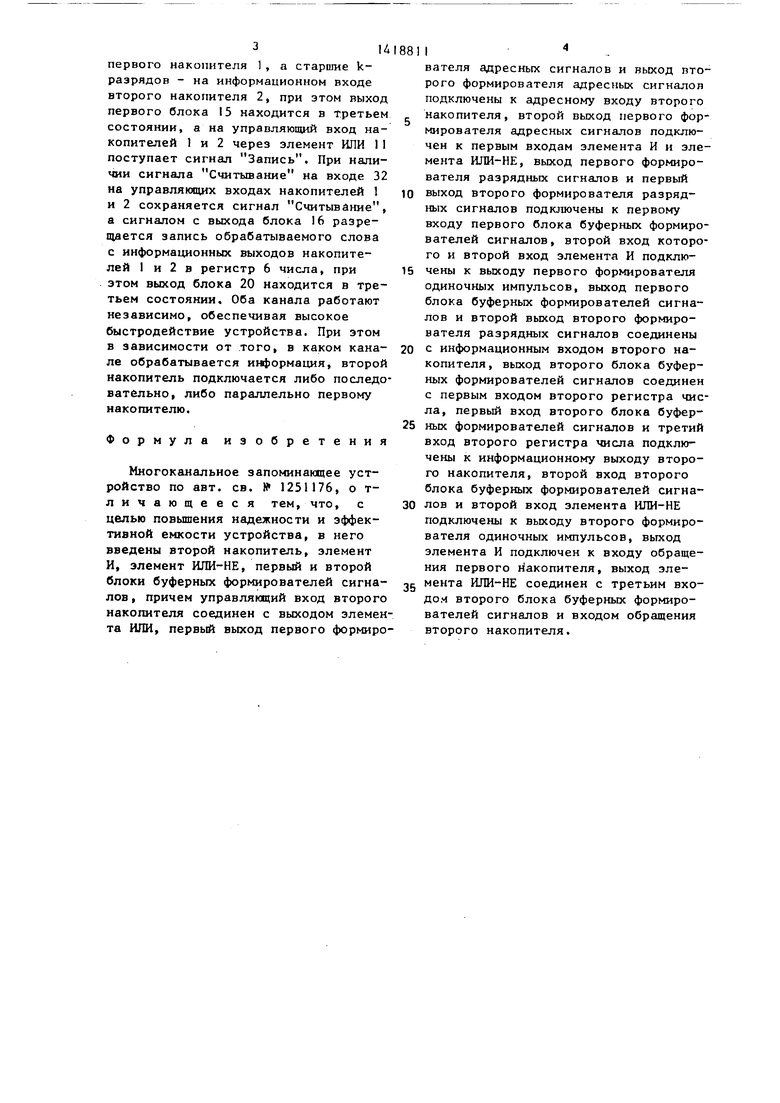

На фиг.1 изображена структурная схема многоканального запоминающего устройства (число каналов равно двум); на фиг.2 - временная диаграмма, поясняющая работу генератора импульсов .

Устройство содержит (фиг.1) первый накопитель I, второй накопитель 2, первый регистр 3 числа, первый формирователь 4 разрядных сигналов, первый формирователь 5 адресных сигналов, второй регистр 6 числа, второй формирователь 7 разрядных сигналов, второй формирователь 8 адресных сигналов, группу элементов ИЛИ, состоящую из первого элемента ИЛИ 9 и второго элемента ИЛИ 10, элемент ШШ 11, генератор 12 импульсов, первый 13 и второй 14 формировател одиночных импульсов, первый 15 и второй 16 блоки элементов И, элемент И 17, элемент ИЛИ-НЕ 18, первый 19 и второй 20 блоки буфер 1ых формирователей сигналов повторителей с тремя состояниями.

На фиг.1 обозначены k-разрядный канал 21 устройства с информацион-i ным выходом 22, информационным входом 23, адресным входом 24, входом записи 25 и считывания 26, 2k-pa3- рядный канал 27 устройства с информационным выходом 28, информационным входом 29, адресным входом 30, входами записи 31 и считывания 32. Оба накопителя 1 и 2 являются k-раз- рядными.

Устройство работает следующим образом.

Генератор 12 вырабатывает две серии непересекаю1цихся импульсов F и FJ (фиг.2), длительность которых одинакова и определяется вpeмeнe цикла записи считывания накопителей 1 и 2.

Рассмотрим работу k-разрядного канала 21.

Код адреса слова поступает нп вход 24 формирователя 5 адресных си1

o

5

0

5

0

5

0

5

0

5

налов. Однонременно на вход 25 записи или вход 26 считъшагшя поступает сигнал, который через элемент ИЛИ 9 поступает на вход формирователя 13 и разрешает формирование одиночного импульса из серии F , с помощью которого на выходе формирователя 5 адресных сигналов формируется адрес обрабатываемого слова. Младший разряд адреса через элемент И 17 или через элемент ИЛИ-НЕ 18 выбирает накопитель I или 2, Одновременно при наличии сигнала Запись на входе 25 блок 15 устанавливает через формирователь 4 разрядных риг- налов и через блок 19 (который может быть, например, реализован на микросхемах К 155 ЛП 8) на информационные входы накопителей 1 и 2 обраба- тьшаемое k-разрядное слово, а на управляющие входы накопителей 1 и 2 через элемент ИЛИ II - сигнал Запись . В зависимости от значения нулевого разряда адреса слово записывается в первый I или второй 2 накопитель. При наличии сигнала Считывание на входе 26 на управляющих входах накопителей 1 и 2 сохраняется сигнал Считывание, а сигналом с выхода блока 15 разрешается запись обрабатываемого слова с информационного выхода накопителя 1, если он выбран, или с информационного выхода накопителя 2 через блок 20((ко- торый может быть реализован, например на микросхемах К 155 ЛП 10), если выбран второй накопитель 2, в регистр 3 числа.

Рассмотрим работу 2k-paзpяднoгo канала 27.

На адресный вход 30 устройства поступает код адреса обрабатываемого слова. Одновременно на вход 31 записи или вход 32 считывания поступает сигнал, который через элемент ИЛИ 10 поступает на вход формирователя 14 и разрешает формирование одиночного импульса из серии F, с помощью которого через формироратель 8 адресных сигналов устанавлиплет на адресном входе накопителем 1 и 2 адрес обрабатываемого слова, причем в данной ситуации накопители выбраны.

Одновременно при наличии сигнала Запись на вхохте 31 блок 16 установит через формирователь адресных сигналов младшие k-рлтрялов обрабатывае мого слова на инЬ рмационном входе

3U

первого накопителя 1, а старшие k- раэрядов - на информационном входе второго накопителя 2, при этом выход первого блока 15 находится в третьем состоянии, а на управляющий вход накопителей 1 и 2 через элемент ИЛИ 11 поступает сигнал Запись, При наличии сигнала Считывание на входе 32 на управляющих входах накопителей 1 и 2 сохраняется сигнал Считывание, а сигналом с выхода блока 16 разре- щается запись обрабатываемого слова с информационных выходов накопителей I и 2 в регистр 6 числа, при этом выход блока 20 находится в третьем состоянии. Оба канала работают независимо, обеспечивая высокое быстродействие устройства. При этом в зависимости от того, в каком канале обрабатывается информация, второй накопитель подключается либо последовательно, либо параллельно первому накопителю.

Формула изобретения

Многокаяальиое запоминающее устройство по авт. св. № 1251176, о т- личающееся тем, что, с целью повышения надежности и эффективной емкости устройства, в него введены второй накопитель, элемент И, элемент ИЛИ-НЕ, первый и второй блоки буферных формирователей сигналов, причем управляющий вход второго накопителя соединен с выходом элемента ИЛИ, первый выход первого формиро81I .

вателя адресньгх сигналов и ныход второго формирователя адресных сигналон подключены к адресному входу второго накопителя, второй выход первого формирователя адресных сигналов подключен к первым входам элемента И и элемента ИЛИ-НЕ, выход первого формирователя разрядных сигналов и первый

0 выход второго формирователя разрядных сигналов подключены к первому входу первого блока буферных формирователей сигналов, второй вход которого и второй вход элемента И подклю5 чены к выходу первого формирователя одиночных нмпульсов, вьгход первого блока буферньж формирователей сигналов и второй выход второго формирователя разрядных сигналов соединены

0 с информационным входом второго накопителя, выход второго блока буферных формирователей сигналов соединен с первым входом второго регистра числа, первьо) вход второго блока буфер5 ных формирователей сигналов и третий вход второго регистра числа подключены к информационному выходу второго накопителя, второй вход второго блока буферных формирователей сигна30 лов и второй вход элемента ИЛИ-НЕ подключены к выходу второго формирователя одиночных импульсов, выход элемента И подключен к входу обращения первого йакопителя, выход эле- 25 мента ИЛИ-НЕ соединен с третьим входом второго блока буферных формирователей сигналов и входом обращения второго накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное запоминающее устройство | 1984 |

|

SU1251176A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Многоканальное запоминающее устройство | 1981 |

|

SU953669A1 |

| Адресно-коммутационное устройство | 1987 |

|

SU1515378A1 |

| Запоминающее устройство с последовательным доступом | 1981 |

|

SU982084A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

Изобретение относится к вычислительной технике и может быть использовано в двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти. Цель изобретения - повышение надежности и эффективной емкости устройства в режиме работы в качестве общей оперативной памяти или устройства согласования k-разрядных и 2k-pa3- рядных процессоров или вычислительных машии. Для этого в устройство введены второй k-разрядный накопитель, элемент И, элемент ИЛИ-НЕ и блоки буферных формирователей сигналов. В зависимости от того, в каком канапе (k-разрядном или 2k-paзpяд- ном)обрабатывается информация, второй накопитель подключается либо последовательно, либо параллельно первому накопителю. 2 ил. (С (Л

| Многоканальное запоминающее устройство | 1984 |

|

SU1251176A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-08-23—Публикация

1985-10-29—Подача