Изобретение относится к вычислительной технике и может быть использовано в двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти.

Цель изобретения - упрощение устройства и повышение его быстродействия.

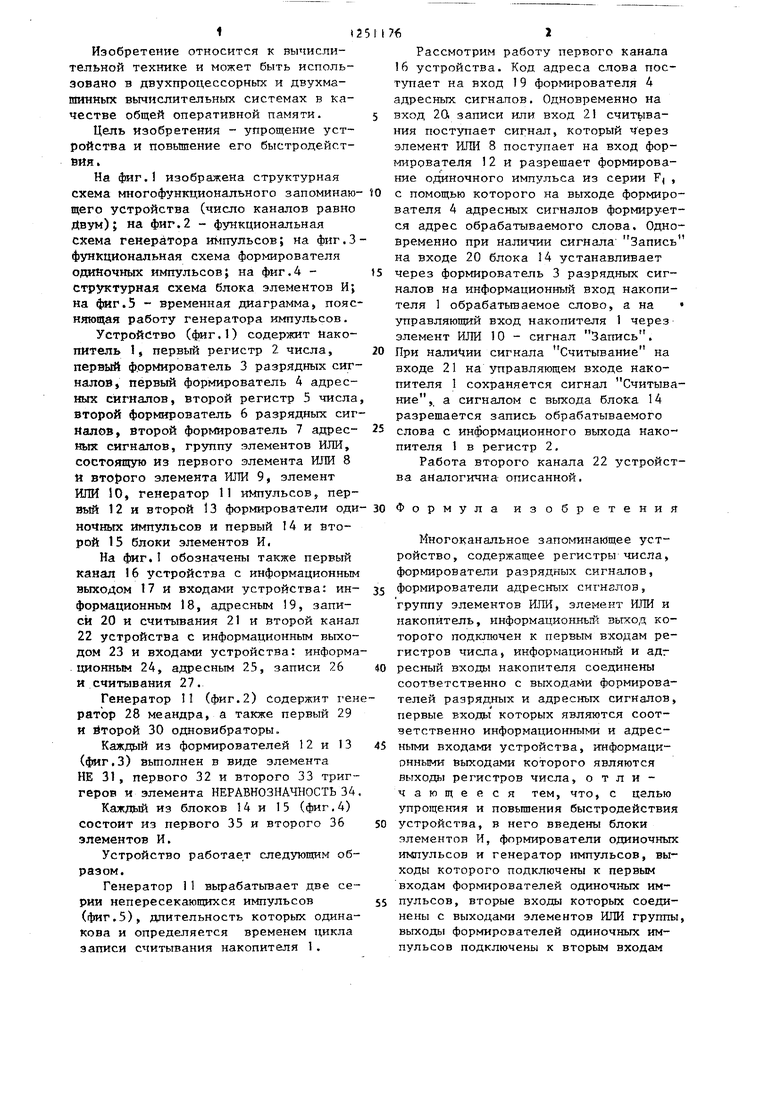

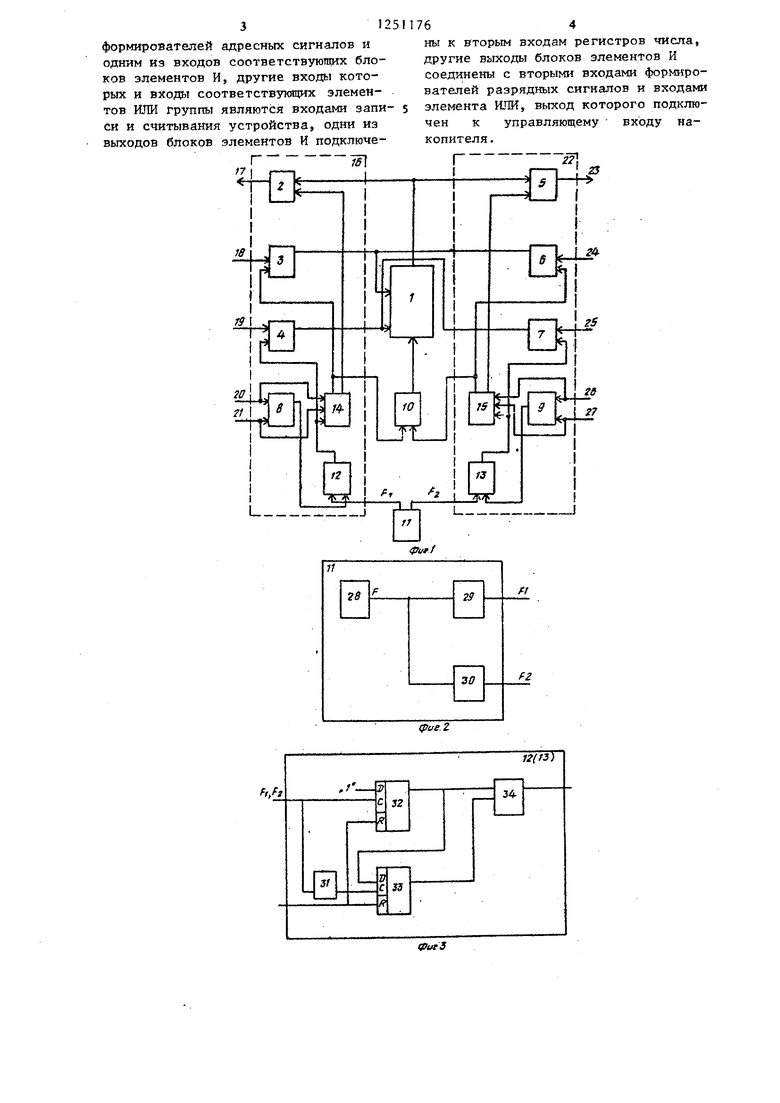

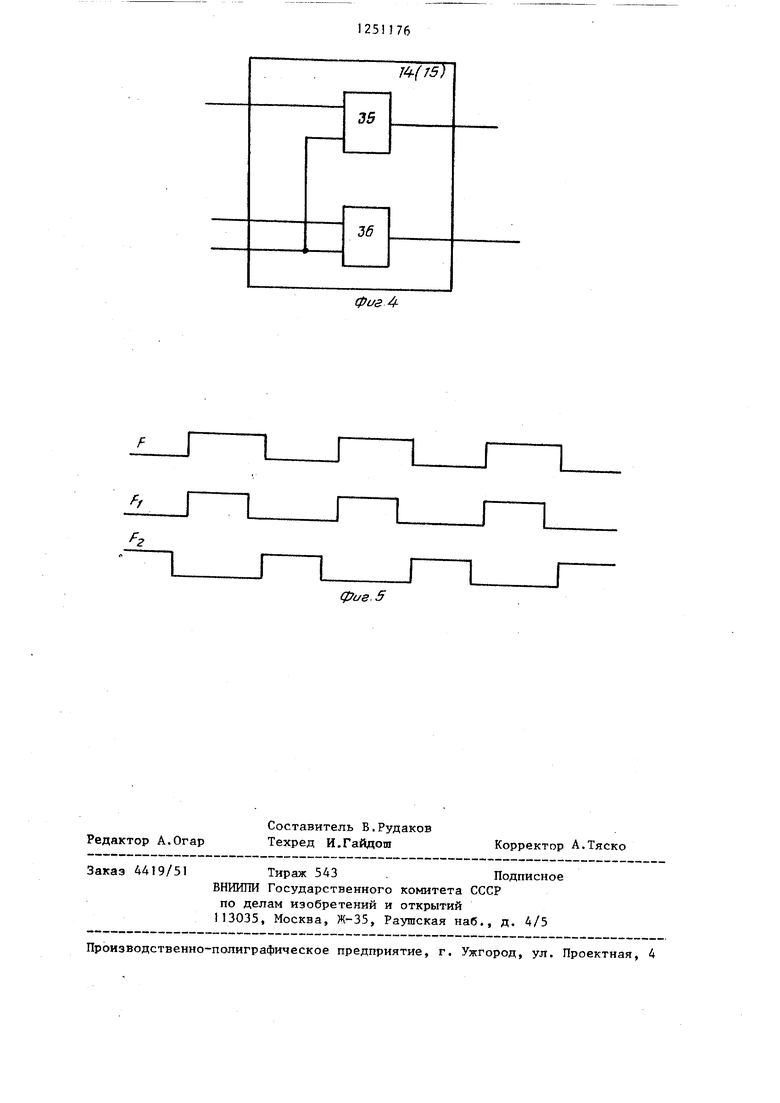

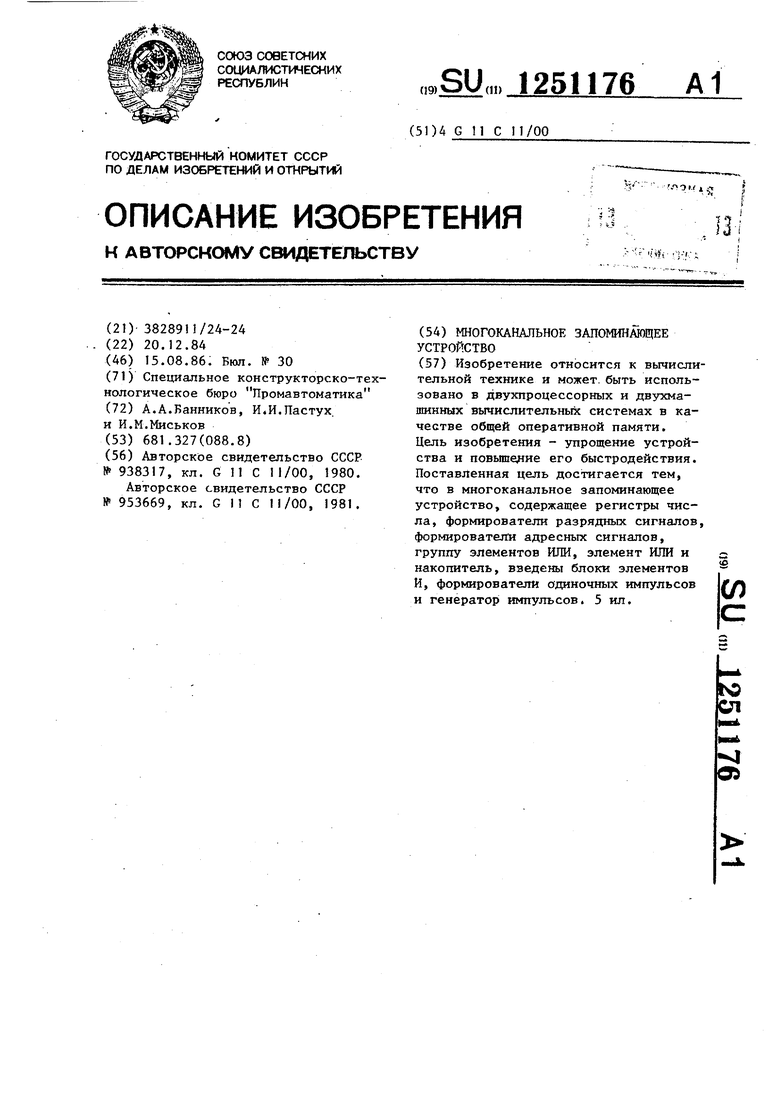

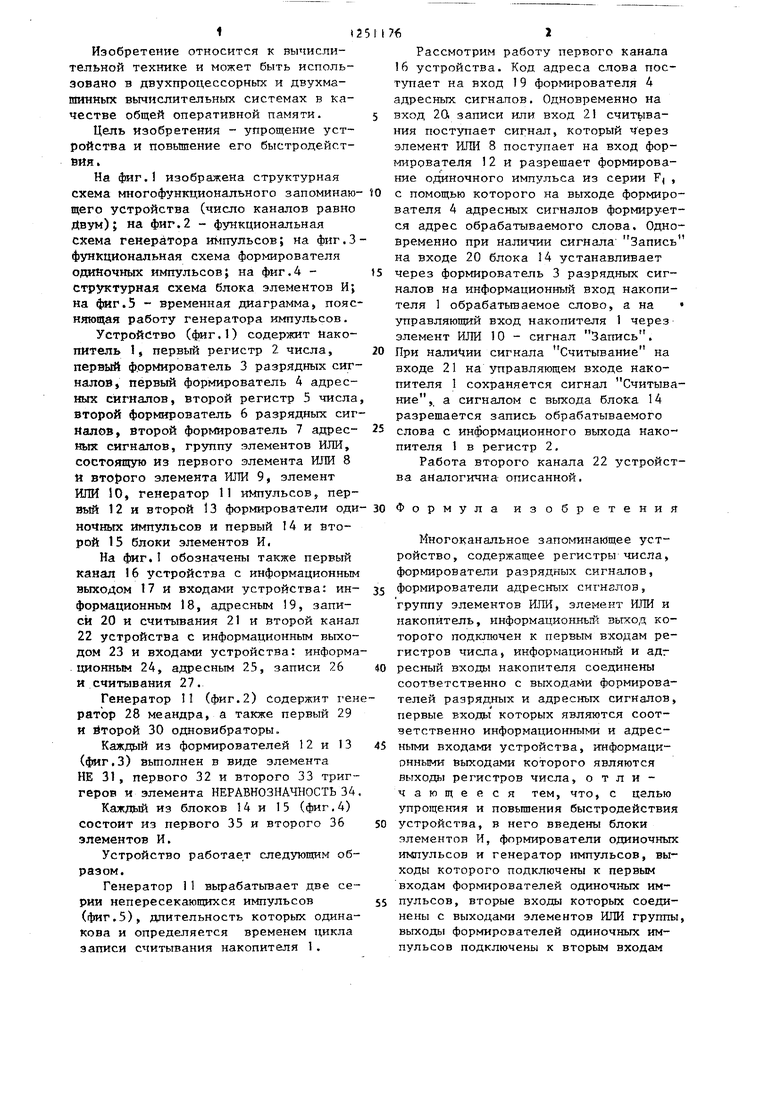

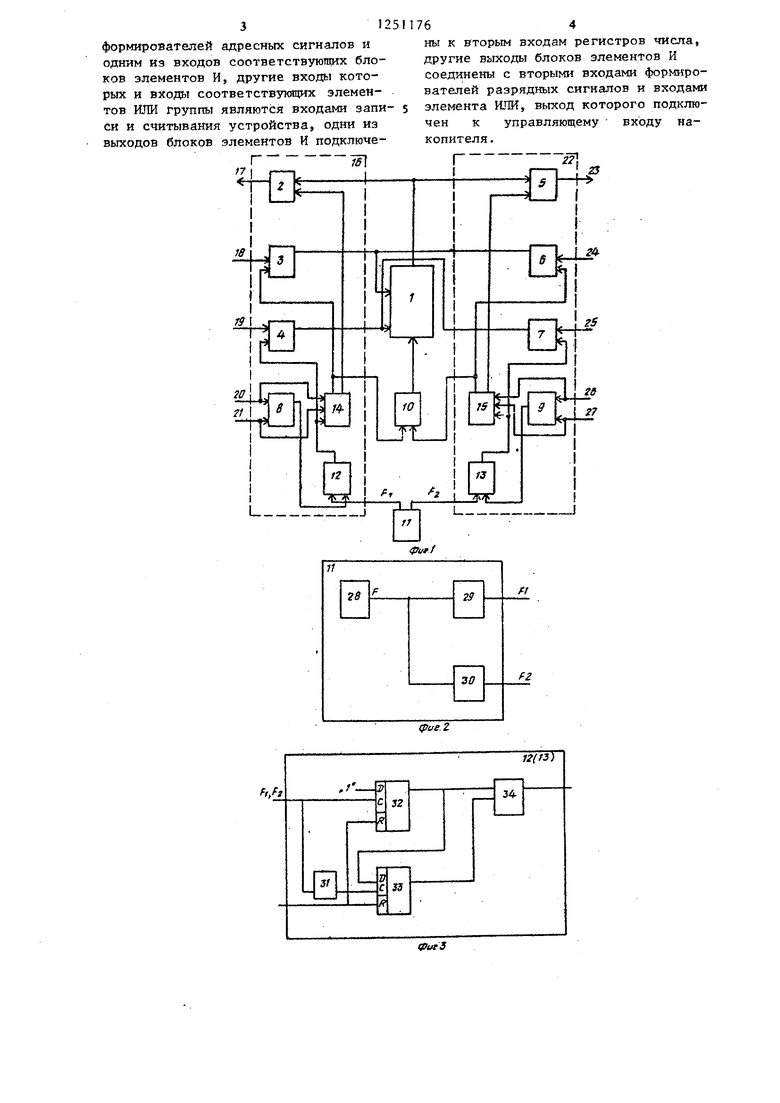

На фиг. изображена структурная схема многофункционального запоминаю- щего устройства (число каналов равно Двум); на фиг,2 - функциональная схема генератора импульсов; на фиг.3 функциональная схема формирователя одиночных импульсов; на фиг.4 - структурная схема блока элементов И; на фиг.5 - временная диаграммаj поясняющая работу генератора импульсов.

Устройство (фиг.1) содержит накопитель 1, первый регистр 2 числа, первый формирователь 3 разрядных сигналов, первый формирователь А адресных сигналов, второй регистр 5 числа второй формирователь 6 разрядных сиг Налов, второй формирователь 7 адрес- ных сигналов, группу элементов ИЖ, состоящую из первого элемента ИЛИ 8 и вто{)ого элемента ИЛИ 9, элемент ИЛИ 10, генератор 11 импульсов, первый 12 и второй 13 формирователя оди ночных импульсов и первый I4 и второй 15 блоки элементов И,

На фиг.1 обозначены также первый канал 16 устройства с информационным выходом 17 и входами устройства: ин- формационным 18, адресным 19, записи 20 и считьтания 21 и второй канал 22 устройства с информационным выходом 23 и входами устройства: информа . ционным 24, адресным 25, записи 26 и считывания 27.

Генератор П (фиг.2) содержит генратор 28 меандра, а также первый 29 и йторой 30 одновибраторы.

Каждый из формирователей 12 и 13 (фиг.З) вьшолнен в виде элемента НЕ 31, первого 32 и второго 33 триггеров и элемента НЕРАВНОЗНАЧНОСТЬ 34.

Каждый из блоков 14 и 15 (фиг,4) состоит из первого 35 и второго 36 элементов И.

Устройство работает следующим образом.

Генератор 11 вьфабатьгаает две серии непересекающихся импульсов (фиг.5), длительность которых одинакова и определяется временем цикла записи считывания накопителя 1.

762

Рассмотрим работу первого канала 16 устройства. Код адреса слова поступает на вход 19 формирователя 4 адресных сигналов. Одновременно на вход 2Q записи или вход 21 считывания поступает сигнал, который через элемент ИЛИ 8 поступает на вход формирователя 12 и разрешает формирование одиночного импульса из серии F( , с помощью которого на выходе формирователя 4 адресных сигналов формируется адрес обрабатываемого слова. Одновременно при наличии сигнала Запись на входе 20 блока 14 устанавливает через формирователь 3 разрядных сигналов на информационный вход накопителя 1 обрабатьшаемое слово, а на управляющий вход накопителя 1 через элемент ИЛИ 10 - сигнал Запись. При сигнала Считывание на входе 21 на управляющем входе накопителя 1 сохраняется сигнал Считывание,, а сигналом с выхода блока 14 разрешается запись обрабатываемого слова с информационного выхода накопителя 1 в регистр 2.

Работа второго канала 22 устройства аналогична описанной.

Формула изобретения

Многоканальное запоминающее устройство, содержащее регистры числа, формирователи разрядных сигналов, формирователи адресных сигналов, группу элементов ИЛИ, элемент ИЛИ и накопитель, информационный выкод которого подключен к первым входам регистров числа, информационный и адг ресный входь накопителя соединены соответственно с выходами формирователей разрядных и адресных сигналов, первые Бходьт которых являются соот- зетственно информационными и адресными входами устройства, информационными выходами которого являются выходы регистров числа, отличающееся тем, что, с целью упрощения и повышения быстродействия устройства, в него введены блоки элементов И, формирователи одиночных импульсов и генератор импульсов, выходы которого подключены к первым входам формирователей одиночных импульсов, вторые входы которых соединены с выходами элементов ИЛИ группы выходы формирователей одиночных импульсов подключены к вторым входам

формирователей адресных сигналов н одним из входов соответствуюптх блоков элементов И, другие входа которых и входы соответствующих элементов ИЖ группы являются входами записи и считывания устройства, одни из выходов блоков элементов И подключены к вторым входам регистров числа, другие выходы блоков элементов И соединены с вторыми входами формирователей разрядных сигналов и входами элемента ИЛИ, выход которого подключен к управляющему входу накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное запоминающее устройство | 1985 |

|

SU1418811A2 |

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Оперативное запоминающее устройство | 1984 |

|

SU1236551A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1580442A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

Изобретение относится к вычислительной технике и может, быть использовано в двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти. Цель изобретения - упрощение устройства и повьте ие его быстродействия. Поставленная цель достигается тем, что в многоканальное запоминающее устройство, содержащее регистры числа, формирователи разрядных сигналов, формирователи адресных сигналов, группу элементов ИЛИ, элемент ИЛИ и накопитель, введены блоки элементов И, формирователи одииочных импульсов и генератор импульсов. 5 ил. о (Л

fi

fZ

7V/5;

-J

фие S

Редактор А.Огар

Составитель В.Рудаков Техред И.Гайдош

Заказ 4419/51

Тираж 543 ,Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг 4

Корректор А.Тяско

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Многоканальное запоминающее устройство | 1981 |

|

SU953669A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-15—Публикация

1984-12-20—Подача