(/

fftad}

(Z)

ю

4

to

vl

Вл1х{т

8мж.СС

Изобретение относится к электросвязи и может использоваться в устройствах для оценки качества цифровых си стем передачи путем измерения ошибок, j возникающих в каналах связи при передаче дискретной информации в виде группового цифррвого потока с синхронизирующими кодовыми словами, а также для цикловой синхронизации цифровых /10 систем передачи.

Цель изобретения - расширение функциональных возможностей путем вьщеле- ния ошибок различной кратности при переменной длине цикла передачи сии- 15 хросигнала.

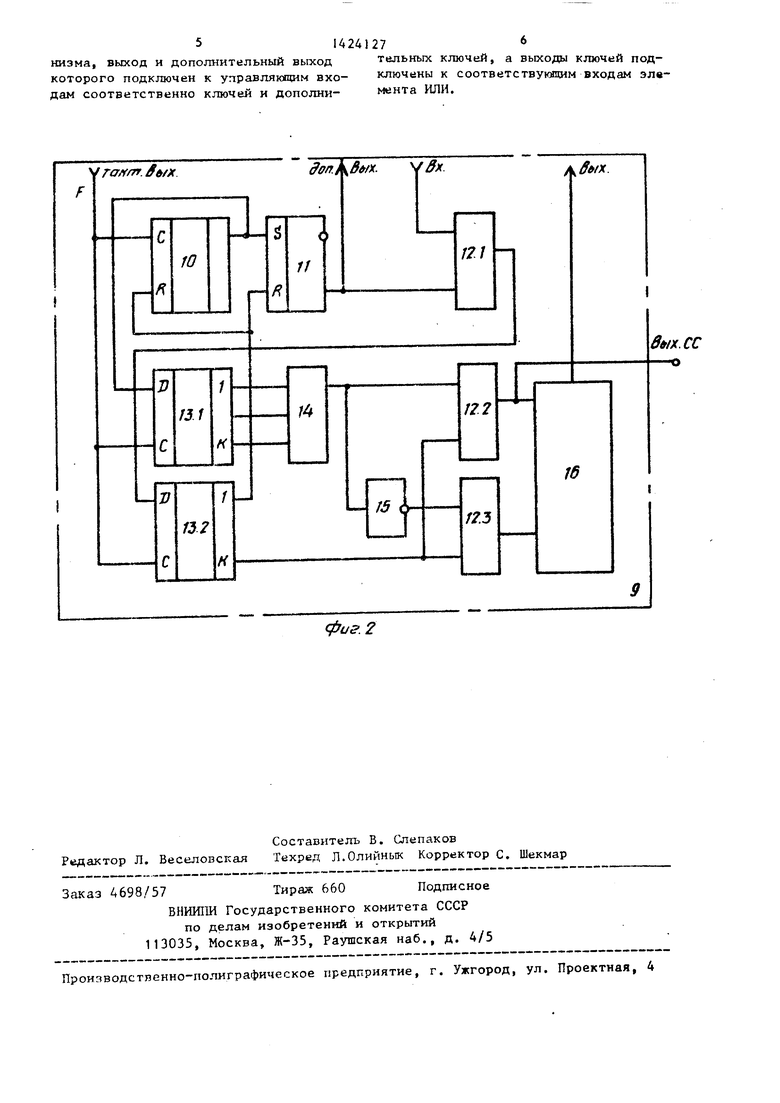

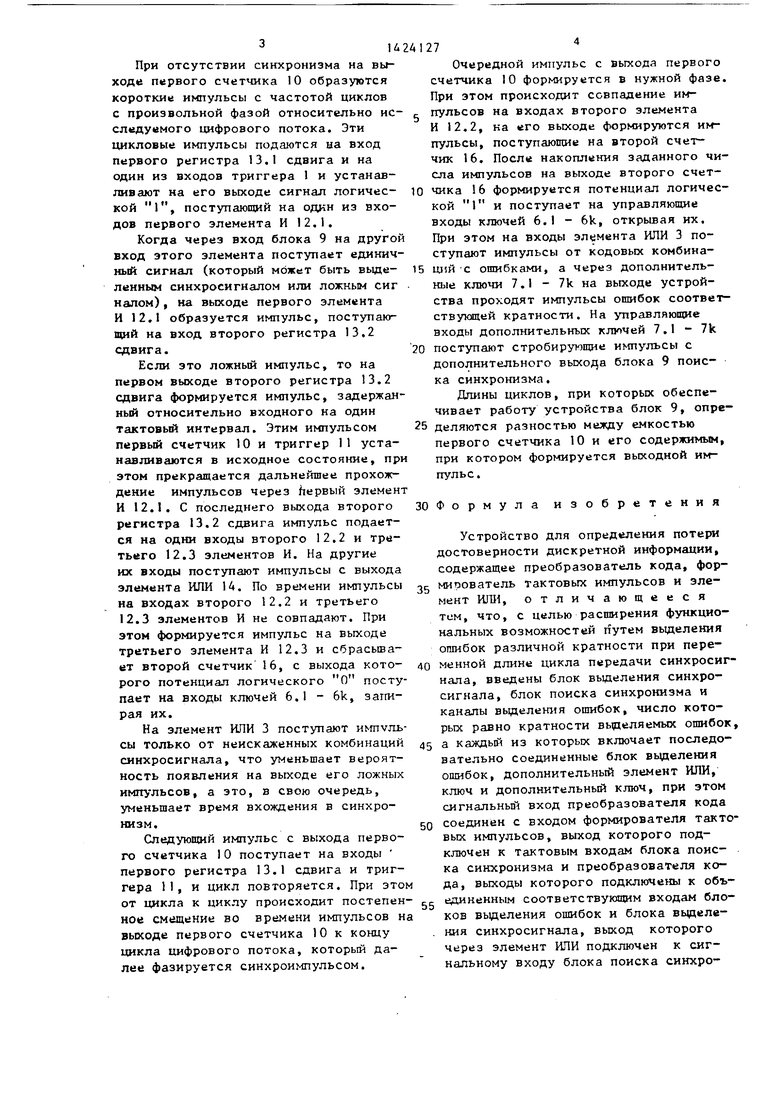

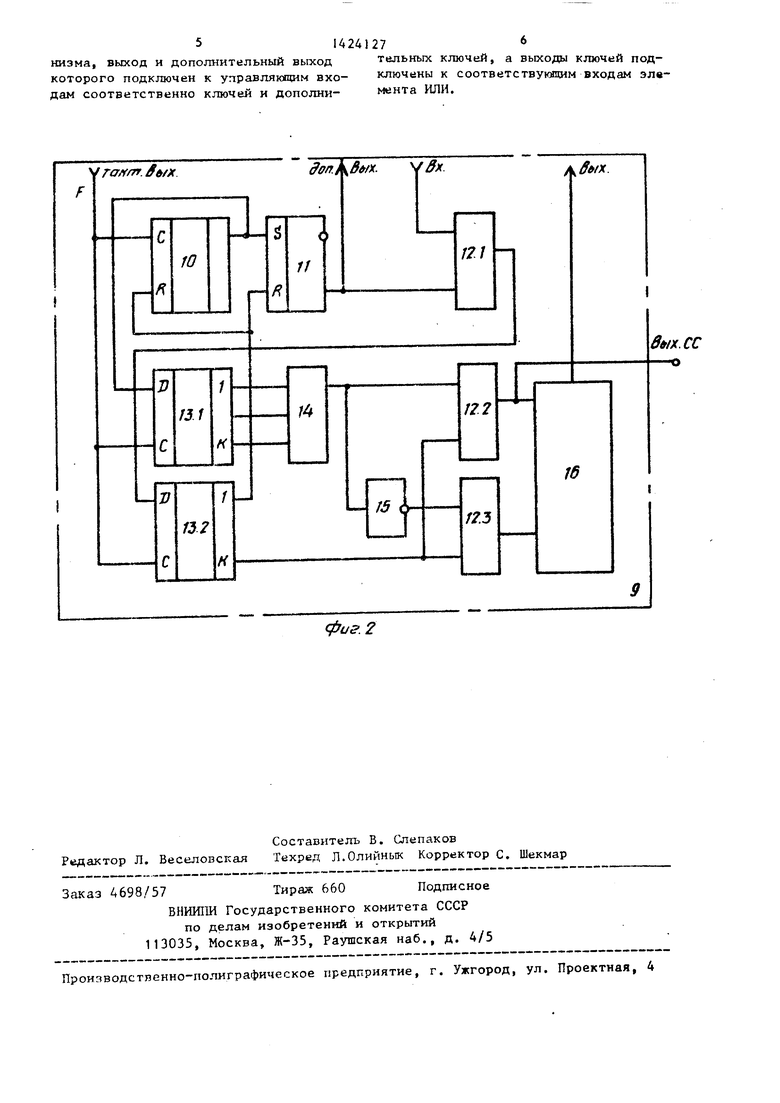

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - пример структурной электрической схемы блока по- 20 иска синхронизма.

Устройство для определения потери достоверности дискретной информации содержит преобразователь I кода, формирователь 2 тактовых импульсов, эле-25 мент ИЛИ 3, блоки 4.lT4k вьщеления ошибок, где k-максимальная кратность выделяемой ошибки, дополнительные элементы ИЛИ 5.1 - 5k, ключи 6.1 - 6k, дополнительные ключи 7. 7k, блок 30 8 выделения синхросигнала и блок 9 поиска синхронизма, включающий первый счетчик 10, триггер И, первый 12,1, второй 12.2.и третий 12.3 элементы И, первый 13.1 и второй 13.2 регистры 35 сдвига, элемент ИЛИ 14, инвертор 15 и второй счетчик 16.

Устройство работает следующим обра зом.

Исследуемый цифровой поток разделенно на циклы, в каждом из которых срдержит- ся М двоичных символов синхросигнала (СС), представляющего собой постоянный М-мврный вектор. Этот цифровой поток (его можно рассматривать как после-дз довательный код поступает на вход преобразователя 1 кода, в котором в каждый тактовый интервал умещается М .текущих символов потока, из которого одновременно формирователем 2 тактовых JQ импульсов вьадвляется регулярная последовательность коротких импульсов. Полученный после преобразования параллельный коды, или твкyщиtг М-мерные век торы, поступают одновременно на входы- блока 8 выделения синхросигнала (СС) блоков 4.1 - 4k вьщеления ошибок кратности 1,2k k не превышает К. В случае опознания СС на выхо-1

де блока 8 появляется короткий импулЬс длительностью в тактовый интервал, а в случае опознания ошибки любой кратности такой импульс возникает на одном из выходов одного из блоков 4. Сигналы сшибок одной кратности суммируются во времени соответствующим дополнительным элементом ИЛИ 5 и подаются на соответствующий ключ 6, управляющий сигнал для которого формирует блок 9 поиска синхронизма. Для этого тактовые импульсы подаются на вход первого счетчика 10 и на тактовые входы первого 13.1 и второго 13.2 регистров сдвига.

Первый счетчик 10 осуществляет под- счет тактовых импульсов, и при достижении заданного значения, определяемого длительностью цикла, на выходе первого счетчика 10 формируется короткий импульс, устанавливающий триггер 11 в состояние и записьшаемый в первый регистр 13.1 сдвига. Записанный импуль с помощью тактовых импульсов продвигается по выходам первого регистра 13.1 и подается на соответствующие входы элемента ИЛИ 14, На выходе элемента ИЛИ 14 формируется импульс, длительность которого равна времени прохождения импульса по выходам первого регистра 13.1 сдвига.

Потенциал логической 1 с выхода триггера 11 поступает на один из входов первого элемента И 12.1 и разреша ет прохождение через него импульсов, поступивших на другой его вход. Импульс с выхода первого элемента Ч 12.1 записьшается во второй регистр 13,2 сдвига, и с первого его выхода поступает на установочные входы первого счетчика 10 и триггера 11, устанавливая их в исходное состояние. С noc-i леднего выхода второго регистра 13.2 сдвига импульс поступает на одни входы второго 12.2 и третьего 12,3 элементов И, на другие входы которых поступает импульс с выхода элемента ИЛИ 14 (на вход второго элемента И 12.2 - непосредственно, а на вход третьего элемента И 12.3 - через инвертор 15). При совпадении по времени импульсов на входах второго элемента И 12.2 на его выходе формируется сигнал наличия СС, являющийся импульсом для второго счетчика 16, а при несовпадении формируется импульс на выходе третьего элемента И 12,3, которым осуществляется сброс второго счетчика 16.

К

При отсутствии синхронизма на выходе первого счетчика 10 образуются короткие импульсы с частотой циклов с произвольной фазой относительно ис- следуемого цифрового потока. Эти цикловые импульсы подаются на вход первого регистра 13.1 сдвига и на один из входов триггера 1 и устанавливают на его выходе сигнал логической 1, поступающий на один из входов первого элемента И 12.1.

Когда через вход блока 9 на другой вход этого элемента поступает единичный сигнал (который может быть вьще- ленным синхросигналом или ложным сиг налом), на выходе первого элемента И 12.1 образуется импульс, поступающий на вход второго регистра 13.2 сдвига.

Если это ложный импульс, то на первом выходе второго регистра 13.2 сдвига формируется импульс, задержанный относительно входного на один тактовый интервал. Этим импульсом первый счетчик 10 и триггер 11 устанавливаются в исходное состояние, при этом прекращается дальнейшее прохождение импульсов через первый элемент И 12.1. С последнего выхода второго регистра 13.2 сдвига импульс подается на одни входы второго 12.2 и третьего 12.3 элементов И. На другие их входы поступают импульсы с выхода элемента ИЛИ 14. По времени импульсы на входах второго 12.2 и третьего 12.3 элементов И не совпадают. При этом формируется импульс на выходе третьего элемента И 12.3 и сбрасьша- ет второй счетчик 16, с выхода которого потенциал логического О поступает на входы ключей 6.1 - 6k, запирая их.

На элемент ИЛИ 3 поступают иьтуль сы только от неискаженных комбинаций синхросигнала, что уменьшает вероятность появления на выходе его ложных импульсов, а это, в свою очередь, уменьшает время вхождения в синхронизм.

Следующий импульс с выхода первого счетчика 10 поступает на входы первого регистра 13.1 сдвига и триггера 11, и цикл повторяется. При это от цикла к циклу происходит постепенное смедение во времени импульсов н выходе первого счетчика 10 к концу цикла цифрового потока, который далее фазируется синхроимпульсом.

7

Очередной импульс с выхода первого счетчика 10 формируется в нужной фазе. При этом происходит совпадение импульсов на входах второго элемента И 12.2, на его выходе формируются импульсы, поступающие на второй счетчик 16. После накопления заданного числа импульсов на выходе второго счетчика 16 формируется потенциал логической 1 и поступает на управляющие входы ключей 6.1 - 6k, открьшая их. При этом на входы эл1ймента ИЛИ 3 поступают импульсы от кодовых комбинаЩ5Й-с ошибками, а через дополнительные ключи 7.1 - 7k на выходе устройства проходят импульсы ошибок соответствующей кратности. На управляющие входы дополнительных ключей 7.1 - 7k

поступают стробирующие импульсы с дополнительного выхода блока 9 поиска синхронизма.

Длины циклов, при которых обеспечивает работу устройства блок 9, опре-

деляются разностью между емкостью первого счетчика 10 и его содержимым, при котором формируется выходной импульс.

Формула изобретения

Устройство для определения потери достоверности дискретной информации, содержащее преобразователь кода, фор- мирователь тактовых импульсов и элемент ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей путем вьоделения ошибок различной кратности при переменной длине цикла передачи синхросигнала, введены блок выделения синхросигнала, блок поиска синхронизма и каналы вьщеления ошибок, число которых равно кратности вьделяемых ошибок, а каждый из которых включает последо- соединенные блок выделения ошибок, дополнительный элемент ИЛИ, ключ и дополнительный ключ, при этом сигнальньш вход преобразователя кода соединен с входом формирователя такте- вых импульсов, выход которого подключен к тактовым входам блока поиска синхронизма и преобразователя кода, выходы которого подключены к объединенным соответствующим входам блоков выделения ошибок и блока вьщеления синхросигнала, выход которого через элемент ИЛИ подключен к сигнальному входу блока поиска синхро

514241276

низма, выход и дополнительный выходтельных ключей, а выходы ключей подкоторого подключен к управляющим вхо- ключены к соответствукяцим входам элв- дам соответственно ключей и дополни-мента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник синхросигнала | 1986 |

|

SU1424129A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ФЕРРОМАГНИТНЫХ ЧАСТИЦ ИЗНОСА В МАСЛЕ | 1997 |

|

RU2131552C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| Устройство синхронизации по циклам | 1976 |

|

SU618858A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

Изобретение относится к электросвязи. Цель изобретения - расширение функциональных возможностей. Устр-во содержит преобразователь 1 кода, формирователь 2 тактовых импульсов, эл-т ИЛИ 3, блок вццеления 8 синхросигнала, блок поиска 9 синхронизма и каналы вьщеления ошибок, каждый из которых состоит из блока выделения 4 ошибок, эл-та ИЛИ 5 и ключей 6 и 7. Цель достигается путем обеспечения вццеления ошибок различной кратности при переменной длине цикла передачи синхросигнала с помощью введенных блока выделения 8, блока поиска 9 и каналов вьделения ошибок. 2 ил.

ffon.t . /8х

If

J31

/4

фиг. 2

/ k

.

/7/

вш.СС -о

122

16

/S

Л

Г2.Ъ

| Мартынов Е | |||

| М | |||

| Синхронизация в системах передачи дискретных сообщений | |||

| М.; Связь, 1972, с | |||

| Поршень для воздушных тормозов с сжатым воздухом | 1921 |

|

SU188A1 |

| Устройство для определения потери достоверности при передаче цифровой информации по линии связи | 1975 |

|

SU559401A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| с | |||

Авторы

Даты

1988-09-15—Публикация

1986-04-23—Подача