00

:&

Изобретение относится к микроэлектронике и может быть использовано при разработке реп рограммируемых постоянных запоминающих устройств большой информационной емкости.

Цель изобретения - увеличение времени хранения информации и количества циклов перепрограммирования.

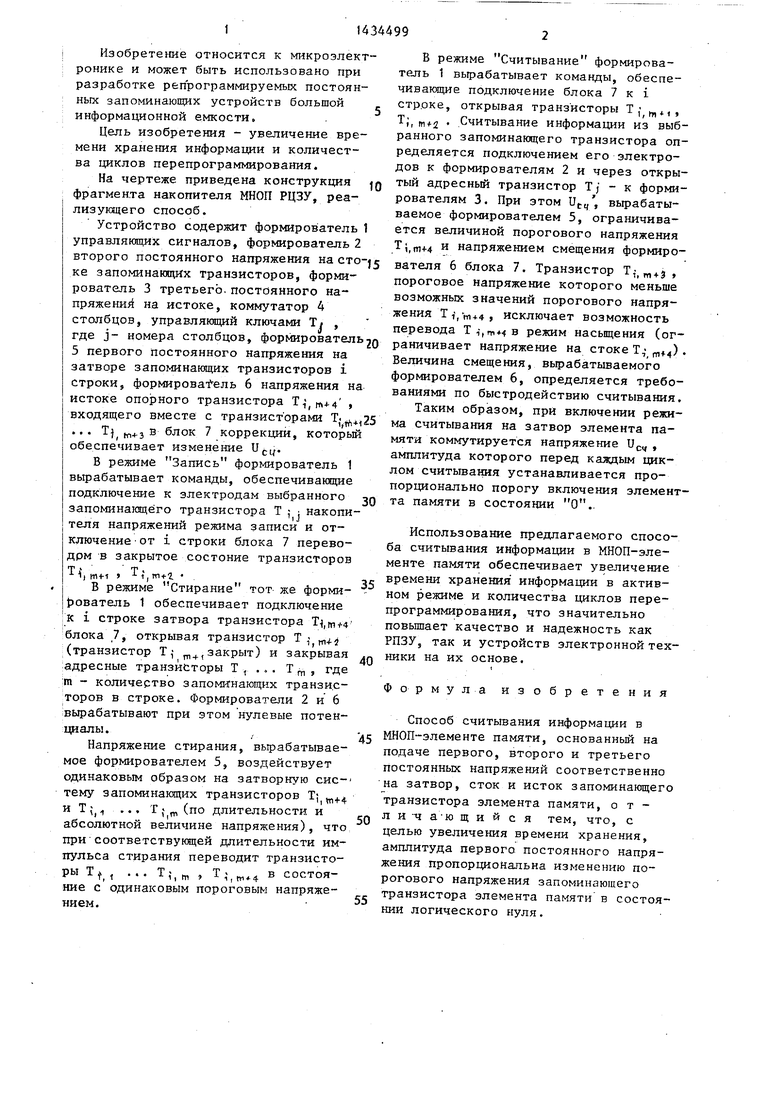

На чертеже приведена конструкция фрагмента накопителя МНОП РЦЗУ, реа- лизукщего способ.

Устройство содержит формирователь управлякицих сигналов, формирователь 2 второго постоянного напряжения на CTO ке запоминающих транзисторов, формирователь 3 третьего, постоянного напряжение} на истоке, коммутатор 4 столбцов, управляняций ключами Ti , где J- номера столбцов, формирователь 5 первого постоянного напряжения на затворе запоминакяцих транзисторов i строки, формирова- ель 6 напряжения на истоке опорного транзистора .4 , входящего вместе с транзисторами Т.. ... Т) ,,,4.3 в блок 7 коррекции, которьй обеспечивает изменение Uj..

В режиме Запись формирователь 1 вьфабатывает команды, обеспечиванлще подключение к электродам выбранного запоминакадёго транзистора Т ,- i накопителя напряжений режима записи и отключение от i строки блока 7 перево- дрм в закрытое состоние транзисторов

) ПИ-1 9 T,.2, .

в режиме Стирание тот же форми- {эователь 1 обеспечивает подключение к i строке затвора транзистора T,tnt4 блока ,7 открывая транзистор Т,-

(транзистор Т,- ,„, закрыт) и закрывая :адресные транзисторы Т , .. Т f Д :т - количество запоминающих транзисторов в строке. Формирователи 2 и 6 :вьфабатывают при этом нулевые потенциалы.,

Напряжение стирания, вырабатываемое формирователем 5, воздействует одинаковым образом на затворную сие- тему запоминагацих транзисторов TI. и Tjj ... Т; (по длительности и абсолютной величине напряжения), что при соответствуняцей длительности импульса стирания переводит транзисто- рыТ, ... Т,-, , Т-,, в состояние с одинаковым пороговым напряжением.

g

о 5

0

0

с

5

В режиме Считывание формирователь 1 вырабатывает команды, обеспе- чивакицие подключение блока 7 к i строке, открывая транзисторы Т; f,, Т;, ,2 Считывание информации из выбранного запоминающего транзистора определяется подключением его электродов к формирователям 2 и через открытый адресный транзистор Tf - к формирователям 3. При этом Utt,, вьфабаты- ваемое формирователем 5, ограничивается величиной порогового напряжения и напряжением смещения формирователя 6 блока 7. Транзистор T,- + j , пороговое напряжение которого меньше возможных значений порогового напряжения Т у, , исключает возможность перевода режим насыщения (ограничивает напряжение на стоке Т,- 44) Величина смещения, вырабатываемого формирователем 6, определяется требованиями по быстродействию считывания.

Таким образом, при включении режима считывания на затвор элемента памяти коммутируется напряжение U,, , амплитуда которого перед каждым циклом считьшаиия устанавливается пропорционально порогу включения элемент- та памяти в состоянии О..

Использование предлагаемого способа считывания информации в МНОП-эле- менте памяти обеспечивает увеличение времени хранения информации в активном режиме и количества циклов перепрограммирования, что значительно повьшает качество и надежность как РПЗУ, так и устройств электронной техники на их основе.

I

Формула изобретения

Способ считывания информации в МНОП-элементе памяти, основанньй на подаче первого, второго и третьего постоянных напряжений соответственно на затвор, сток и исток запоминающего транзистора элемента памяти, о т - л и -ч а-ю щ и и с я тем, что, с целью увеличения времени хранения, амплитуда первого постоянного напряжения пропорциональна изменению порогового напряжения запоминающего транзистора элемента памяти в состоянии логического нуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ считывания информации из элементов памяти на полевых транзисторах и формирователь сигналов считывания | 1989 |

|

SU1697118A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Ячейка памяти для ОЗУ с энергонезависимым хранением информации (ее варианты) | 1982 |

|

SU1161989A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ НА МДП-ТРАНЗИСТОРАХ С ИЗМЕНЯЕМЫМ ПОРОГОВЫМ ВКЛЮЧЕНИЕМ | 1985 |

|

RU1378681C |

Изобретение относится к микроэлектронике и может быть использовано при разработке репрограммируемых постоянных запоминагацих устройств. Целью изобретения является увеличение времени хранения информации и количества циклов перепрограммирования МНОП-элемента памяти. Поставленная цель достигается тем, что амплитуда напряжения считывания пропорциональна пороговому напряжению запоминаю- ,щего транзистора злемента памяти в состоянии логического нуля. 1 ил.

| Электроника, 1981, № 4, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

Авторы

Даты

1988-10-30—Публикация

1986-09-23—Подача