Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ (электронных вычислительных машин) с повышенной надежностью.

Цель изобретения - сокращение объема оборудования устройства.

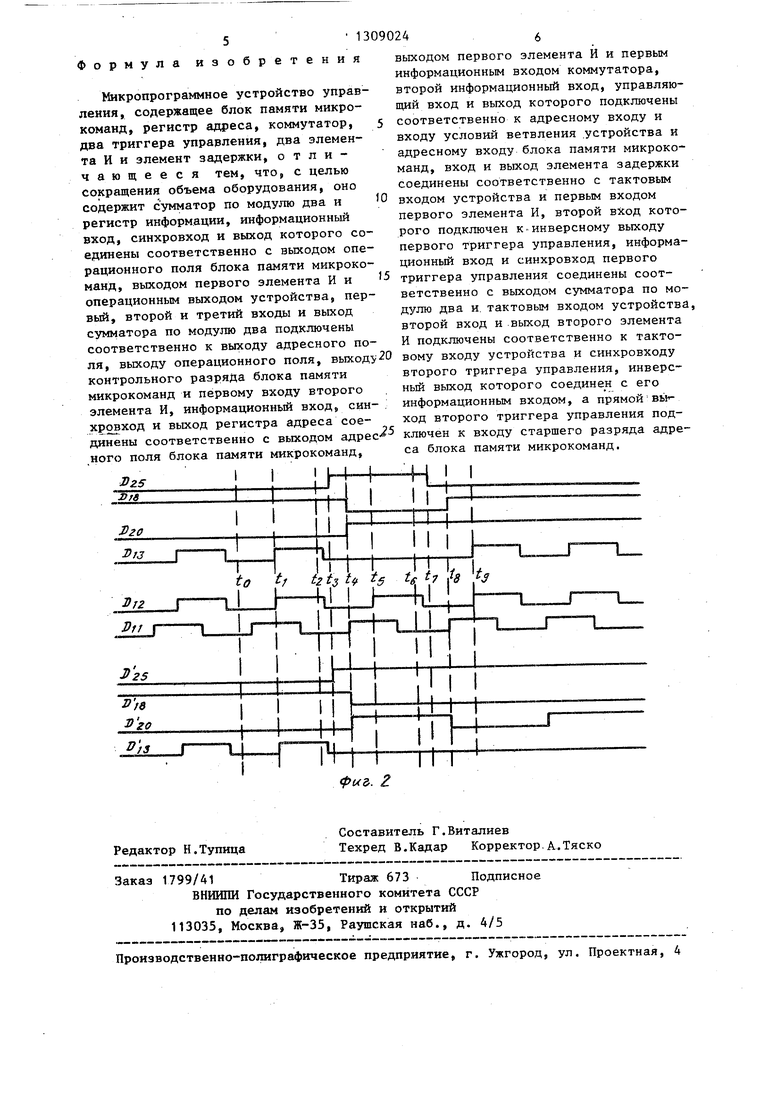

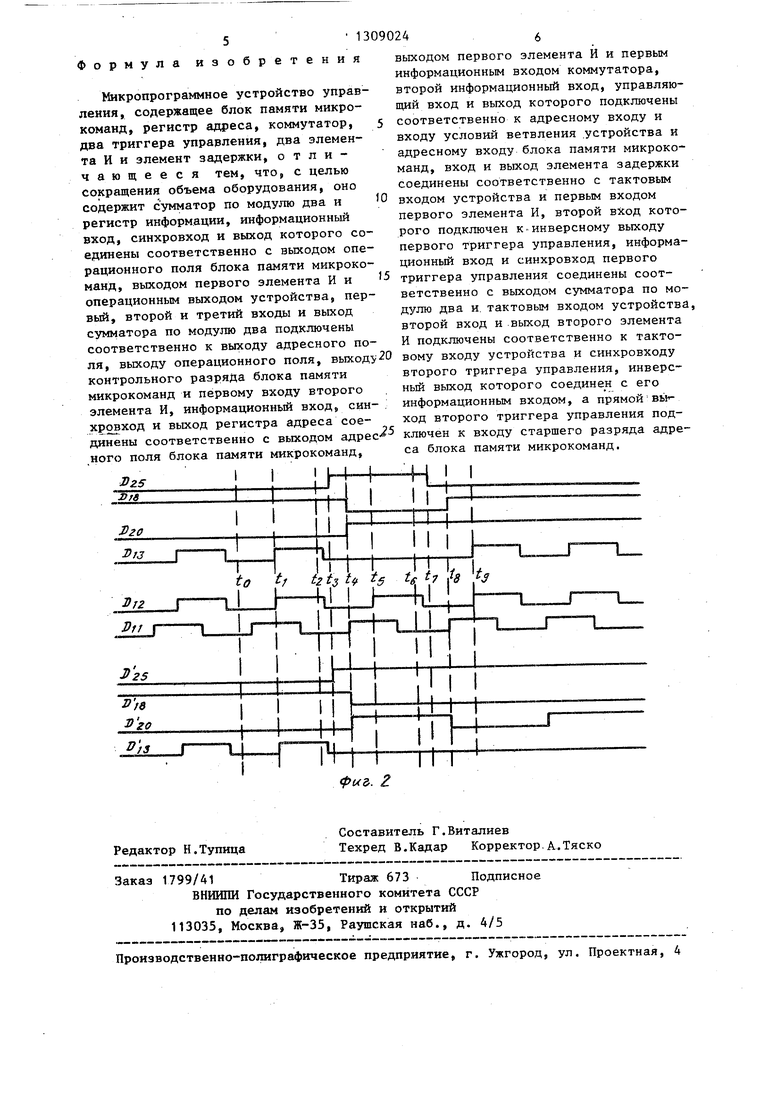

На фиг.1 представлена функциональная схема устройства; на фиг,2 - временная диаграмма работы устройства.

Устройство (фиг.1) содержит элемент 1 задержки, первый элемент И2, регистр 3 сдвига, второй элемент И4, первый триггер 5 управления, коммутатор 6, второй триггер 7 управления, блок 8 памяти микрокоманд, сумматор 9 по модулю два,, регистр 10 информации и имеет тактовый, вход 11 устройства, выход 12 элемента 1, выход 13 элемента 2, выход 14 регистра 3, адресный вход 15 устройства, вход 16 условий ветвления устройства, выход 17 элемента 4, инверсный выход 18 триггера 5, выход 19 коммутатора.6,

гистр принимается адресная часть сле дующей исправной микрокоманды. Элемент 4 предназначен для управления перебросом триггера 7 в противополож

5 ное состояние в зависимости от значе ния сигнала неисправности Триггер 5 служит для запирания (отпирания) элемента 2 установкой в единичное (нулевое) состояние по переднему

JO фронту тактовых импульсов D при наличии на информационном входе единич ного (нулевого) сигнала неисправное- ти П„.

Коммутатор 6 предназначен для подачи начального адреса микропрограмм на вход блока 8, а также модификации адресной части микрокоманды в зависи мости от условий ветвления и ее пода чи на вход блока 8, Коммутатор пред20 ставляет собой группу трехвходовых элементов ИЛИ, количество которых оп ределяется разрядностью адресной час ти микрокоманды. Триггер 7 служит для инвертирования старшего адресног

15

прямой (единичный) выход 20 и инверс- разряда блока 8 по переднему фронту

ный (нулевой) выход 21 триггера 7, вьгход 22 адресного поля, выход 23 операционного поля и выход 24 контрольного разряда блока 8, выход 25 сигнала неисправности сумматора 9, операционный выход 26 устройства.

Временные диаграммы (фиг,2) показывают динамику логических уровней на соответствующих входах и выходах устройства. Например, D , - временная диаграмма логического уровня на выходе 13 элемента 2, Диаграммы D D|g, , D., показывают работу устройства при отказе основной микрокоманды с последущим чтением исправной резервной микрокоманды, а диаграммы D , D|g, Вщ, D , - при отказе и исновной, и резервной микрокоманд.

Элемент 1 задержки предназначен для задержки тактовых импульсов D, на время, необходимое для переброса триггера 5 в единичное (нулевое) состояние и надежного запирания (отпирания) элемента 2, Элемент 2 предназначен для блокировки поступления тактовых импульсов D,2 на синхровходы регистров 3 и 10 в случае, когда триггер 5 находится в единичном состоянии. Регистр 3 необходим для приема адресной части исправной микрокоманды по переднему фронту импульса D,j и хранения ее до поступления следующего . импульса DIJ, по которому в этот регистр принимается адресная часть следующей исправной микрокоманды. Элемент 4 предназначен для управления перебросом триггера 7 в противоположное состояние в зависимости от значения сигнала неисправности Триггер 5 служит для запирания (отпирания) элемента 2 установкой в единичное (нулевое) состояние по переднему

фронту тактовых импульсов D при наличии на информационном входе единичного (нулевого) сигнала неисправное- ти П„.

Коммутатор 6 предназначен для подачи начального адреса микропрограммы на вход блока 8, а также модификации адресной части микрокоманды в зависимости от условий ветвления и ее подачи на вход блока 8, Коммутатор представляет собой группу трехвходовых элементов ИЛИ, количество которых определяется разрядностью адресной части микрокоманды. Триггер 7 служит для инвертирования старшего адресного

разряда блока 8 по переднему фронту

тактового импульса D, всякий раз, когда элемент А отпирается единичным сигналом неисправности D . Блок 8 необходим для хранения и вьщачи микрокоманд.

При наличии нулевого сигнала на входе старшего разряда адреса считывается основная микрокоманда, а при наличии единичного сигнала - резерв- наяо Блок 8 можно реализовать на микросхемах постоянных программируемых ЗУ, таких как РТ4, РТ5, РТ7, Сумматор

9предназначен для проверки на четность числа единиц в микрокоманде.

При четном числе единиц на выходе 25 вырабатывается нулевой сигнал а в случае нечетного - единичный. Сумматор 9 можно реализовать, например, на микросхемах ИП2 или Ш15. Регистр

10предназначен для приема и хранения информационной части исправной микрокоманды и подачи ее на выход устройства. Устройство может начать работу независимо от состояния триггеров 5

и 7 и значения сигнала неисправности на выходе 25 сумматора 9,

Примем, что к моменту времени t (фиг,1 и 2) из. блока 8 считана исправ- ная основная микрокоманда (по адресу с нулевым старшим разрядом), вследствие чего сигнал неисправности имеет, нулевое значение, а триггеры 5 н 7 находятся в нулевом состоянии.

Тогда в момент времени t, по переднему фронту импульсов D, считанная основная микрокоманда принимается- в регистры 3 и 10, так как элемент 2 отк-. рыт единичным сигналом с нулевого вы- 5 хода 18 триггера 5. Информационная часть микрокоманды поступает на выход 26 устройства, а адресная часть микрокоманды с выхода 14 регистра 3 поступает в коммутатор 6, где вьфабатыва О ется адрес следующей микрокоманды, который с выхода 19 поступает на адресный вход блока 8. Так как триггер

7находится в нулевом состоянии, то на его выходе 20

нал, и в момент времени

8считывается следующая микрокоманда по адресу с нулевым старшим разрядом и поступает на входы регистров 3 и 10

и сумматора 9.20

Если микрокоманда не искажена, то в момент времени t считывается следующая микрокоманда, если же микрокоманда искажена, то в момент времени

в регистры 3 и 10, и работа устройства продолжается аналогично работе с момента времени t( с той разницей, что в последующих тактах считываются резервные микрокоманды (по адресам с единичным старшим разрядом) до первой неисправной микрокоманды, после чего считываются основные микрокоманды (по адресам с нулевым старщим разрядом), и т.д.

Если повторно считанная резервная микрокоманда тоже искажена, работа устройства продолжается согласно ди- имеется нулевой сиг- 5 аграммам D., D , D, D/g. В момент

tj из блока

времени t изменении не происходит, так как на выходе 25 сумматора 9 сохраняется единичный сигнал. Элемент 4 остается открытым, и в момент времени tg по переднему фронту тактового импульса D,, триггер 7 перебрасывается в нулевое состояние, а триггер 5 состояние не изменяет, вследствие чего элемент 2 остается запертым. Поэтому - в момент времени t приема искаженной резервной микрокоманды в регистры з и 10 не происходит. Устройство прекращает работу, так как при отказе основной и резервной микрокоманд на выходе 25 сумматора 9 постоянно присутствует единичный сигнал неисправности. Триггер 5 остается в единичном состоянии, а элемент 2 остается запертым, блокируя прием искаженных в регистры 3 и 10.

оде 25 сумматора 9 вырабаты

иничный сигнал неисправности, ий на информационный вход 5 и отпирающий элемент 4. е этого в момент времени t 5 и 7 устанавливаются в еди-- стояние по переднему фронту импульса D,. Элемент 2 занулевым сигналом с нулевого триггера 5, вследствие чего времени

нды в регистры 3 и 10 н проОдновременно из блока 8 счирезервная микрокоманда, так ходе 20 триггера 7 имеется

tj приема искаженной 35 микрокоманд

времени t так как на раняется ед остается от tg по перед пульса D,, т в нулевое с тояние не и элемент 2 о - в момент вр резервной м и 10 не про кращает раб основной и выходе 25 с сутствует ед ности. Триг состоянии, а пертым, блок

40

Предлагае такой же уст и известное сбое основно ды считывает а основная ( В случае сбо микрокоманды ная (резервн рокоманд пре и известное, обязательно этом предлаг продолжать р шего количес устройство д сбою при чте -.мяти. Кроме памяти извес дополнительн считывания з команды.

единичньш сигнал, и к моменту времени t, она поступает на выход блока 8.

о

Если повторно считанная резервная микрокоманда не искажена, работа устройства продолжается согласно диаг-.

ранмам D , D

25

l&

Д

20

25

D,j. В момент време

ни t на выходе 25 сумматора 9 восстанавливается нулевой сигнал, вновь запирающий элемент 4 и поступающий на информационный вход триггера 5. Тогда в момент времени tg по передне му фронту тактового импульса D, триггер 5 устанавливается в нулевое состояние, отпирая элемент 2. Триггер 7 остается в прежнем состоянии,.благодаря чему сохраняется единичное значение старшего разряда адреса блока 8 на выходе 20. В момент времени ty резервная микрокоманда принимается

244

в регистры 3 и 10, и работа устройства продолжается аналогично работе с момента времени t( с той разницей, что в последующих тактах считываются резервные микрокоманды (по адресам с единичным старшим разрядом) до первой неисправной микрокоманды, после чего считываются основные микрокоманды (по адресам с нулевым старщим разрядом), и т.д.

20

, -

35 микрокоманд

времени t изменении не происходит, так как на выходе 25 сумматора 9 сохраняется единичный сигнал. Элемент 4 остается открытым, и в момент времени tg по переднему фронту тактового импульса D,, триггер 7 перебрасывается в нулевое состояние, а триггер 5 состояние не изменяет, вследствие чего элемент 2 остается запертым. Поэтому в момент времени t приема искаженной резервной микрокоманды в регистры з и 10 не происходит. Устройство прекращает работу, так как при отказе основной и резервной микрокоманд на выходе 25 сумматора 9 постоянно присутствует единичный сигнал неисправности. Триггер 5 остается в единичном состоянии, а элемент 2 остается запертым, блокируя прием искаженных в регистры 3 и 10.

40

45

Предлагаемое устройство обладает такой же устойчивостью к сбоям, что и известное устройство, так как при сбое основной (резервной) микрокоманды считывается резервная (основная), а основная (резервная) не бракуется. В случае сбоя резервной (основной) микрокоманды опять считьшается основная (резервная), т.е. при сбоях микрокоманд предлагаемое устройство, как и известное, не прекращает работу, а обязательно восстанавливается. При этом предлагаемое устройство может продолжать работу и после двух и большего количества сбоев, а известное устройство допускает только по одному сбою при чтении из каждого блока па- -.мяти. Кроме того, при отказе ячеек памяти известное устройство теряет дополнительно один такт вхолостую для считывания заведомо искаженной микрокоманды.

50

ормула

5 1309024

изобретения

вы ин вт щи со вх ад ма со вх пе ро пе ци тр ве ду вт И

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса, коммутатор, два триггера упраэления, два элемента И и элемент задержки, отличающееся тем, что, с целью сокращения объема оборудования, оно содержит сумматор по модулю два и регистр информации, информационный вход, синхровход и выход которого соединены соответственно с выходом операционного поля блока памяти микрокоманд, выходом первого элемента И и операционным выходом устройства, первый, второй и третий входы и выход сумматора по модулю два подключены

выходом первого элемента И и первым информационным входом коммутатора, второй информационный вход, управляющий вход и выход которого подключены соответственно к адресному входу и входу условий ветвления .устройства и адресному входу блока памяти микрокоманд, вход и выход элемента задержки соединены соответственно с тактовым входом устройства и первым входом первого элемента И, второй вход кото рого подключен к.инверсному выходу первого триггера управления, информа ционный вход и синхровход первого триггера управления соединены соответственно с выходом сумматора по мо дулю два и. тактовым входом устройств второй вход и выход второго элемента И подключены соответственно к тактосоответственно к выходу адресного поля, выходу операционного поля, выходу О вому входу устройства и синхровходу контрольного разряда блока памяти второго триггера управления, инверс- микрокоманд и первому входу второго , ный выход которого соединен с его элемента И, информационный вход, синхровход и выход регистра адреса соединены соответственно с выходом адрес ного поля блока памяти микрокоманд,

,5

информационным входом, а прямой вь ход второго триггера управления подключен к входу старшего разряда адреса блока памяти микрокоманд.

фиъ. 2.

Редактор Н.Тупица

Составитель Г.Виталиев

Техред В.Кадар Корректор.А.Тяско

Заказ 1799/41Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

выходом первого элемента И и первым информационным входом коммутатора, второй информационный вход, управляющий вход и выход которого подключены соответственно к адресному входу и входу условий ветвления .устройства и адресному входу блока памяти микрокоманд, вход и выход элемента задержки соединены соответственно с тактовым входом устройства и первым входом первого элемента И, второй вход которого подключен к.инверсному выходу первого триггера управления, информационный вход и синхровход первого триггера управления соединены соответственно с выходом сумматора по модулю два и. тактовым входом устройства, второй вход и выход второго элемента И подключены соответственно к тактовому входу устройства и синхровходу второго триггера управления, инверс- ный выход которого соединен с его

О вому входу устройства и синхровходу второго триггера управления, инверс- , ный выход которого соединен с его

,5

информационным входом, а прямой вь ход второго триггера управления подключен к входу старшего разряда адреса блока памяти микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1267415A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ (электронных вычислительных машин) с повьшенной надежностью. Целью изобретения является сокращение -объема оборудования устройства. С этой целью в устройство, содержащее блок 8 памяти микрокоманд, регистр 3 адреса, коммутатор 6, два триггера 5,7 управления, два элемента И 2,4 и элемент Т задержки, введены сумматор 9 по модулю два и регистр 10 информации, что позволяет обеспечить равные с известными устройствами параметры надежности при исключении из их состава второго блока памяти микрокоманд и средств для формирования его входных и выходных сигналов. 2 ил. с 5 сл

| Микропрограммное устройство управления | 1981 |

|

SU993261A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Реконфигурируемое устройство с программным управлением | 1981 |

|

SU1007108A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-02—Подача