(Л

4 О9

СО

(Pat-f

1U

Изобретение относится к вычислительной техник и может быть использовано в программируемых постоянных запоминающих устройствах (ППЗУ),

Целью изобретения является упрощение дешифратора.

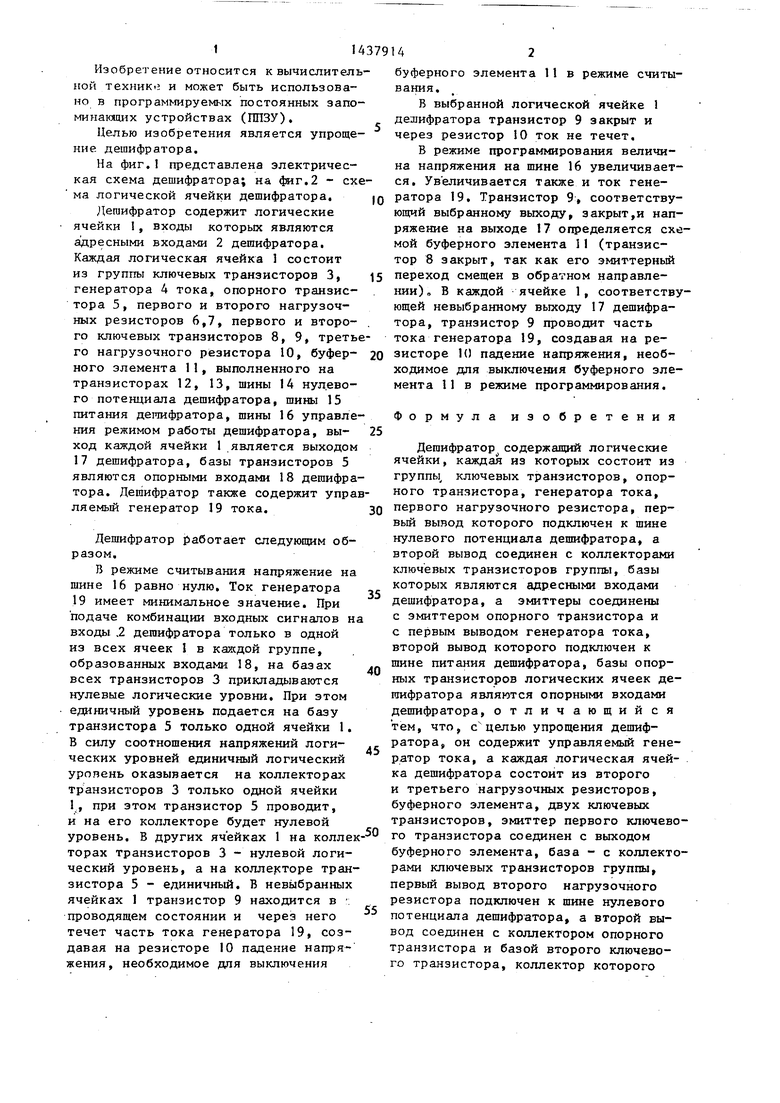

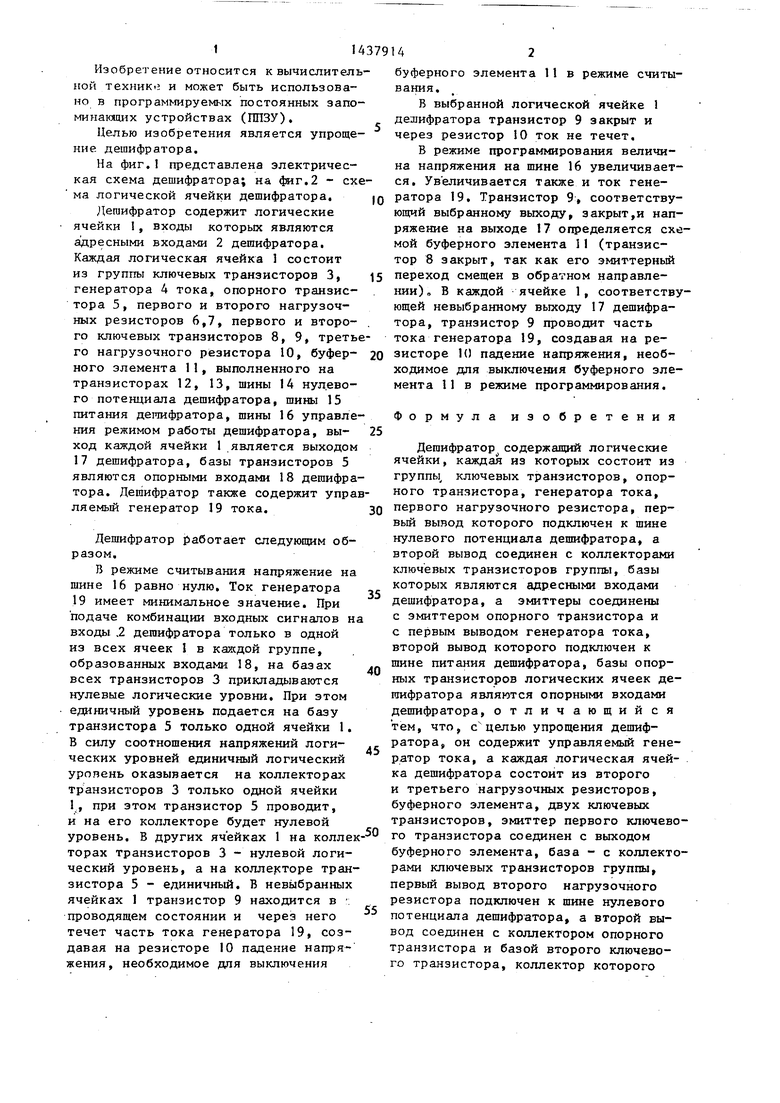

На фиг.1 представлена электрическая схема дешифратора; на фиг.2 - схма логической ячейки дешифратора,

Дешифратор содержит логические ячейки 1, входы которых являются адресными входами 2 дешифратора. Каждая логическая ячейка 1 состоит из группы ключевых транзисторов 3, генератора 4 тока, опорного транзистора 5, первого и второго нагрузочных резисторов 6,7, первого и второго ключевых транзисторов 8, 9, третьго нагрузочного резистора 10, буфер- кого элемента П, выполненного на транзисторах 12, 13, шины 14 нулевого потенциала дешифратора, шины 15 питания депифратора, шины 16 управления режимом работы дешифратора, вы- ход каждой ячейки 1 является выходом 17 дешифратора, базы транзисторов 5 являются опорными входами 18 дешифратора. Дешифратор также содержит упраляемый генератор 19 тока.

Дешифратор работает следующим образом.

В режиме считывания напряжение на шине 16 равно нулю. Ток генератора 19 имеет минимальное значение. При подаче комбинации входных сигналов н входы .2 дешифратора только в одной из всех ячеек 1 в каждой группе, образованных входами 18, на базах всех транзисторов 3 прикладываются нулевые логические уровни. При этом единичный уровень подается на базу транзистора 5 только одной ячейки 1. В силу соотношения напряжений логи- ческих уровней единичный логический уровень оказывается на коллекторах транзисторов 3 только одной ячейки 1, при этом транзистор 5 проводит, и на его коллекторе будет нулевой уровень. В других ячейках 1 на коллек торах транзисторов 3 - нулевой логический уровень, а на колле торе транзистора 5 - единичный. В невыбранных ячейках 1 транзистор 9 находится в проводящем состоянии и через него течет часть тока генератора 19, создавая на резисторе 10 падение напряжения, необходимое для выключения

Q

5 0 5 0

д ,

5

142

буферного элемента 11 в режиме считывания.

В выбранной логической ячейке 1 дешифратора транзистор 9 закрыт и через резистор 10 ток не течет.

В режиме программирования величина напряжения на шине 16 увеличивается. Ув еличивается также и ток генератора 19. Транзистор 9, соответствующий выбранному выходу, закрыт,и напряжение на выходе 17 определяется схемой буферного элемента 11 (транзистор 8 закрыт, так как его эмиттерньй переход смещен в обратном направлении), В каждой ячейке 1, соответствующей невыбранному выходу 17 дешифратора, транзистор 9 проводит часть тока генератора 19, создавая на резисторе И) падение напряжения, необходимое для выключения буферного элемента 11 в режиме программирования.

Формула изобретения

Дешифратор содержащий логические ячейки, каждая из которых состоит из группы ключевых транзисторов, опорного транзистора, генератора тока, первого нагрузочного резистора, первый вывод которого подключен к шине нулевого потенциала дешифратора, а второй вывод соединен с коллекторами ключевых транзисторов группы, базы которых являются адресными входами дешифратора, а эмиттеры соединены с эмиттером опорного транзистора и с первым выводом генератора тока, второй вывод которого подключен к щине питания дешифратора, базы опорных транзисторов логических ячеек дешифратора являются опорными входами дешифратора, отличающийся тем, что, с целью упрощения дешифратора, он содержит управляемый генератор тока, а каждая логическая ячейка дешифратора состоит из второго и третьего нагрузочных резисторов, буферного элемента, двух ключевых транзисторов, эмиттер первого ключевого транзистора соединен с выходом буферного элемента, база - с коллекторами ключевых транзисторов группы, первый вывод второго нагрузочного резистора подключен к шине нулевого потенциала дешифратора, а второй вывод соединен с коллектором опорного транзистора и базой второго ключевого транзистора, коллектор которого

(AI-A,) .11

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Накопитель | 1988 |

|

SU1536442A1 |

| Устройство для индикации | 1982 |

|

SU1072093A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Накопитель для оперативного запоминающего устройства | 1990 |

|

SU1751815A1 |

Изобретение относится к вычислительной технике и может быть использовано в програьмируемых постоянных запоминающих устройствах. Цель изобретения - упрощение дапи4фатора. Поставленная цель достигается тем, что дешифратор содержит второй и третий нагрузочные резисторы , первый и второй ключевые транзисторы 8,9, буферш 1й элемент И, управ-, ляемый генератор:тока 19 с соответствующими связями. Использование буферных элементов 11 позволяет увеличить размах напряжения на выходе 17 дешифратора. В результате одни и те же выходы 17 дешифратора могут быть использованы как в режиме считывания, так и в режиме программирования. 2 ил.

| Патент аЧА № 4014007, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Дешифратор | 1977 |

|

SU681557A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-15—Публикация

1985-08-20—Подача