«

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля электромеханических блоков | 1982 |

|

SU1151973A1 |

| Устройство для тестового контроля временных соотношений | 1987 |

|

SU1596337A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1608672A1 |

| Устройство микропрограммного управления | 1981 |

|

SU1003086A1 |

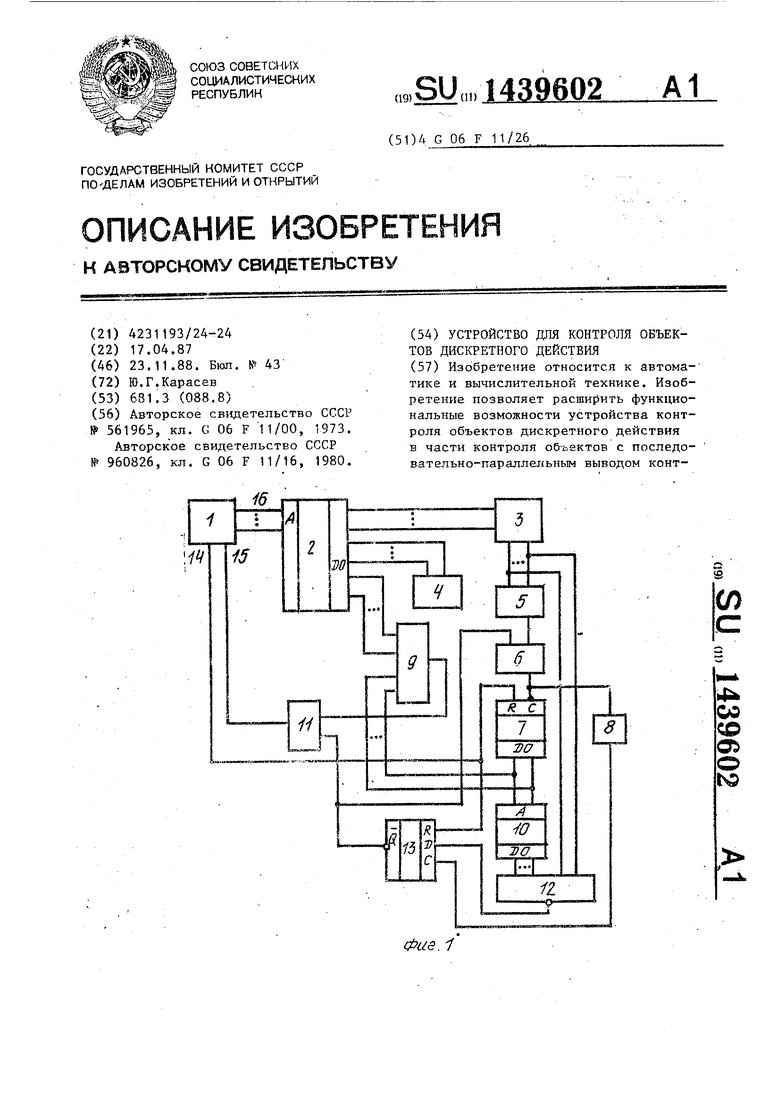

Изобретение относится к автоматике и вычислительной технике. Изобретение позволяет расширить функциональные возможности устройства контроля объектов дискретного действия в части контроля объектов с последовательно-параллельным выводом конт

4ik 00 CD Gb О ГчЭ

Фив. 1

рольной информации и неопределенными временными задержками между отдельными наборами реакций объекта контроля. Цель изобретения - повышение достоверности контроля. Устройство содержит блок управления 1, блоки памяти 2, 10, таймер А, блоки сравнения 9, 12, счетчик 7, элементы И 6, 11, зшемент задержки 8, элемент ИЛИ и триггер 13. Тестовые наборы формируются по командам с блока управления 1 первым блоком памяти 2. Контроль вьжодных реакций производится блоком сравнения 12. Триггер 13 фиксирует ошибки в выходнь;х реакциях объекта контроля 3. Блок памяти 10 счетчик 7, таймар 4, блок сравнения 12 и элемент задержки 8 обеспечивают контроль нескольких наборов выходных реакций объекта контроля 3 на один тест и их обработку по обобщенному сигналу, не зависимому от так1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля систем дискретного действия с последовательно-параллельным выводом контрольной информации и неопределенными временными задержками между отделными наборами реакций объектов контроля (ОК) .

Цель изобретения - повышенке достоверности контроля.

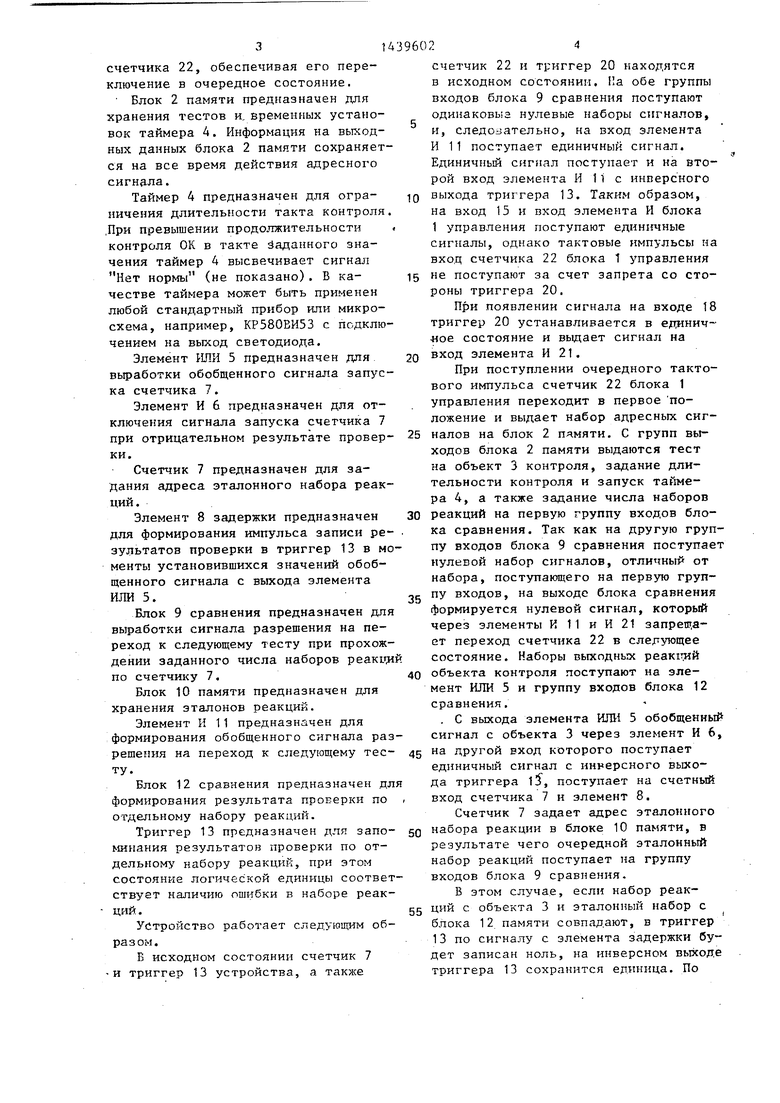

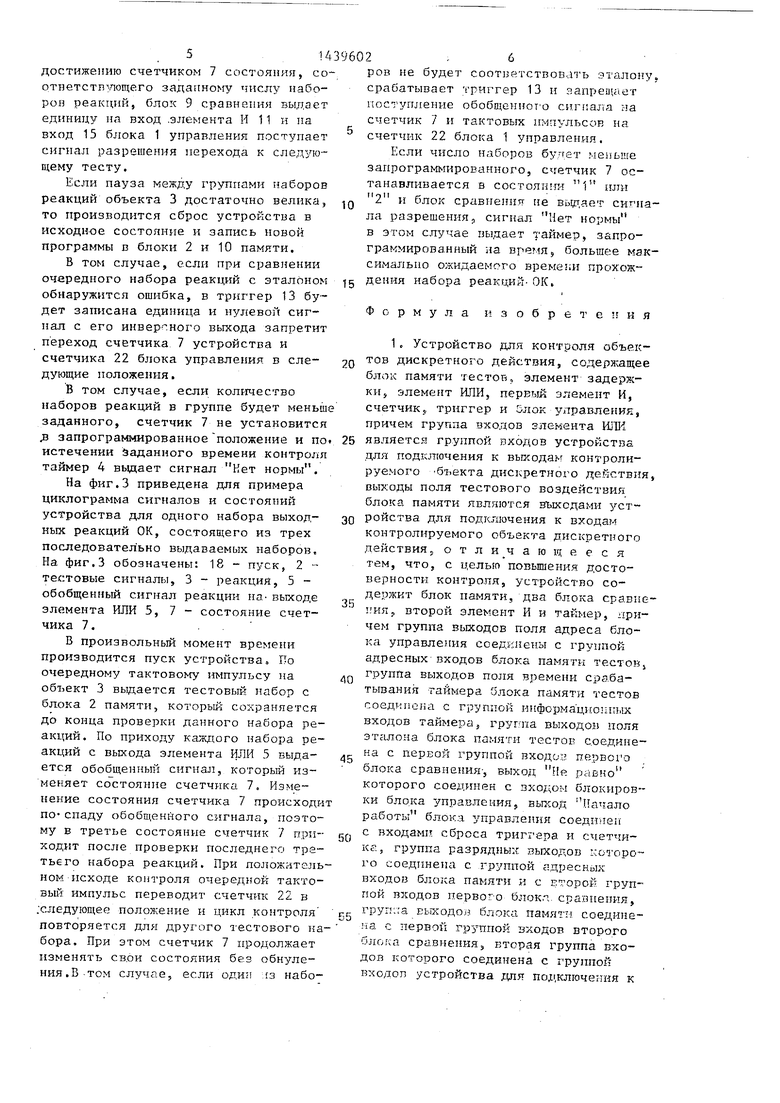

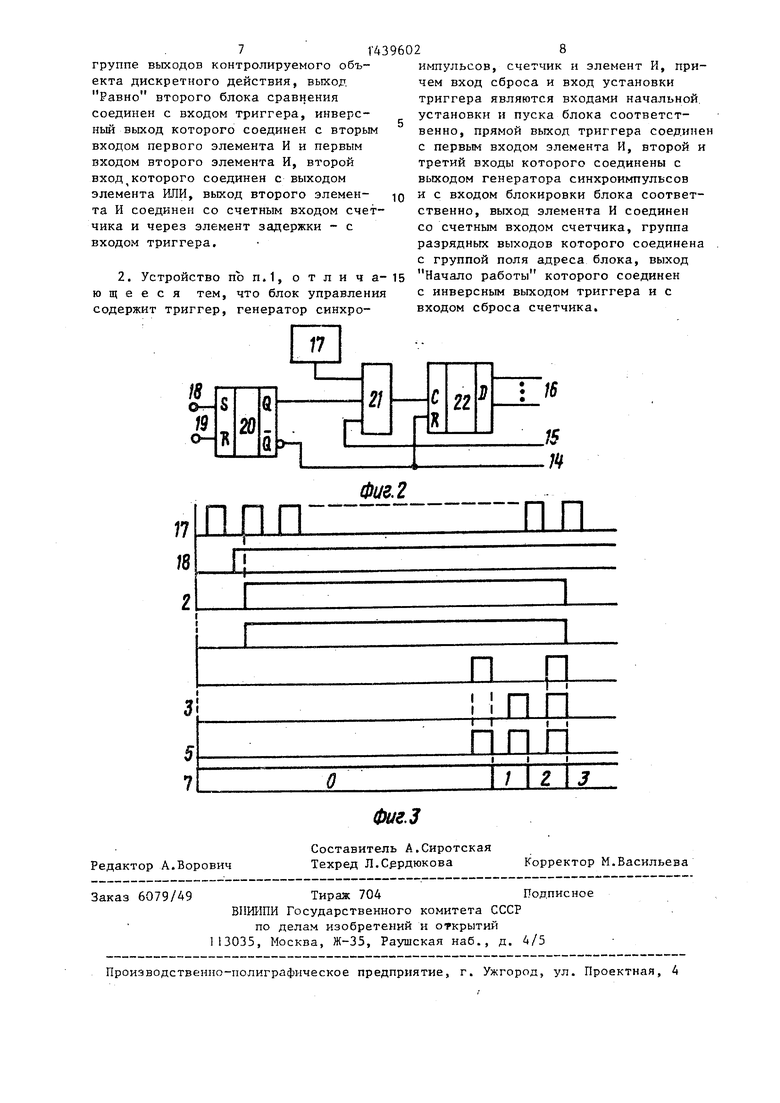

На фиг,1 приведена фунрлщональнэя схема устройства контроля на фиг.2- функциональная схема, блока управления; на фиг.3 - циклограмма работы устройства,

Устройство (фйг.1) содержит блок управления., блок 2 памяти тестов, объект 3 контроля, таймер 4, элемент ИЛИ 5, элемент И 6, счетчик 7, элемент 8 задержки, блок 9 сравнения, блок 10 памяти, элемент 11, блок ;12 сравнения и триггер 13. На фиг.Т также обозначены выход 14 начала работы управления, вход блокировки блока 15 управления, группз поля адреса выходов блока 16 управления,

товой частоты устройства. Сущность изобретения заключается в том, что для хранения эталонных значений реакций вводится второй блок памяти, а для их выборки - счетчик. Это позволяет обеспечить контроль объекта контроля с несколькими наборами выходных реакций на один -тестовый сигнал без увеличения основной памяти. Кроме -того, выбор эталонных значений реакций и их сравнение с реакциями производятся по обобщенному сигналу, формируемому элементом ИЛИ. Это позволяет сделать незавйсимь|м процгсс контроля выходных реакций, поступающих с неопределенной задержкой по отношению к времени выдачи теста, от периода тактовых импульсов, а следовательно, избежать необходш.1ости ор ганизации циклов и увеличить быстродействие устройства. 1 ЗоП. ф-лы. 3 ил,

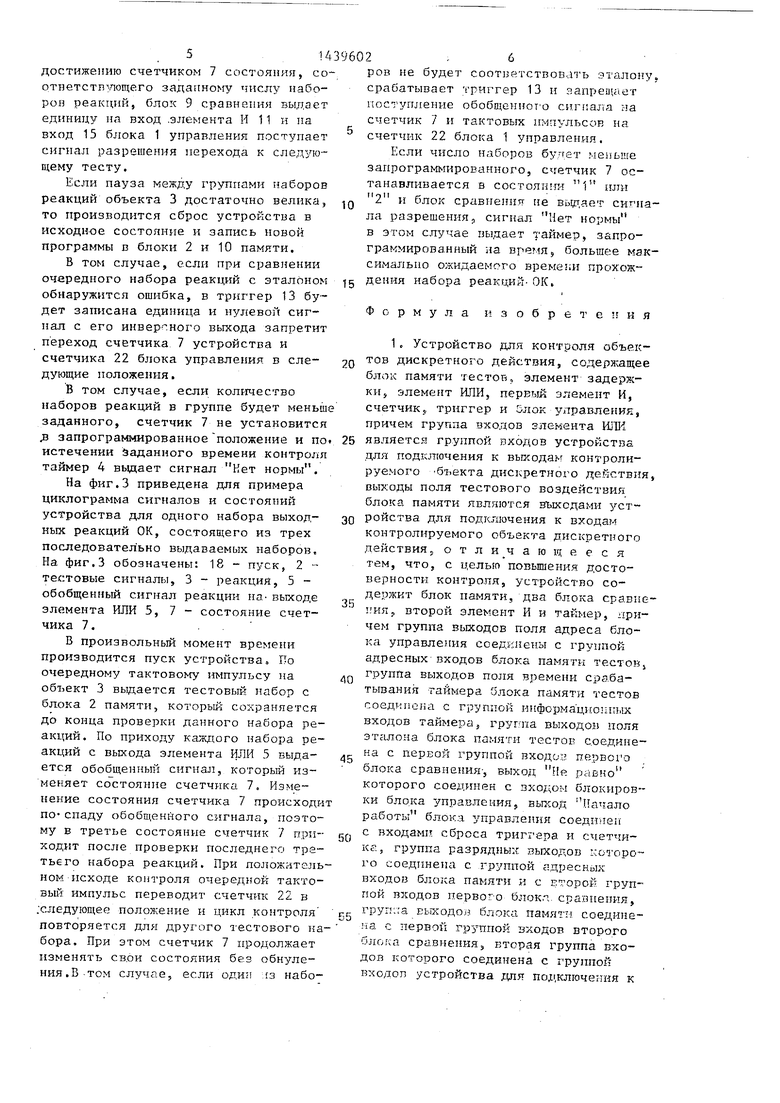

Блок 1 управления (фиг,2) содержит генератор 17 синхроимпульсов, вход 18 пуска, вх:од 19 канальной установки, триггер 20, элемент И 21

и счетчик 22.

Блок 1 управления тгредназначен для запуска устройства, приведение его в исходное состояние, а также задания адреса тестового набора и последовательности выборки тестов. В исходном состоянии после подачи пулевого сигнала на вход 19 счетчик 22 адреса блока 1 управления устанавливается в нулевое состояние за

счет единичного сигнала, поступающего с инверсного вьпсода триггера 20. Этот же сигнал поступает на выход 14 блока 1 управления.

После подачи нуля на вход 18 триг гер 20 переходит в единичное состояние и снимает сигнап сброса со счетчика 22, а также дает разрещение на пропуск сигналов с генератора 17 на

ci вход счетчика 22 элементом И 21. После -прихода разрешающего сигнала на вход элемента И 21 тактовые импульсы начинают поступать на вход

счетчика 22, обеспечивая его переключение в очередное состояние.

Блок 2 памяти предназначен для хранения тестов и, временных установок таймера 4. Информация на выходных данных блока 2 памяти сохраняется на все время действия адресного сигнала.

Таймер 4 предназначен для ограничения длительности такта контроля ,При превышении продолжительности контроля ОК в такте Заданного значения таймер 4 высвечивает сигнал Нет нормы (не показано). В качестве таймера может быть применен любой стандартный прибор или микросхема, например, КР580ВИ53 с подключением на выход светодиода.

Элемент ИЛИ 5 предназначен для вьфаботки обобщенного сигнала запуска счетчика 7.

Элемент И 6 предназначен для отключения сигнала запуска счетчика 7 при отрицательном результате проверки.

Счетчик 7 предназначен для задания адреса эталонного набора реакций.

Элемент 8 задержки предназначен для формирования импульса записи ре- зультатов проверки в триггер 13 в моменты установившихся значений обобщенного сигнала с выхода элемента ИЛИ 5.

Блок 9 сравнения предназначен для выработки сигнала разрешения на переход к следующему тесту при прохождении заданного числа наборов реак1.ти по счетчику 7.

Блок 10 памяти предназначен для хранения эталонов реакций.

Элемент И 11 предназначен для формирования обобщенного сигнала разрешения на переход к следующему тесту.

Блок 12 сравнения предназначен дл формирования результата проверки по отдельному набору реакций.

Триггер 13 предназначен для запоминания результатов проверки по отдельному набору реакций, при этом состояние логической единицы соответствует наличию ошибки в наборе реакций.

Устройство работает следующим образом.

Б исходном состоянии счетчик 7 и триггер 13 устройства, а также

0

5

0

5

счетчик 22 и триггер 20 находятся в исходном состоянии. обе группы входов блока 9 сравнения поступают одинаковые нулевые наборы сигналов, и, следовательно, на вход элемента И 11 поступает единичный сигнал. Единичный сигнал поступает и на второй вход элемента И 11 с инверсного выхода триггера 13. Таким образом, на вход 15 и вход элемента И блока 1 управления поступают единичные сигналы, однако тактовые импульсы на вход счетчика 22 блока 1 управления не поступают за счет запрета со стороны триггера 20.

При появлении сигнала на входе 18 триггер 20 устанавливается в единич- «ое состояние и вьщает сигнал на вход элемента И 21.

При поступлении очередного тактового импульса счетчик 22 блока 1 управления переходит в первое положение и выдает набор адресных сигналов на блок 2 памяти. С групп выходов блока 2 памяти выдаются тест на объект 3 контроля, задание длительности контроля и запуск таймера 4, а также задание числа наборов реакций на первую группу входов блока сравнения. Так как на другую группу входов блока 9 сравнения поступает нулевой набор сигналов, отличный от набора, поступающего на первую группу входов, на выходе блока сравнения формируется нулевой сигнал, который через элементы И 11 и И 21 запрещает переход счетчика 22 в следующее состояние. Наборы выходньх реакхтий объекта контроля поступают на элемент ИЛИ 5 и группу входов блока 12 сравнения.

. С выхода элемента ИЛИ 5 обобщенный сигнал с объекта 3 через элемент И 6, на другой вход которого поступает единичный сигнал с иннерсного выхода триггера l5, поступает на счетный вход счетчика 7 и элемент 8.

Счетчик 7 задает адрес эталонного набора реакции в блоке 10 памяти, в результате чего очередной эталонный набор реакций поступает на группу входов блока 9 сравнения.

В этом случае, если набор реак- 5 ций с объекта 3 и эталонный набор с блока 12 памяти совпадают, в триггер 13 по сигналу с элемента задержки будет записан ноль, на инверсном выходе триггера 13 сохранится единица. По

0

5

0

5

0

достижению счетчиком 7 состояния, со- отнетстл :-, тощего заданному числу наборов реакций, блок 9 сравнения выдгзет единицу на вход .элемента И 11 и па вход 15 блока 1 управления поступает СНГ11ЯП разрешения перехода к следующему тесту.

Если пауза между группами наборов реакций объекта 3 достаточно велика, то производится сброс устройства в исходное состояние и запись новой программы с блоки 2 и 10 памяти,

В том случае, если при сравнении очередного набора реакций с эталоном обнаружится ошибка, в триггер 13 будет записана единица и нулевой сигнал с его инверпного выхода запретит переход счетчика 7 устройства и счетчика 22 блока управления в следующие положения.

В том случае, если количество наборов реакций в группе будет меньш заданного, счетчик 7 не установится р запрограммированное положение и по истечении Заданного времени контроля таймер 4 выдает сигнал Кет нормы.

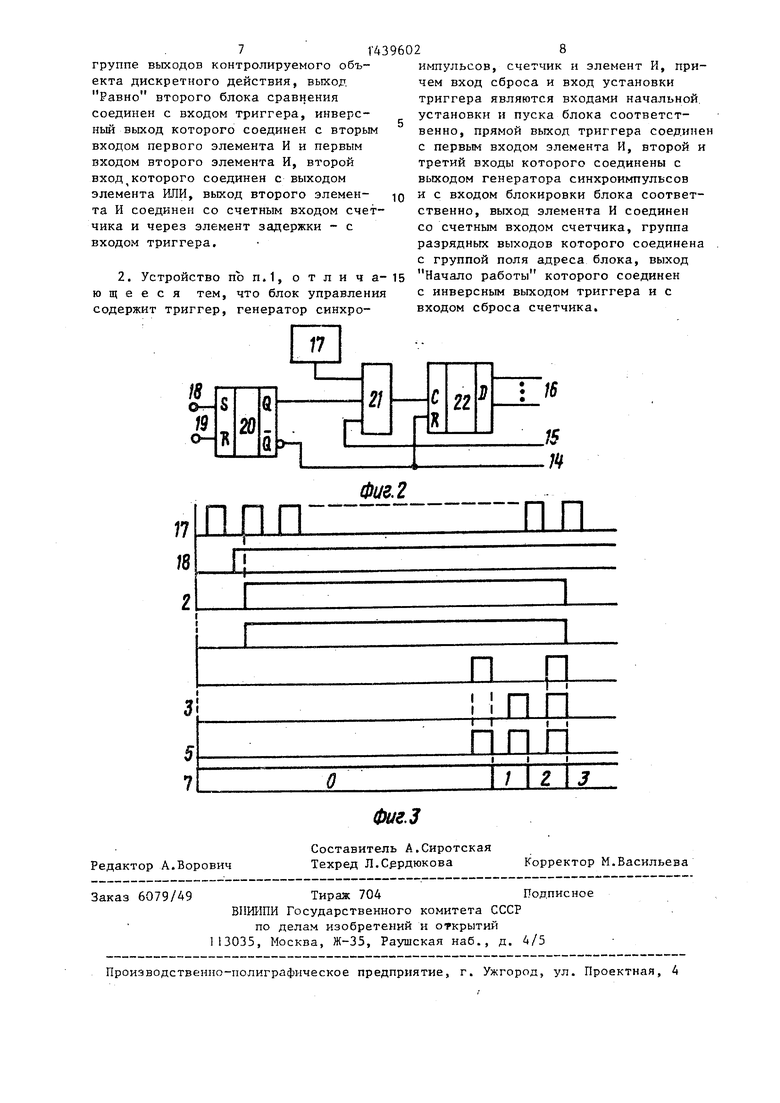

На фиг.З приведена для примера циклограмма сигналов и состояний устройства для одного набора выходных реакций ОК, состоящего из трех последовател ьно выдаваемых наборов. На фиг.З обозначены: 18 - пуск, 2 - тестовые сигналы, 3 - реакций, 5 - обобщенный сигнал реакции на-выходе элемента ИЛИ 5, 7 - состояние счетчика 7.

В произвольный момент времени производится пуск устройства. По очередному тактовому импульсу на объект 3 вьщается тестовый набор с блока 2 памяти, которьш сохраняется до конца проверки данного набора реакций. По приходу каждого набора реакций с выхода элемента ИЛИ 5 выдается обобщенный сигнал, которьм изменяет состояние счетчика 7. Изменение состояния счетчика 7 происходи по-спаду обобщенного сигнала, поэтому в третье состояние счетчик 7 приходит nocjre проверки последнего третьего набора реакций. При положительном исходе контроля очередной тактовый импульс переводит счетчик 22 в . следующее положение и цикл контроля повторяется для другого 1 естового набора. При этом счетчик 7 продолжает изменять свои состояния без обнуления.В -том случае, если один лз набо

ров не будет соответствовать Э1 ало1 у. срабатывает триггер 13 и запрещает посп упление обобщеннот о сигнала счетчик 7 и тактовых пмаух1Ьсов на счетчик 22 блока 1 управления.

Если число наборов будет меньше 3anporpaMNn- pOEaHHoro, счетчик 7 останавливается в состояхпга 1 или 2 и блок сравнения не вьщает сигнала разрешения, сигнал Нет нормы в этом случае выдает таймер, запрограммированный на времяJ большее максимально ожидаемого вренегиг прох ож- дения набора реакций- ОК.

Формула и 3 о б р е т е и я

0

5

0

5

0

5

0

Г43

группе выходов контролируемого объекта дискретного действия, выход Равно второго блока сравнения соединен с входом триггера, инверс- ньй выход которого соединен с вторым входом первого элемента И и первым входом второго элемента И, второй вход которого соединен с выходом элемента ИЛИ, выход второго элемен- та И соединен со счетным входом счетчика и через элемент задержки - с входом триггера.

Составитель А.Сиротская Техред Л.Сррдюкова

8

импульсов, счетчик и элемент И, причем вход сброса и вход установки триггера являются входами начальной, установки и пуска блока соответственно, прямой выход триггера соедине с первым входом элемента И, второй и третий входы которого соединены с выходом генератора синхроимпульсов и с входом блокировки блока соответственно, выход элемента И соединен со счетным входом счетчика, группа разрядных выходов которого соединена с группой поля адреса блока, выход

Начало работы которого соединен с инверсным выходом триггера и с входом сброса счетчика.

16

15 П

Фив. 2

Фие.З

Корректор М.Васильева

| Устройство для обнаружения неисправностей цифровых систем | 1973 |

|

SU561965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых блоков | 1980 |

|

SU960826A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1987-04-17—Подача