W §

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1986 |

|

SU1438008A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Преобразователь р-кода фибоначчи в двоичный код | 1976 |

|

SU662932A1 |

| Преобразователь кода Фибоначчи в двоичный код | 1986 |

|

SU1432789A1 |

| Устройство для преобразования двоичного кода в код магнитного носителя | 1980 |

|

SU1148572A3 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1231609A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

Изобретение относится к вычислительной технике и может быть исполь- зсэвано в-Системах преобразования информации, представленной двошшым кодом, в код Фибоначчи. Целью изобретения является повышение быстродействия преобразователя. Преобразователь содержит входной регистр 1, сумматор 2, блоки 3-5 постоянной памяти, выходной регистр 6, элемент 7 задержки, информационные и управляющие входы 8 и-9, выходы 10 преобразователя. I ил.

4

;со ю

v|

сд

Изобретение относится к вычислительной технике,и мелеет быть использовано для преобразования информации, представленной двоичным кодом в код Фибоначчи,

Цель изобретения - повьшение быстродействия преобразователя.

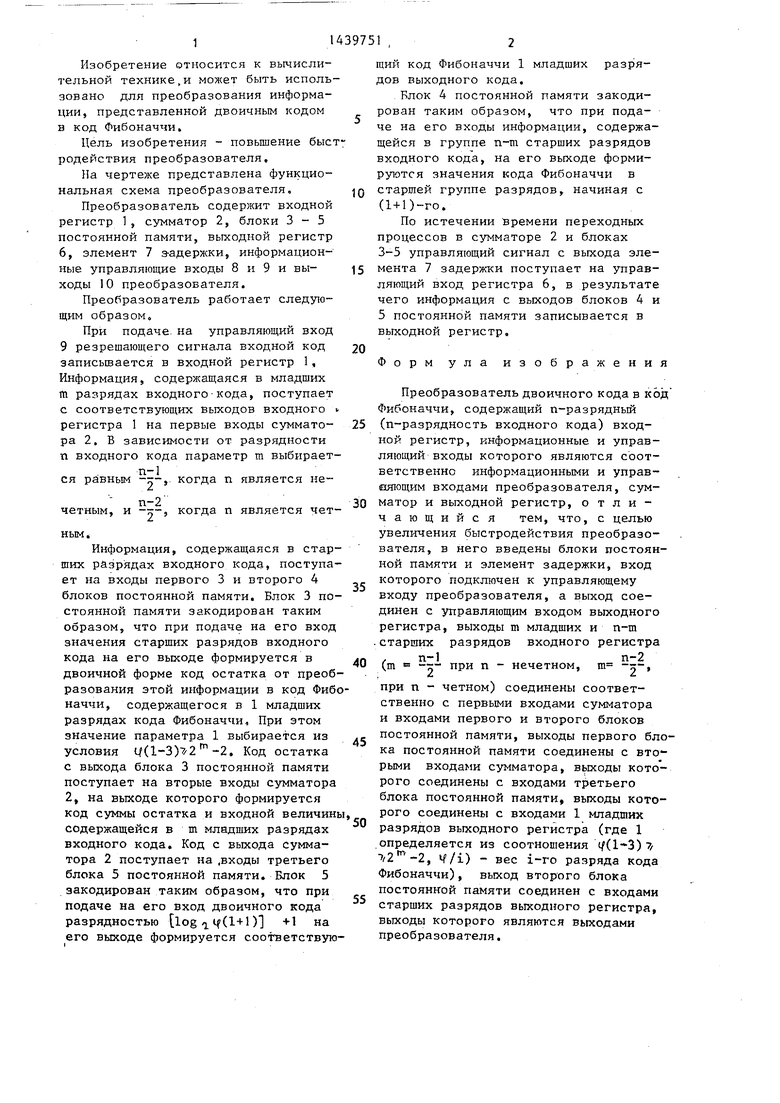

Па чертеже представлена функциональная схема преобразователя.

Преобразователь содержит входной регистр 1, сумматор 2, блоки 3-5 постоянной памяти, выходной регистр 6, элемент 7 з-адержки, информационные управляющие входы 8 и 9 и выходы 10 преобразователя.

Преобразователь работает следующим образом,

При подаче, на управляющий вход 9 резрешающего сигнала входной код записьшается в входной регистр 1, Информация, содержащаяся в младших m разрядах входного-кода, поступает с соответствующих выходов входного регистра 1 на первые входы сумматора 2, В зависимости от разрядности п входного кода параметр m выбираетп-1ся равным ,. когда п является нечетным.

п-2 и

когда п является четным.

Информация, содержащаяся в старших разрядах входного кода, поступает на входы первого 3 и второго 4 блоков постоянной памяти. Блок 3 постоянной памяти закодирован таким образом, что при подаче на его вход значения старших разрядов входного кода на его выходе формируется в двоичной форме код остатка от преобразования этой информации в код Фибоначчи, содержащегося в 1 младших разрядах кода Фибоначчи, При этом значение параметра 1 выбирается из условия Cf(l-3)7/2 -2, Код остатка с выхода блока 3 постоянной памяти поступает на вторые входы сумматора 2, на выходе которого формируется код суммы остатка и входной величины содержащейся в m младших разрядах входного кода. Код с выхода сумматора 2 поступает на .входы третьего блока 5 постоянной памяти. Блок 5 закодирован таким образом, что при подаче на его вход двоичного кода разрядностью {log- 1(1+1) +1 на его выходе формируется соответствую

0

5

0

5

0

щий код Фибоначчи 1 младших разрядов выходного кода.

Блок 4 постоянной памяти закодирован таким образом, что при подаче на его входы информации, содержащейся в группе n-m старших разрядов входного кода, на его выходе формируются значения кода Фибоначчи в старшей группе разрядов, начиная с (1+1)-го,

По истечении времени переходных процессов в сумматоре 2 и блоках 3-5 управляющий сигнал с выхода элемента 7 задержки поступает на управляющий вход регистра 6, в результате чего информация с выходов блоков 4 и 5 постоянной памяти записывается в выходной регистр.

Форм ула изображения

Преобразователь двоичного кода в код Фибоначчи, содержащий п-разрядный (п-разрядность входного кода) входной регистр, информационные и управляющий входы которого являются соответственно информационными и управ- ияющим входами преобразователя, сумматор и выходной регистр, отличающийся тем, что, с целью увеличения быстродействия преобразователя, в него введены блоки постоянной памяти и элемент задержки, вход которого подключен к управляющему входу преобразователя, а выход соединен с управляющим входом выходного регистра, выходы m младших и n-m .старших разрядов входного регистра п-1п-2

5

0

5

т -j-.

(m - г- при п - нечетном,

при п - четном) соединены соответственно с первыми входами сумматора и входами первого и второго блоков постоянной памяти, выходы первого блока постоянной памяти соединены с вторыми входами сумматора, вькоды которого соединены с входами третьего блока постоянной памяти, выходы которого соединены с входами 1 младших разрядов выходного регистра (где 1 определяется из соотнонтения (/(l- S) 7/ /2 -2, if/i) - вес i-ro разряда кода Фибоначчи), выход второго блока постоянной памяти соединен с входами старших разрядов выходного регистра, выходы которого являются выходами преобразователя,

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-23—Публикация

1986-06-09—Подача