1

Изобретение относится к вычислительной технике и может быть использовано для распознавания технического состояния системы внешних запоми- устройств прямого доступа.

Целью изобретения является noBbmie- ние достоверности и быстродействия устройства.

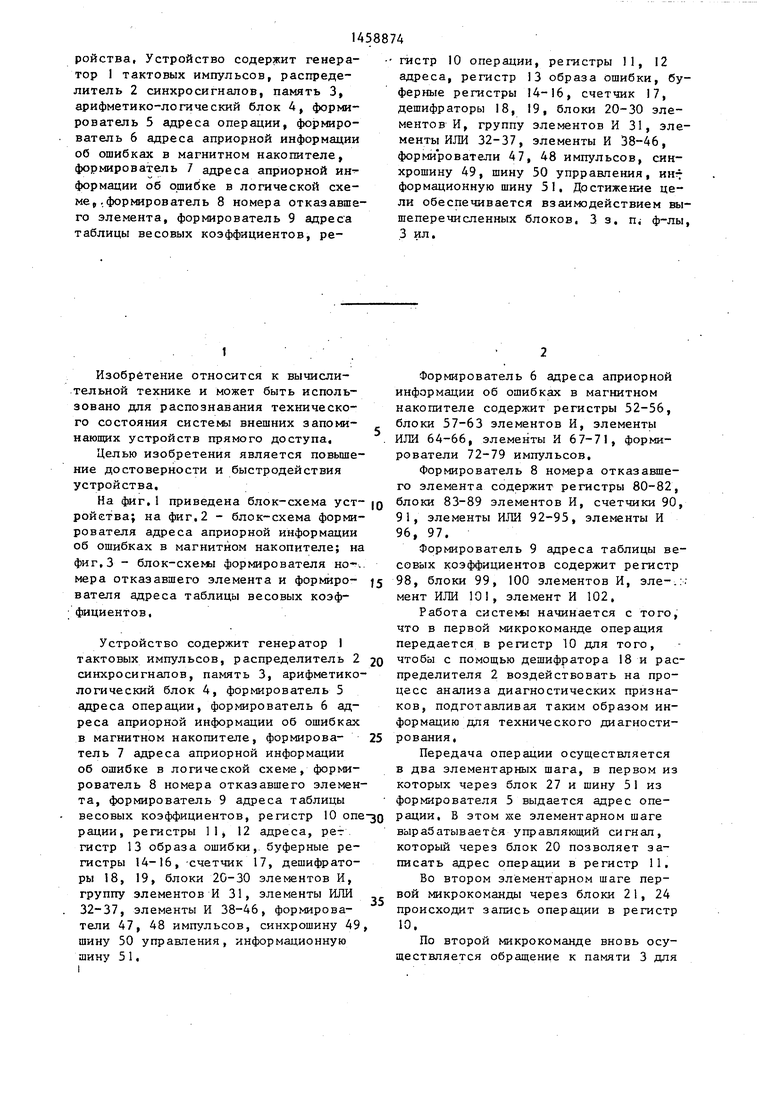

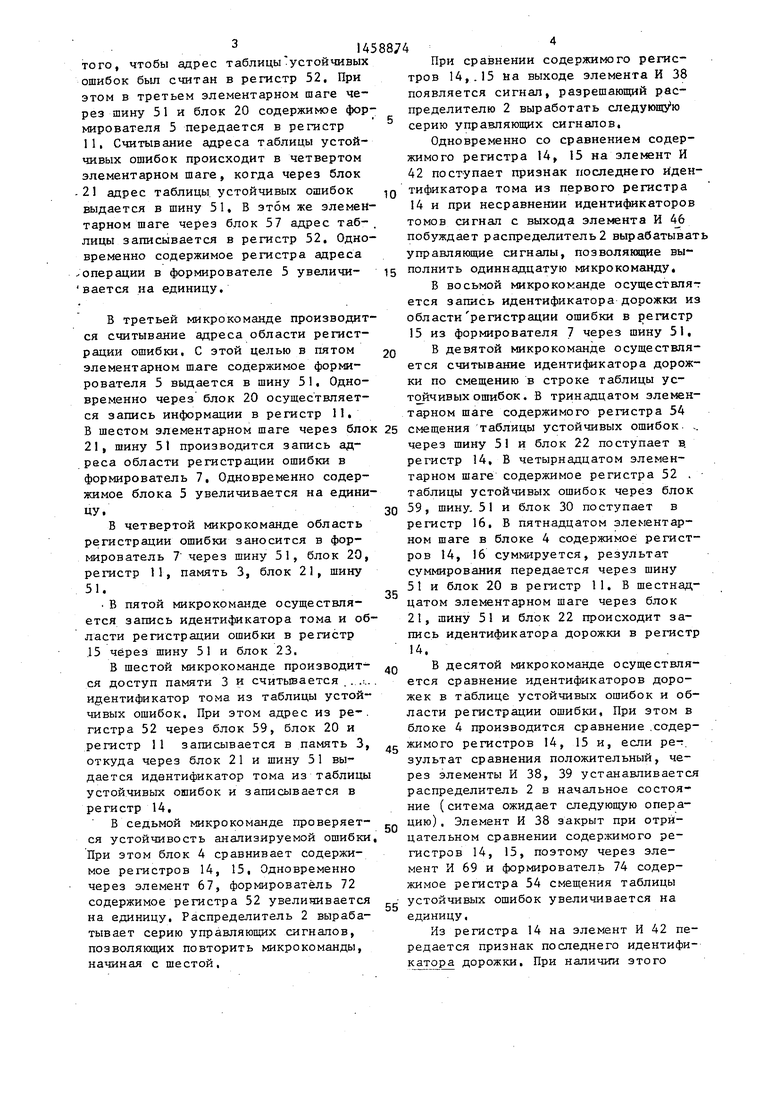

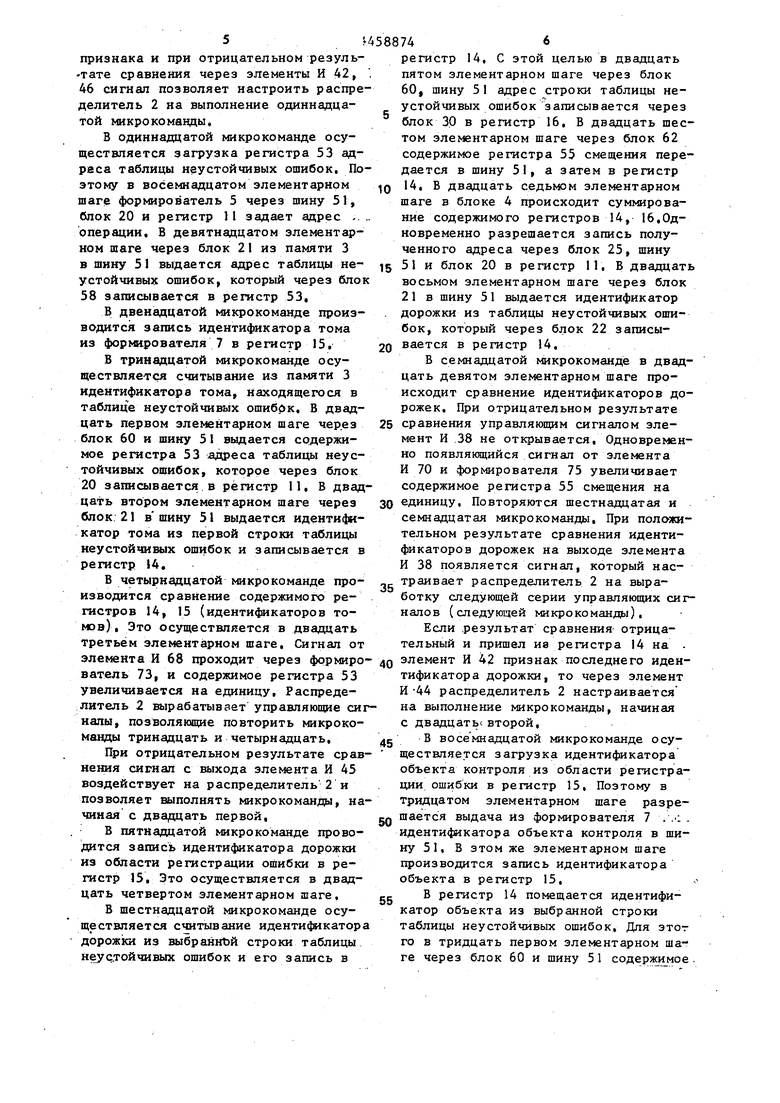

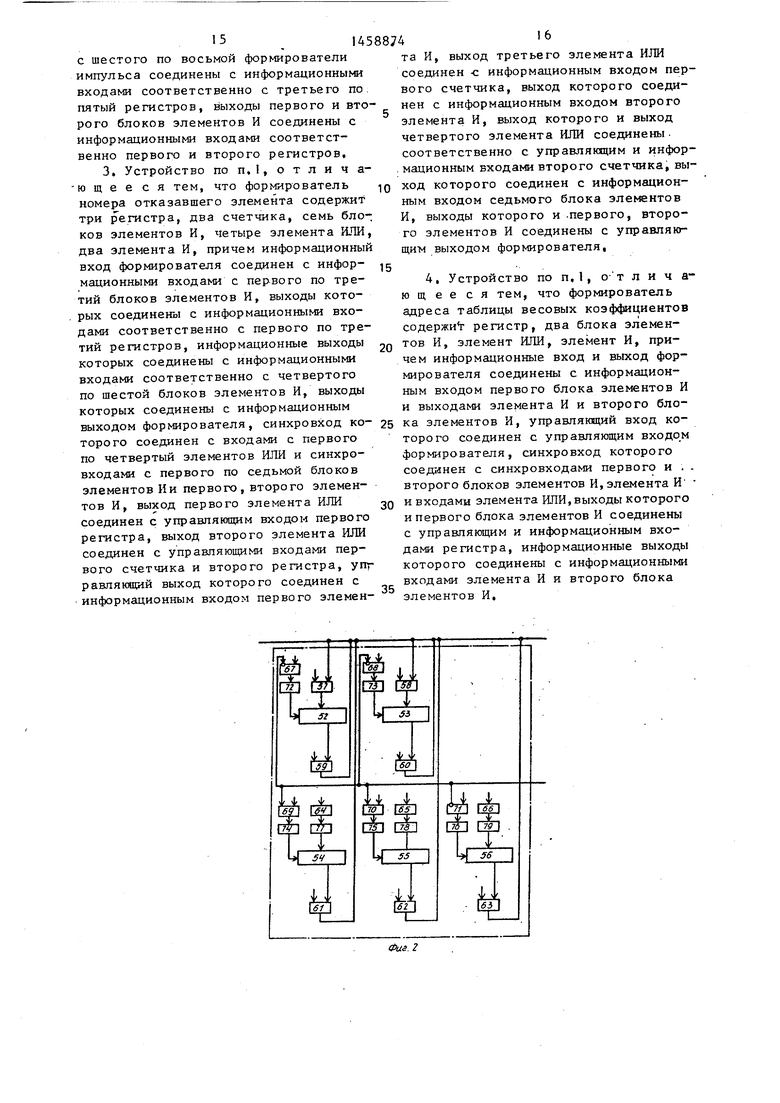

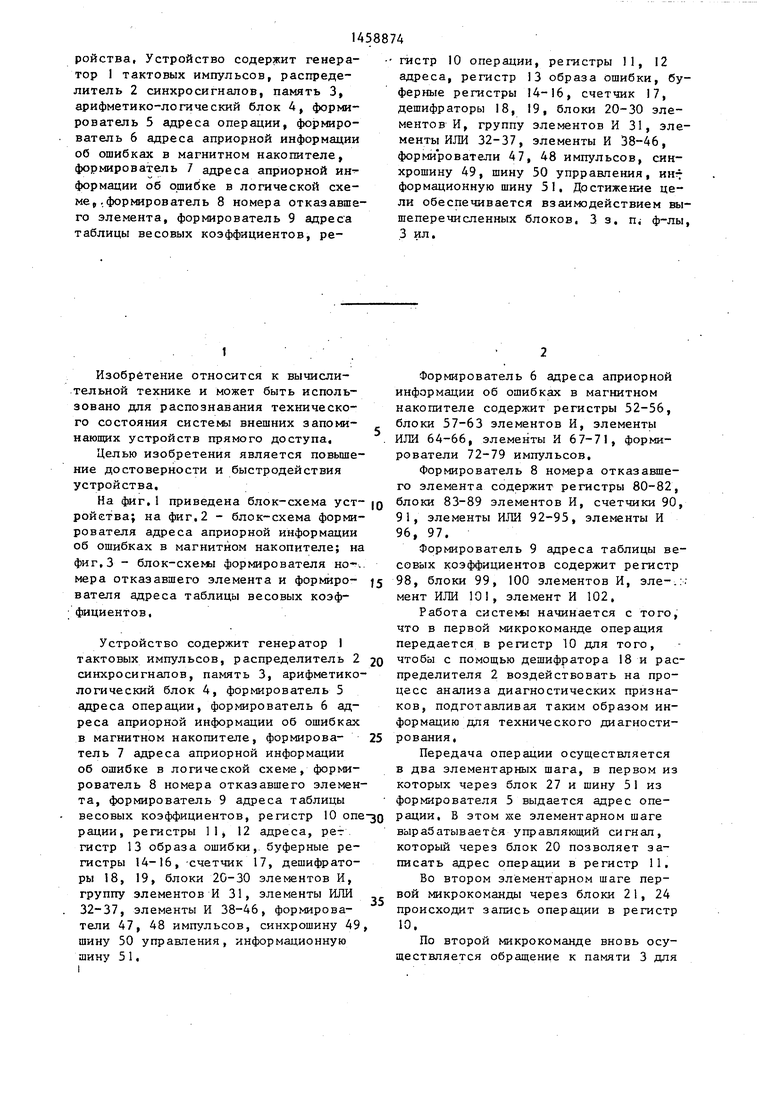

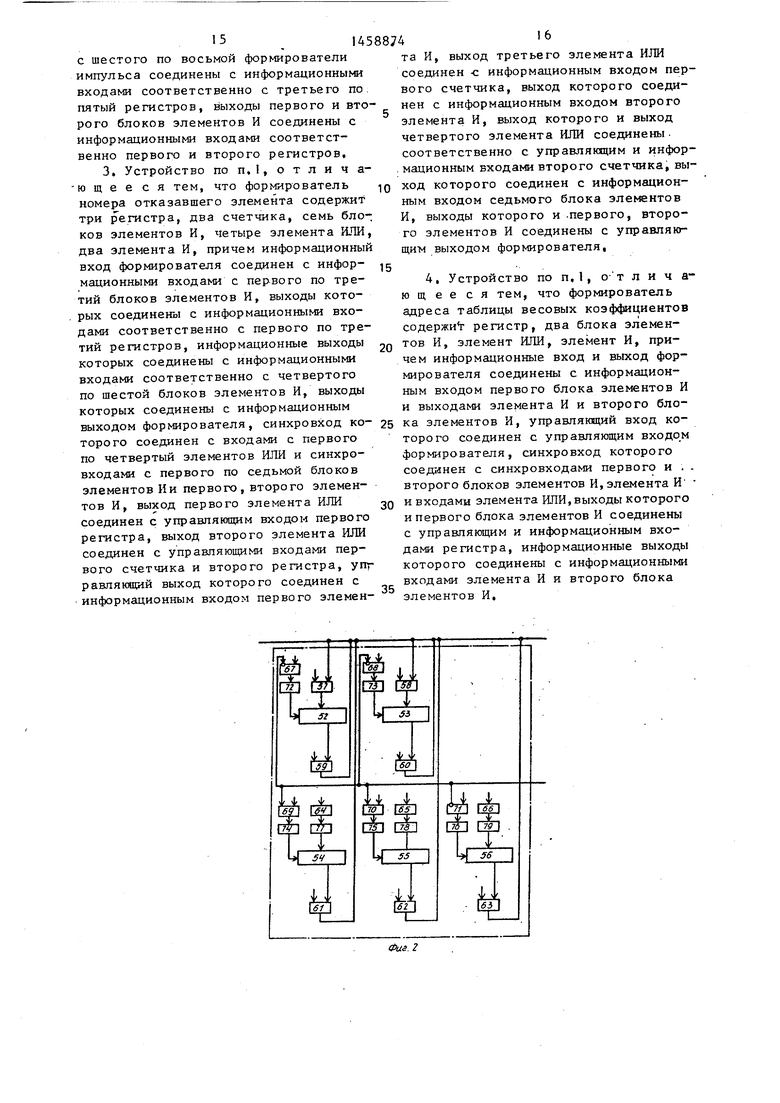

На фиг,1 приведена блок-схема устройства; на фиг,2 - блок-схема формирователя адреса априорной информации об ошибках в магнитном накопителе; на фиг.З - блок-схемз формирователя но-., мера отказавшего элемента и формирователя адреса таблицы весовых коэффициентов.

Устройство содержит генератор I тактовых импульсов, распределитель 2 синхросигналов, память 3, арифметико- логический блок 4, формирователь 5 адреса операции, формирователь 6 адреса априорной информации об ошибках в магнитном накопителе, формирова- тель 7 адреса априорной информации об ошибке в логической схеме, формирователь 8 номера отказавшего элемента, формирователь 9 адреса таблицы весовых коэффициентов, регистр 10 опе рации, регистры 11, 12 адреса, pe-ir гистр 13 образа ошибки, буферные регистры 14-16, -счетчик 17, дешифраторы 18, 19, блоки 20-30 элементов И, группу элементов И 31, элементы ИЛИ 32-37, элементы И 38-46, формирователи 47, 48 импульсов, синхрошину 49 шину 50 управления, информационную шину 51,

0

5

0 5 о

Формирователь 6 адреса априорной информации об ошибках в магнитном накопителе содержит регистры 52-56, блоки 57-63 элементов И, элементы ИЛИ 64-66, элементы И 67-71, формирователи 72-79 импульсов.

Формирователь 8 номера отказавшего элемента содержит регистры 80-82, блоки 83-89 элементов И, счетчики 90, 91, элементы ИЛИ 92-95, элементы И 96, 97,

Формирователь 9 адреса таблицы весовых коэффициентов содержит регистр 98, блоки 99, 100 элементов И, эле-.:; мент ИЛИ 101, элемент И 102,

Работа систем начинается с того, что в первой микрокоманде операция передается в регистр 10 для того, чтобы с помошью дешифратора 18 и распределителя 2 воздействовать на процесс анализа диагностических признаков, подготавливая таким образом информацию для технического диагностирования.

Передача операции осуществляется в два элементарных шага, в первом из которых через блок 27 и шину 51 из формирователя 5 выдается адрес операции, В этом же элементарном шаге вырабатывается управляющий сигнал, который через блок 20 позволяет записать адрес операции в регистр 11,

Во втором элементарном шаге первой микрокоманды через блоки 21, 24 происходит запись операции в регистр 10,

По второй микрокоманде вновь осуществляется обращение к памяти 3 для

3 1458874

того, чтобы адрес таблицы устойчивых ошибок был считан в регистр 52, При этом в третьем элементарном шаге через шину 51 и блок 20 содержимое формирователя 5 передается в регистр 11, Считывание адреса таблицы устойчивых ошибок происходит в четвертом элементарном шаге, когда через блок

21 адрес таблицы, устойчивых сшибок Q выдается в шину 51, В этом же элемей- тарном шаге через блок 57 адрес таб- . лицы записывается в регистр 52, Одновременно содержимое регистра адреса

операции в формирователе 5 увеличи- 15

вается на единицу.

В третьей микрокоманде производится считывание адреса области регист20

рации ошибки, С этой целью в пятом элементарном шлге содержимое формирователя 5 выдается в шину 51, Одновременно через блок 20 осуществляется запись информации в регистр П. В шестом элементарном шаге через блок 25 смешения таблицы устойчивых ошибок 21, шину 51 производится запись ад-через шину 51 и блок 22 поступает в.

В девятой микрокоманде осуществля ется считывание идентификатора дорож ки по смещению в строке таблицы устойчивых ошибок . В тринадцатом элемен тарном шаге содержимого регистра 54

реса области регистрации ошибки в формирователь 7, Одновременно содержимое блока 5 увеличивается на единицу.

В четвертой микрокоманде область регистрации ошибки заносится в формирователь 7 через шину 51, блок 20, регистр 11, память 3, блок 21, шину 51,

. В пятой микрокоманде осуществляется запись идентификатора тома и области регистрации ошибки в регистр .15 через шину 51 и блок 23.

В шестой микрокоманде производится доступ памяти 3 и считьгоается ...... идентификатор тома из таблицы устойчивых ошибок. При этом адрес из ре-, гистра 52 через блок 59, блок 20 и регистр 11 записывается в память 3, откуда через блок 21 и шину 51 вы дается идентификатор тома из таблицы устойчивых ошибок и записывается в регистр 14,

В седьмой микрокоманде проверяется устойчивость анализируемой ошибки. При этом блок 4 сравнивает содержимое регистров 14, 15, Одновременно через элемент 67, формирователь 72 содержимое регистра 52 увеличивается на единицу. Распределитель 2 вырабатывает серию управляюш 1Х сигналов, позволяюш 1х повторить микрокоманды, начиная с шестой.

30

35

40

регистр 14, В четырнадцатом элементарном шаге содержимое регистра 52 таблицы устойчивых ошибок через бло 59, шину. 51 и блок 30 поступает в регистр 16, В пятнадцатом элементарном шаге в блоке 4 содержимое регист ров 14, 16 суммируется, результат суммирования передается через шину 51 и блок 20 в регистр 11, В шестнад цатом элементарном шаге через блок 21, шину 51 и блок 22 происходит запись идентификатора дорожки в регист 14,

В десятой микрокоманде осуществля ется сравнение идентификаторов дорожек в таблице устойчивых ошибок и об ласти регистрации ошибки. При этом в блоке 4 производится сравнение .содер жимого регистров 14, 15 и, если ре-г. зультат сравнения положительный, через элементы И 38, 39 устанавливаетс распределитель 2 в начальное состояние (ситема ожидает следующую операцию) , Элемент И 38 закрыт при отрицательном сравнении содержимого регистров 14, 15, поэтому через элемент И 69 и формирователь 74 содержимое регистра 54 смещения таблицы устойчивых ошибок увеличивается на единицу,

Из регистра 14 на элемент И 42 пе редается признак последнего идентифи катора дорожки. При наличии этого

45

50

Q

15

0

25 смешения таблицы устойчивых ошибок через шину 51 и блок 22 поступает в.

При сравнении содержимого регистров 14,. 15 на выходе элемента И 38 появляется сигнал, разрешающий распределителю 2 выработать следующею серию управляющих сигналов.

Одновременно со сравнением содержимого регистра 14, 15 на элемент И 42 поступает признак последнего идентификатора тома из первого регистра

14и при несравненйи идентификаторов томов сигнал с выхода элемента И побуждает распре делит ель 2 вырабатывать управляющие сигналы, позволяющие выполнить одиннадцатую микрокоманду,

В восьмой микрокоманде осуществляг ется запись идентификатора дорожки из области регистрации ошибки в регистр

15из формирователя 1 через шину 51,

В девятой микрокоманде осуществляется считывание идентификатора дорожки по смещению в строке таблицы устойчивых ошибок . В тринадцатом элементарном шаге содержимого регистра 54

5 смешения таблицы устойчивых ошибок через шину 51 и блок 22 поступает в.

0

5

0

регистр 14, В четырнадцатом элементарном шаге содержимое регистра 52 . таблицы устойчивых ошибок через блок 59, шину. 51 и блок 30 поступает в регистр 16, В пятнадцатом элементарном шаге в блоке 4 содержимое регистров 14, 16 суммируется, результат суммирования передается через шину 51 и блок 20 в регистр 11, В шестнадцатом элементарном шаге через блок 21, шину 51 и блок 22 происходит запись идентификатора дорожки в регистр 14,

В десятой микрокоманде осуществляется сравнение идентификаторов дорожек в таблице устойчивых ошибок и области регистрации ошибки. При этом в блоке 4 производится сравнение .содержимого регистров 14, 15 и, если ре-г. зультат сравнения положительный, через элементы И 38, 39 устанавливается распределитель 2 в начальное состояние (ситема ожидает следующую операцию) , Элемент И 38 закрыт при отрицательном сравнении содержимого регистров 14, 15, поэтому через элемент И 69 и формирователь 74 содержимое регистра 54 смещения таблицы устойчивых ошибок увеличивается на единицу,

Из регистра 14 на элемент И 42 передается признак последнего идентификатора дорожки. При наличии этого

5

0

признака и при отрицательном резуль- -тате сравнения через элементы И 42, . 46 сигнал позволяет настроить распределитель 2 на выполнение одиннадцатой микрокомавды,

В одиннадцатой микрокоманде осуществляется загрузка регистра 53 адреса таблицы неустойчивых ошибок. Поэтому в восемнадцатом элементарном шаге формирователь 5 через шину 51, блок 20 и регистр 1 1 задает адрес .. .. операции, В девятнадцатом элементарном шаге через блок 2I из памяти 3 в шину 51 выдается адрес таблицы неустойчивых ошибок, который через блок 58 записывается в регистр 53,

В двенадцатой микрокоманде производится запись идентификатора тома из формирователя 7 в регистр 15,

В тринадцатой микрокоманде осуществляется считывание из памяти 3 идентификатора тома, находящегося в таблице неустойчивых ошибок, В двадцать первом элементарном шаге через блок 60 и шину 5I выдается содержимое регистра 53 адреса таблицы неустойчивых ошибок, которое через блок 20 записывается в регистр 11, В двадцать втором элементарном шаге через блок 21 в шину 51 выдается идентификатор тома из первой строки таблицы неустойчивых ошибок и записывается в регистр 14,

В четырнадцатой микрокоманде производится сравнение содержимого регистров 14, 15 (идентификаторов томов). Это осуществляется в двадцать третьем элементарном шаге. Сигнал от

10

15

регистр 14, С этой целью в двадцать пятом элементарном шаге через блок 60, шину 51 адрес строки таблицы неустойчивых ошибок записывается через блок 3Q в регистр 16, В двадцать шестом элементарном шаге через блок 62 содержимое регистра 55 смещения передается в шину 51, а затем в регистр 14, В двадцать седьмом элементарном шаге в блоке 4 происходит суммирование содержимого регистров 14, 16,Одновременно разрешается запись полученного адреса через блок 25, шину 51 и блок 20 в регистр 11, В двадцать восьмом элементарном шаге через блок 21 в шину 51 выдается идентификатор дорожки из таблицы неустойчивых ошибок, который через блок 22 записывается в регистр 14,

В семнадцатой микрокоманде в двадцать девятом элементарном шаге происходит сравнение идентификаторов дорожек. При отрицательном результате

25 сравнения управляющим сигналом элемент И 38 не открывается, Одновре 4ен- но появлякяцийся сигнал от элемента И 70 и формирователя 75 увеличивает содержимое регистра 55 смещения на

30 единицу. Повторяются шестнадцатая и семнадцатая микрокоманды. При положительном результате сравнения идентификаторов дорожек на выходе элемента И 38 появляется сигнал, который нас„ траивает распределитель 2 на выра20

ботку следующей серии управляющих сигналов (следующей микрокоманда).

Если .результат сравнения отрицательный и пришел И8 регистра 14 на . элементам 68 проходит через фор мир о- 40 элемент И 42 признак последнего иден- ватель 73, и содержимое регистра 53тификатора дорожки, то через элемент

увеличивается на единицу. Распределитель 2 вырабатывает управляюшие сигИ -44 распределитель 2 настраивается на выполнение микрокоманды, начиная с двадцать( второй,

налы, позволяющие повторить микрокоманды тринадцать и четырнадцать.

При отрицательном результате сравнения сигнал с выхода элемента И 45 воздействует на распределитель 2 и позволяет выполнять микрокоманды, начиная с двадцать первой,

В пятнадцатой микрокоманде проводится запись идентификатора дорожки из области регистрации оваибки в регистр 15, Это осуществляется в двадцать четвертом элементарном шаге,

В шестнадцатой микрокоманде осуществляется сштывание идентификатора дорожки из выбраннЪй строки таблицы неустойчивых ошибок и его запись в

5

регистр 14, С этой целью в двадцать пятом элементарном шаге через блок 60, шину 51 адрес строки таблицы неустойчивых ошибок записывается через блок 3Q в регистр 16, В двадцать шестом элементарном шаге через блок 62 содержимое регистра 55 смещения передается в шину 51, а затем в регистр 14, В двадцать седьмом элементарном шаге в блоке 4 происходит суммирование содержимого регистров 14, 16,Одновременно разрешается запись полученного адреса через блок 25, шину 51 и блок 20 в регистр 11, В двадцать восьмом элементарном шаге через блок 21 в шину 51 выдается идентификатор дорожки из таблицы неустойчивых ошибок, который через блок 22 записывается в регистр 14,

В семнадцатой микрокоманде в двадцать девятом элементарном шаге происходит сравнение идентификаторов дорожек. При отрицательном результате

5 сравнения управляющим сигналом элемент И 38 не открывается, Одновре 4ен- но появлякяцийся сигнал от элемента И 70 и формирователя 75 увеличивает содержимое регистра 55 смещения на

0 единицу. Повторяются шестнадцатая и семнадцатая микрокоманды. При положительном результате сравнения идентификаторов дорожек на выходе элемента И 38 появляется сигнал, который настраивает распределитель 2 на выра0

ботку следующей серии управляющих сигналов (следующей микрокоманда).

И -44 распределитель 2 настраивается на выполнение микрокоманды, начиная с двадцать( второй,

В восе мнадцатой микрокоманде осуществляется загрузка идентификатора объекта контроля из области регистрации, ошибки в регистр 15, Поэтому в тридцатом элементарном шаге разрешается выдача из формирователя 7 . .: . идентификатора объекта контроля в шину 5 1 , В этом же элементарном шаге производится запись идентификатора объекта в регистр 15,

В регистр 14 помещается идентификатор объекта из выбранной строки таблицы неустойчивых ошибок, Дая этот го в тридцать первом элементарном шаге через блок 60 и шину 51 содержимое.

регистра 53 таблицы неустойчивых оши бок передается в регистр 16.

В девятнадцатой микрокоманде в тридцать втором элементарном шаге че рез блок 62, шину 51, блок 22 содержимое регистра 56 смещения помещается в регистр 14. В тридцать третьем элементарном шаге происходит суммиро -вание содержимого регистра 14, 16 и прохождение результата суммирования через блок 25, шину 51 и блок 20 в регистр II, В тридцать четвертом эле йентарном шаге из памяти 3 идентификатор объекта через блок 21, шину 51 и блок 22 перемещается в регистр 14, В двадцатой микрокоманде происходит сравнение идентификаторов объектов в регистрах 14, 15 в тридцать пятом элементарном шаге. При отрицательном результате сравнения распределитель 2 вырабатывает управляющие сигналы, которые позволяют повторить микрокоманды девятнадцать, двадцать, Одновременно сигналом от элемента И 71 и формирователя 76 содержимое регистра 56 смещения увеличивается на единицу.

На элемент И 42 передается признак последнего идентификатора объекта. При отрицательном результате :., сравнения и признаке последнего иденг тификатора объекта открывается эле- мент И 43, сигнал с выхода которого настраивает распределитель 2 на выполнение тридцать четвертой микрокоманды. При положительном результате сравнения срабатывает элемент И 38 и распределитель 2 вырабатывает управляющие сигналы, позволяющие выполнять микрокоманды, начиная с двадцать четвертой,

В двадцать первой микрокоманде производится запись идентификатора тома в таблицу неустойчивых ошибок. Для этого в тридцать шестом элементарном шаге содержимое регистра 53 через блок 60, шину 51 и блок 20 поступает в регистр П. В тридцать седьмом элементарном шаге идентификатор тома из формирователя 7 выдается в шину 51 и через блок 26,

В двадцать второй микрокоманде осуществляется запись идентификатора дорожки в таблицу неустойчивых ошибок, С этой целью, в тридцать восьмом элементарном шаге разрешается прохождение содержимого регистра 55 через блок 62, шину 51 и блок 22 в регистр

58§74 8

14, В тридцать девятом шаге осуществляется суммирование регистров 14, 16 и прохождение результата суммиро- вания через блоки 25, 21 и шину 51 в регистр I 1 (в регистре 16 к этому времени находится содержимое регистра адреса таблицы неустойчивых ошибок).

10 сороковом элементарном шаге идентификатор дорожки из формирователя 7 через блок 26 записывается в память 3,

В двадцать третьей микрокоманде 15 осуществляется запись идентификатора объекта в таблицу неустойчивых ошибок. Микрокоманда состоит из трех элементарных шагов: сорок первого,сорок второго и сорок третьего, Выпол- 20 няется она аналогично двадцать второй микрокоманде, только в сорок первом элементарном шаге содержимое регистра 56 через блок 63, шину 51 и блок 22 подается в регистр 14, 25 В двадцать четвертой микрокоманде производится формирова ние диагностического образа ошибки, В сорок четвертом элементарном шаге из формирователя 7 содержимое байтов уточненно- 30 го состояния поступает на элементы И 31 и дешифратор 19. В зависимости от содержимого байта на выходе дешифратора 19 появляется сигнал, разрешающий прохождение байтов уточнен- 2g ного состояния только через те элементы И 31, которые соответствуют диагностическому образу, В этом же элементарном шаге происходит запись образа ошибки в регистр 13, 40 В двадцать пятой микрокоманде в регистр 80 адреса массива ошибок записывается первая строка массива ошибок. Для этого в сорок пятом элементарном шаге из формирователя 5 через 5 шину 51, блок 20 в регистр 11 записывается адрес операции, В сорок шестом элементарном шаге адрес массива ошибок через блоки 21, 83 и шину 51 записывается в регистр 80, В этом же Q элементарном шаге содержимое формирователя 5 увеличивается на единицу. Одновременно адрес масок ошибок записывается в регистр 82 адреса масок ошибок,

g В двадцать шестой микрокоманде в сорок седьмом элементарном шаге из ; , формирователя 7 через шину 51 и блок 22 идентификатор объекта записывается в регистр 14,

в двадцать седьмой микрокоманде заполняется регистр 98 адреса таблицы весовых коэффициентов. Поэто 1у в сорок восьмом элементарном шаге разрешается запись в регистр П адреса операции. В сорок девятом элементарном шаге из памяти 3 через блок 21, шину 51 и блок 99 адрес весовых козф145887410.

траивается на выполнение тридцать четвертой микрокоманды.

Если первый бит регистра 13 равен единице, то по сигналу с элемента И 41 распределитель 2 выбирает управляющие сигналы, которые выполняют следующие микрокомандыt

В тридцать первой микрокоманде в

Г/ие„:л Гс:,.аегг;в™;;р.. с;- ,„ ; : --:--- 15

новременно содержимое формирователя 5 увеличивается на единицу.

В двадцать восьмой микроком анде идентификатор устройства из регистра 98 записывается в регистр 15. С этой целью в пятидесятом элементарном шаге и через элемент И 102 осуществляется выдача в шину 51 идентификатора объекта, В этом же элементарном шаге информация из шины 51 помещается в

регистр 15.

В двадцать девятой микрокоманде в пятьдесят первом элементарном шаге производится сравнение содержимого регистров 14, 15 и при отрицательном результате сравнения блок 100 не открывается и открывается при положит тельном результате сравнения. При отсутствии сигнала на выходе элемента И 38 распределитель 2 повторяет серию управляющих сигналов, которые повторяют выполнение микрокоманды двадцать семь - двадцать девять. Одновременно через элемент ИЛИ 101 содержимое регистра 98 адреса весовых коэффициентов увеличивается на единицу.

В тридцатой микрокоманде проверяется содержимое регистра 13 образа ошибки. С этой целью в пятьдесят втором элементарном шаге обеспечивается сдвиг влево содержимого регистра 13 и через элемент ИЛИ 36 и формирователь 47 уменьшает содержимое счетчика 17 на единицу. Распределитель 2 повторяет тридцатую микрокоманду. Одновременно через элемент ИЛИ 92 сот. держимое регистра 80 увеличивается

на единицу.

В этом же шаге при нулевом значении счетчика 17 формирователь 47 побуждает распределитель 2 начать выполнение тридцдть второй.микрокоманды.

Одновременно сигналом с выхода элемента И 97 содержимое счетчика 91 уменьшается на единицу. Нулевое значение счетчика через блок 89 передается в распределитель 2 и он насг

открывается блок 86 и содержимое регистра 80 через шину 51 и блок.20 записывается в регистр П. В пятьдесят четвертом элеметарном шаге через блок 21, шину 51 и блок 23 маска ошибки

20

30

записывается в регистр 15, В пятьдесят пятом элементарном шаге производится наложение масок регистров 14 и 15. В пятьдесят шестом элементарном шаге результат наложения записывается через блок 25, 22 в регистр 14. В этом же шаге обеспечивается запись результата наложения в регистр 81 маски. Одновременно сигнал увеличивает 25 содержимое регистра 80 на единицу. Выполняются микрокоманды, начиная с тридцатой,

В тридцать второй микрокоманде производится специальный доступ к памяти 3. С этой целью в пятьдесят . седьмом элементарном шаге записывается исходный адрес масок ошибок через блок 88, шину 51 и блок 20 в регистр

11.

В пятьдесят восьмом элементарном шаге записывается содержимое регистра 81 маски в регистр 12.

В пятьдесят девятом элементарном шаге обеспечивается выдача в шину 51- результата специального методу доступа. Одновременно открыт блок 22 и информация из шины 51 записывается в

регистр 14.

В тридцать третьей микрокоманде 4g вырабатывается дополнение до расши- ренного диагностического образа. С этой целью в шестидесятом элементарном шаге через блок 29 образ ошибки выдается в шину 51 и далее через блок 23 в регистр 15,

В шестьдесят первом элементарном шаге в блоке 4 осуществляется операция сложения по модулю 2. Результат операции записывается через блок 25, шину 51, блок 28 в регистр 13 об раза ошибок. Выполняется тридцатая микрокоманда, по которой обеспечивав ется запись маски ошибки в регистр 14.

35

40

50

55

; : --:--- 5

открывается блок 86 и содержимое регистра 80 через шину 51 и блок.20 записывается в регистр П. В пятьдесят четвертом элеметарном шаге через блок 21, шину 51 и блок 23 маска ошибки

0

30

записывается в регистр 15, В пятьдесят пятом элементарном шаге производится наложение масок регистров 14 и 15. В пятьдесят шестом элементарном шаге результат наложения записывается через блок 25, 22 в регистр 14. В этом же шаге обеспечивается запись результата наложения в регистр 81 маски. Одновременно сигнал увеличивает 25 содержимое регистра 80 на единицу. Выполняются микрокоманды, начиная с тридцатой,

В тридцать второй микрокоманде производится специальный доступ к памяти 3. С этой целью в пятьдесят . седьмом элементарном шаге записывается исходный адрес масок ошибок через блок 88, шину 51 и блок 20 в регистр

11.

В пятьдесят восьмом элементарном шаге записывается содержимое регистра 81 маски в регистр 12.

В пятьдесят девятом элементарном шаге обеспечивается выдача в шину 51- результата специального методу доступа. Одновременно открыт блок 22 и информация из шины 51 записывается в

регистр 14.

В тридцать третьей микрокоманде 4g вырабатывается дополнение до расши- ренного диагностического образа. С этой целью в шестидесятом элементарном шаге через блок 29 образ ошибки выдается в шину 51 и далее через блок 23 в регистр 15,

В шестьдесят первом элементарном шаге в блоке 4 осуществляется операция сложения по модулю 2. Результат операции записывается через блок 25, шину 51, блок 28 в регистр 13 образа ошибок. Выполняется тридцатая микрокоманда, по которой обеспечивав-. ется запись маски ошибки в регистр 14.

35

40

50

55

111458974

В тридцать четвертой микрокомандеми с третьего по пятый блоков элеменв шестьдесят втором элементарном ша- тов И и фррмирователя адреса априор- ге сдвигается влево содержимое ре- ной информации об ошибке в логичесгистра 81. Одновременно при нулевомкой схеме, синхровход которого соеди-.

значении старшего бита регистра 81нен через синхрошину с синхровходаэлемент 96 закрыт и повторяется вы-ми с первого по седьмой блоков элеполнение тридцать второй микрокоманды, ментов И формирователя адреса опера- При ненулевом значении старшего битации, вxoдa м с первого по четвертый,

-регистра 81 маски элемент И 96 открыт ю элементов ИЛИ, синхровходом первого и выполняется следующая мкpoкoмaндa. элемента И и выходом распределителя

В этом же шаге через элемент ИЛИ . синхросигналов, такто.вый вход которо- 93 содержимое счетчика 90 уменьшает-го соединен с выходом генератора такся на единицу. Одновременно при ну-товых импульсов, выход пятого блока

левом значении счетчика 90 открываетг 15 элементов И через регистр операции ся элемент И 97 и распределитель 2 .соединен с входом первого дешифратопереводится в исходное положение,ра, выход которого через шину управВ этом же шаге сигнал через эле-ления ссСединен с управляю1дим входом

мент ИЛИ 101 увеличивает содержимоераспределителя синхросигналов, выход

регистра 98 адреса таблицы весовых 20 первого блока элементов И через пер- коэффициентов на единицу,вый регистр адреса соединен с первым

В тридцать пятой микрокоманде осу- адресным входом памяти, информацион- ществляется формирование весовых ко- ный вход которой соединен с выходом ,эффициентрв ошибок, С этой целью вседьмого блока элементов И, а выход шестьдесят третьем элементарном шаге 25 с информационным входом второго бло- открывается элемент И 102, через ко-ка элементов И, выходы третьего и четторый содержимое регистра 98 записы-вертого блоков элементов И через совается в регистр 11, В шестьдесятответственно первый и второй буферные

четвертом элементарном шаге обеспечи- регистры соединены с первым и вторым вается запись в регистр 14 коэффици-г.. зо информац ионными входами арифметико- ента веса ошибки. Одновременно черезлогического блока, синхровходы соедиэлемент ИЛИ 101 обеспечивается увели- нены с выходами с первого по четвер- чение содержимого регистра 98 на еди- тый элементов ИЛИ, а информационный щ цу выход и выход признака логического

В шестьдесят пятом элементарном сравнения соединены с информациоины- шаге обеспечивается выдача в шину 51ми входами соответственно шестого

содержимого регистра 98, которое за-блока элементов И и первого элемента

писывается в регистр 11,ТВ шестьде-И, отличающееся тем, что,

сят шестом шаге вес ошибки выдаетсяс целью повьш1ения достоверности и

в шину 51 и далее в регистр 15,до быстродействия устройства, в него

В тридцать шестой микрокоманде в . введены формирователь номера отказав-, шестьдесят седьмом элементарном шагешего элемента, формирователь адреса

в блоке 4 складывается содержимое ре- таблицы весовых коэф(|Еициентов, фор- гистров 14, 15 и результат суммирова- мирователь адреса априорной информа- ния через шину 51, блоки 25, 26 за- g ции об ошибках в магнитном накопите- писывается в память 3 по адресу, со- ле, счетчик, дешифратор, четыре бло- держащемуся в регистре П.ка элементов И, регистр образа ошибки, буферный регистр, восемь элемен- Формула изобретениятов И, два формирователя импульсов,

-д два элемента ИЛИ, группа элементов И,

I, Устройство для формирования ди- регистр адреса, причем управляющий агностической информации о вычислите- вход, информационный вход и синхро- льной системе, содержащее формирова-. вход формирователя адреса априорной тель адреса операции, выход и инфор-информации об ошибках в магнитном

ГмационньА вход которого соединены че- gg накопителе соединены соответственно рез адресно-информационную шину с ий- через шину управления с выходом вто- формационным входом первого блокарого элемента И,.через адресно-инфор

элементов И, выходом второго Влока :- . мационную шину - с выходом второго элементов И и информационными блока-блока элементов И и с синхрошиной

устройства, а выход через адресно- информационную шину - с информационным входом первого блока элементов И, второй адресный вход памяти че- ,рез второй регистр адреса соединен с выходом восьмого блока элементов И, информационный вход и синхровход котог рого соединены соответственно через адресно-информационную шину с выхо- дом формирователя адреса априорной информации об ошибке в логической схеме и синхрошиной устройства, выходы выдачи старших байтов ошибок и выдавторого блока элементов И и информационным входом первого блока элемен;тов И, выход шестого элемента ИЛИ чег- рез второй формирователь импульсов

,соединен с информационным входом счетчика, выходы третьего и четвертого элементов И и управляющий выход формирователя номера отказавшего элемента соединены через шину управления с управляющим входом распределителя синхросигналов и выходами второго и с шестого по девятый элементов И, первые входы которых соединены с син

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1667068A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Вычислительное устройство | 1981 |

|

SU993270A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

Изобретение относится к вычислительной технике и может быть использовано для распознавания техническо го состояния систе1 1 внешних запоми- наювц х устройств прямого доступа. Целью изобретения является повьшение достоверности и быстродействия уст

чи младших байтов ошибок формировате- ig хрошиной устройства, а вторые входы ля адреса априорной информации об ошибке в логической схеме соединены с первыми и вторыми входами элементов И группы, выходы которых соединены с группой входов регистра образа ошибки, вход фактической, информации об ошибке ко- торого соединен с выходом девятого блока элементов И, входы которого соединены соответственно через адресно-информационную шину с выходом шестого блока элементов И и синхрошиной устройства, выход выдачи управляющего байта формирователя адреса априорной информации об ошибке в логической схеме через второй дешифрат . тор соединен с третьими входами эле- ментов И группы, четвертые входы кот торых соединены с синхрошикой устройства, соединенной через пятый элемент ИЛИ с входом первого формирователя импульсов, выход которого соединен с синхровходами р егистра адреса ошибки и счетчика, выход которого соединен . с первым входом третьего элемента И, выход наличия диагностического признака ошибки и информационный выход регистра образа ошибки соединены с первыми входами соответственно четг-. вертого элемента И и десятого блока элементов И, выход которого соединен с информационным входом седьмого блока элементов И, синхрошина устройства соединена с вторыми ,входа « третьего и четвертого элементов И, десятого блока элементов И, первыми входами одиннадцатого блока элементов И и пятого элемента И, входами шестого элемента ИЛИ и синхровходами формирователя номера отказавшего элемента и формирователя адреса таблицы весовых коэффициентов, информационные входы и выходы которых соединены через адресно-информационную шину с выходом

20

30

35

с выходом первого элемента И, третьи входа с шестого по девятый элемент рв И соединены с выходом пятого элемента И, второй вход которого соединен с выходом признака последнего идентификатора тома арифметико-логического блока, третий информационный ёход которого через третий буферный регистр соединен с выходом одиннадца- 25 того блока элементов И, второй вход которого соединен с адресно-информационной шиной устройства, управляющий вход формирователя адреса таблицы весовых коэффициентов соединен с выходом второго элемента И через адресно- информационную шину устройства.

2, Устройство по п.1, о т л и ч а- ю щ е е с я тем, что формирователь адреса априорной информации об ошибках в магнитном накопителе содержит пять, регистров, семь блоков элементов И, три элемента ИЛИ, восемь формирователей импульса, пять элементов И, причем информационные входы первого и второго блоков элементов И соединены с информационным входом формирователя, выход которого соединен с выходами, с третьего по седьмой блоков элементов И, информационные входы которых соединены с выходами соответственно с первого по пятый регистров, управляющие входы которых соединены с выходами соответственно с первого по пятый формирователей импульса, входы которых соединены с выг ходами с первого по пятый элементов И, первые входы которых соединены с управляющим входом формирователя, о. , синхровход которого соединен С синхровходами с первого по седьмой блоков элементов И, с вторыми входами с первого по пятый элементов И и входами с первого по третий элементов ИЛИ, выходы которых через соответственно

40

45

50

55

0

0

5

с выходом первого элемента И, третьи входа с шестого по девятый элемент рв И соединены с выходом пятого элемента И, второй вход которого соединен с выходом признака последнего идентификатора тома арифметико-логического блока, третий информационный ёход которого через третий буферный регистр соединен с выходом одиннадца- 5 того блока элементов И, второй вход которого соединен с адресно-информационной шиной устройства, управляющий вход формирователя адреса таблицы весовых коэффициентов соединен с выходом второго элемента И через адресно- информационную шину устройства.

2, Устройство по п.1, о т л и ч а- ю щ е е с я тем, что формирователь адреса априорной информации об ошибках в магнитном накопителе содержит пять, регистров, семь блоков элементов И, три элемента ИЛИ, восемь формирователей импульса, пять элементов И, причем информационные входы первого и второго блоков элементов И соединены с информационным входом формирователя, выход которого соединен с выходами, с третьего по седьмой блоков элементов И, информационные входы которых соединены с выходами соответственно с первого по пятый регистров, управляющие входы которых соединены с выходами соответственно с первого по пятый формирователей импульса, входы которых соединены с выг ходами с первого по пятый элементов И, первые входы которых соединены с управляющим входом формирователя, о. , синхровход которого соединен С синхровходами с первого по седьмой блоков элементов И, с вторыми входами с первого по пятый элементов И и входами с первого по третий элементов ИЛИ, выходы которых через соответственно

0

5

0

5

15 1458874

с шестого по восьмой формирователита И, выход третьего элемента ИЛИ

соединен -с информационным входом перимпульса соединены с информационными входами соответственно с третьего по. пятый регистров, выходы первого и второго блоков элементов И соединены с информационными входами соответственно первого и второго регистров,

элемента И, выход которого и выход четвертого элемента ИЛИ соединены, соответственно с управлягацим и инфор- . мационным входами второго счетчика, вы10 ход которого соединен с информационным входом седьмого блока элементов И, выходы которого и .первого, второго элементов И соединены с управляющим выходом формирователя,

15

4, Устройство по п. 1 , о- т л и ч а- ю щ е е с я тем, что формирователь адреса таблицы весовых коэффициентов содержи регистр, два блока элеменJjL V,WVJ1 & V. .%j- ,. -- .--r

ТИЙ регистров, информационные выходы JQ ов И, элемент ИЛИ, элемент И, прикоторых соединены с информационными входами соответственно с четвертого по шестой блоков элементов И, выходы которых соединены с информационным

чем информационные вход и выход формирователя соединены с информационным входом первого блока элементов И и выходами элемента И и второго блоКОТОРЫЛ I- ri ti4jvf r-i т

выходом формирователя, синхровход ко- 25 ка элементов И, управляющий вход л.л. ,-. rt -чт ЮГГ СТ WTTLT ХЛ ffVf ПП М

торого соединен с входами с первого по четвертый элементов ИЛИ и синхровход ами с первого по седьмой блоков элементов И и первого,второго элементов И, выход первого элемента ИЛИ соединен с управляюш:им входом первого регистра, выход второго элемента ИЛИ соединен с управляющими входами первого счетчика и второго регистра, упг равляющий выход которого соединен с

информационным входом первого элемен- элементов И.

торого соединен с управляющим входом формирователя, синхровход которого соединен с синхровходами первого и .- второго блоков элементов И, элемента И 30 и входами элемента ИЛИ, выходы которого и первого блока элементов И соединены с управляющим и информационным входами регистра, информационные выходы которого соединены с информационными

входами элемента И и второго блока оэ

ного счетчика, выход которого соединен с информационным входом второго

элемента И, выход которого и выход четвертого элемента ИЛИ соединены, соответственно с управлягацим и инфор- мационным входами второго счетчика, выход которого соединен с информационным входом седьмого блока элементов И, выходы которого и .первого, второго элементов И соединены с управляющим выходом формирователя,

4, Устройство по п. 1 , о- т л и ч а- ю щ е е с я тем, что формирователь адреса таблицы весовых коэффициентов содержи регистр, два блока элемен-1.--r

ов И, элемент ИЛИ, элемент И, И, элемент ИЛИ, элемент И, причем информационные вход и выход формирователя соединены с информационным входом первого блока элементов И и выходами элемента И и второго бло-- r-i т

ка элементов И, управляющий вход .л. ,-. rt -чт ЮГГ СТ WTTLT ХЛ ffVf ПП М

элементов И.

торого соединен с управляющим входом формирователя, синхровход которого соединен с синхровходами первого и .- второго блоков элементов И, элемента И и входами элемента ИЛИ, выходы которого и первого блока элементов И соединены с управляющим и информационным входами регистра, информационные выходы которого соединены с информационными

входами элемента И и второго блока

| Устройство для обработки статистических данных о работе аппаратуры вычислительных машин и систем | 1982 |

|

SU1086439A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Амперометрический способ измерения концентрации кислорода в газовых смесях | 2017 |

|

RU2654389C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-02-15—Публикация

1986-04-25—Подача