Изобретение относится к вычислительной технике и может быть исполь- . зовано для сопряжения цифрового процессора обработки сигналов с элек- тронно-вычислительной машиной.

Целью изобретения является повышение коэффициента использования оборудования.

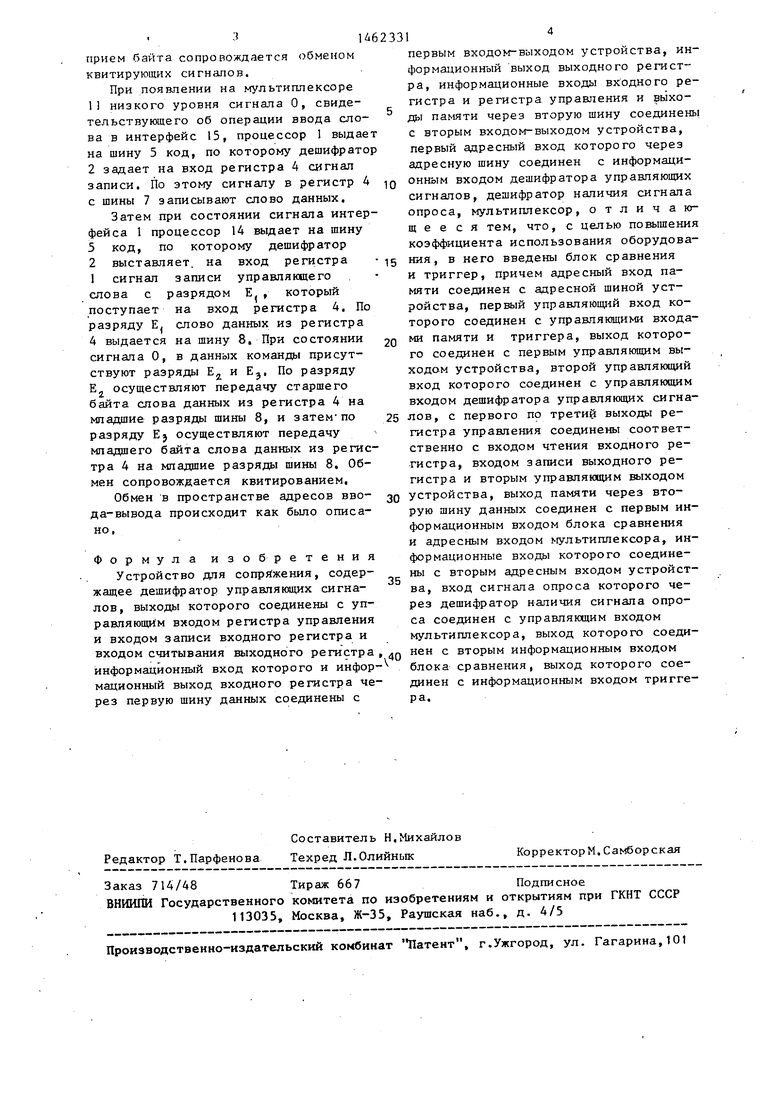

На чертеже приведена блок-схема п)эедпа-гаемого устройства.

1 Устройство содержит регистр 1 уп- р|авления, дешифратор 2 управлякядих сигналов, выходной регистр 3, входной регистр 4, адресную шину 5, память 61, шины 7 и 8 данных, триггер 9, блок 1|0 сравнения, мультиплексор 11, де- Шифратор 12 наличия . сигнала опроса, ход 13 сигнала опроса устройства, фоцессор 14 обработки сигналов, ин- т|ерфейс 15. ЭВМ,

Устройство работает под управлением программы процессора 14, которая йомещена в памяти 6, Чтение команд ИЗ памяти 6 происходит, выставлением шину 5 адреса команды. Адрес команды сопровождают сигналом, поступающим на Ьход управления памяти 6 , разрешая чте Ние. Считанное слово команды с выхода памяти 6 поступает на шину 7,и по ней . в пр.оцессор 14, Работа устройства основана на программном опросе процессором 14 состояния линий управления интерфейса 15 и формировании ответных сигналов на выходе регистра 1,в которы командой вывода заносится спово управления. Состояние линий управления Интерфейса 15 опрашивает мультиплексор 11, работа которого разрешается дешифратором 12 при наличии сигнала на входе 13.

Модифицированная команда проверки состояния внешних устройств, осуществляющая переход по адресу в зависимости от состояния сигнала на выходе триггера 9, выполняется следующим образом, В момент чтения из памяти 6 первого слова команды на адресный вход мультиплексора 11 с шины 7 поступает код, размещенный в неиспользованные разряды О, 1, 2 первого слова команды, Этим кодом при наличии сигнала на входе мультиплексора 11, пос тупакщего с выхода дешифратора 12, выбирается информационный вход мультиплексора 11, к которому подю1юче- на.опрашиваемая линия интерфейса 15, С выхода мультиплексора I 1 сигнал о состоянии выбранной линии поступает

5 0

5 о Q

д

5

50

на вход блока 10, не первом входе которого действует сигнал с шины 7. С выхода блока 10 сигнал поступает на вход триггера 9, состояние которого фиксируется задним фронтом сигнала на входе управления триггера 9. С выхода триггера 9 сигнал поступает на вход процессора 14. Если сигнал О, то осуществляется переход по адресу, указанному во втором слове команды. Если сигнал 1 , то следующая команда выбирается в естественном порядке. Для обмена одним словом в пространстве адресов памяти устройство следит за состоянием линий интерфейса 15 путем циклического выполнения команды с- соответствующей выборкой опрашиваемых линий. Если по интерфейсу 15 поступает низкий уровень сигнала, свидетельствующий об операции вывода данных из интерфейса 15 в устройство сопряжения, происходит . обмен словом посредством команды, при выполнении которой по адресу с младших разрядов шины5 и при наличии сигнала дешифратор 2 выдает на вход регистра 1 сигнал записи, по которому с шины 7 в регистр 1 записывают слово управления, В слове управления установлен разряд С , разрешающий по второму входу управления запись слова с шины 8 в регистр 3, и разряд , формирующий ответный низкий уровень сигнала квитирования; на соответствующей линии интерфейса 15, Затем командой устройство проверяет снятие интерфейсом 15 активного низкого уровня сигнала, и посредством команды регистр 1 снимает активный низкий уровень сигнала ХАСК, обмена одним сло-с вом завершается. Дешифратор 2, управ- .ляемый кодом с шины 5 и сигналом управления с процессора 14, выдает сигнал на вход регистра 3, данные из которого по этому сигналу поступают на . шину 7 и далее в процессор 14,

При появлении на мультиплексоре 11 сигнала 1, устройство сопряжения переходит в режим последовательного обмена байтами между процессором 14 и интерфейсом 15, Выданные в регистр 1 слова управления содержат разряды С, и Сj,поступающие с выхода регистра 1 на вход регистра 3. Разряд С обеспечивает прием в регистр 3 старшего байта слова с младших разрядов шины 8, а затем разряд Cj обеспечивает прием младшего разряда слова. Каждый

прием байта сопровождается обменом квитирующих сигналов.

При появлении на мультиплексоре 1 низкого уровня сигнала О, свидетельствующего об операции ввода слова в интерфейс 15, процессор 1 выдает на шину 5 код, по которому дешифратор 2 задает на вход регистра 4 сигнал

первым входом-выходом устройства, ин формационный выход выходного регистра, информационные входы входного ре гистра и регистра управления и выходы памяти через вторую шину соединень с вторым входом-выходом устройства, первый адресный вход которого через адресную шину соединен с информаци, ЗоДасЧ Иа DAW, cinv-iH л « - записи. По этому сигналу в регистр 4 ю онным входом дешифратора управляющих с шины 7 записывают слово данных.сигналов, дешифратор наличия сигнала

опроса, мультиплексор, отличаю щееся тем, что, с целью повышения коэффициента использования оборудоваЗатем при состоянии сигнала интерфейса 1 процессор 14 выдает на шину 5 код, по которому дешифратор 2 выставляет, на вход регистра 1 сигнал записи управляюцего слова с разрядом Е , который поступает на вход регистра 4. По разряду EJ слово данных из регистра 4 выдается на шину 8, При состоянии сигнала О, в данных команды присутствуют разряды Ej и Ej, По разряду Е, осуществляют передачу старшего байта слова данных из регистра 4 на младшие разряды шины 8, и затем-по разряду Е} осуществляют передачу младшего байта слова данных из регистра 4 на младшие разряды шины 8, Обмен сопровождается квитированием

опроса, мультиплексор, отличающееся тем, что, с целью повышения коэффициента использования оборудова15 ния, в него введены блок сравнения и триггер, причем адресный вход памяти соединен с адресной шиной устройства, первый управляющий вход которого соединен с управляклцими входами памяти и триггера, выход которого соединен с первым управляюш €м выходом устройства, второй управляющий вход которого соединен с управляющим входом дешифратора управляющих сигна25 лов, с первого по третий выходы регистра управления соединены соответственно с входом чтения входного регистра, входом записи выходного регистра и вторым управляющим выходом

20

Обмен в пространстве адресов вво- зо устройства, выход памяти через втода-вывода происходит как было описано,

Формула изобретения Устройство для сопряжения, содержащее дешифратор управляющих сигналов , выходы которого соединены с управляющим входом регистра управления и входом записи входного регистра и

35

рую шину данных соединен с первым информационным входом блока сравнения и адресным входом мультиплексора, информационные входы которого соединены с вторым адресным входом устройства, вход сигнала опроса которого через дешифратор наличия сигнала опроса соединен с управляющим входом мультиплексора, выход которого соедивходом считывания выходного реги стра , Q вторым информационным входом

информационный вход которого и инфор- блока сравнения, выход которого соемационный выход входного регистра че-динен с информационным входом триггерез первую шину данных соединены сра.

первым входом-выходом устройства, ин формационный выход выходного регистра, информационные входы входного регистра и регистра управления и выходы памяти через вторую шину соединень с вторым входом-выходом устройства, первый адресный вход которого через адресную шину соединен с информационным входом дешифратора управляющих сигналов, дешифратор наличия сигнала

опроса, мультиплексор, отличающееся тем, что, с целью повышения коэффициента использования оборудования, в него введены блок сравнения и триггер, причем адресный вход памяти соединен с адресной шиной устройства, первый управляющий вход которого соединен с управляклцими входами памяти и триггера, выход которого соединен с первым управляюш €м выходом устройства, второй управляющий вход которого соединен с управляющим входом дешифратора управляющих сигналов, с первого по третий выходы регистра управления соединены соответственно с входом чтения входного регистра, входом записи выходного регистра и вторым управляющим выходом

устройства, выход памяти через вто

рую шину данных соединен с первым информационным входом блока сравнения и адресным входом мультиплексора, информационные входы которого соединены с вторым адресным входом устройства, вход сигнала опроса которого через дешифратор наличия сигнала опроса соединен с управляющим входом мультиплексора, выход которого соеди

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

Изобретение относится к вычислительной технике и может быть использовано для српряжения цифрового процессора обработки сигналов с ЭВМ. Целью изобретения является повышение коэффициента использования оборудования. Устройство содержит регистр 1 управления, дешифратор 2 управляющих сигналов, выходной регистр 3, входной регистр 4, адресную шину 5, память 6, шины 7 и 8 данных, триггер 9, блок 10 сравнения, мультиплексор 11, Дешифратор 12 наличия сигнала опроса, вход 13 сигнала опроса устройства, процессор 14 обработки сигналов, интерфейс 15 ЭВМ. Устройство работает под управлением nporpaMNbi процессора 14, которая помещена в па мяти 6. Чтение команд из памяти 6 происходит выставлением на шину 5 адреса команды. Адрес команды сопровождают сигналом, пocтyпaюп: м на вход управления памяти 6, разрешая чтение. Считанное слово команды с выхода памяти 6 поступает на шину 7 и по ней в процессор 14. Работка устройства основана на программном опросе процессора 14 состояния линий управления интерфейса 15 и формировании ответных сигналов на выходе регистра 1, в который командой вывода заносится слово управления. 1 ил. i (Л G: 4 О5 Ю оо со

| Устройство для связи независимо работающих подсистем обработки данных | 1984 |

|

SU1166129A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для организации мультипроцессорной иерархической системы | 1984 |

|

SU1295409A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-02-28—Публикация

1987-07-17—Подача