6

5

Од ts9

lif 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501276A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1985 |

|

SU1396280A2 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1985 |

|

SU1275777A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

Изобретение относится к вычислительной технике. Его использование в системах обработки дискретной нации позволяет повысить быстродействие преобразователя. Благодаря вне-- дению блока 1 преобразования параллельного кода в последовательности импульсов и соответствующему подключению входов преобразователя формирование выходного кода происходит за меньшее число тактов 1 з.п, ф-лы, 3 ил.

А 3

фиг. J

10

15

Изобретение относится; к вычислительной технике и может быть использовано Е системах обработки дискретной информации.

Цель изобретения - повышение быстродействия преобразователя.

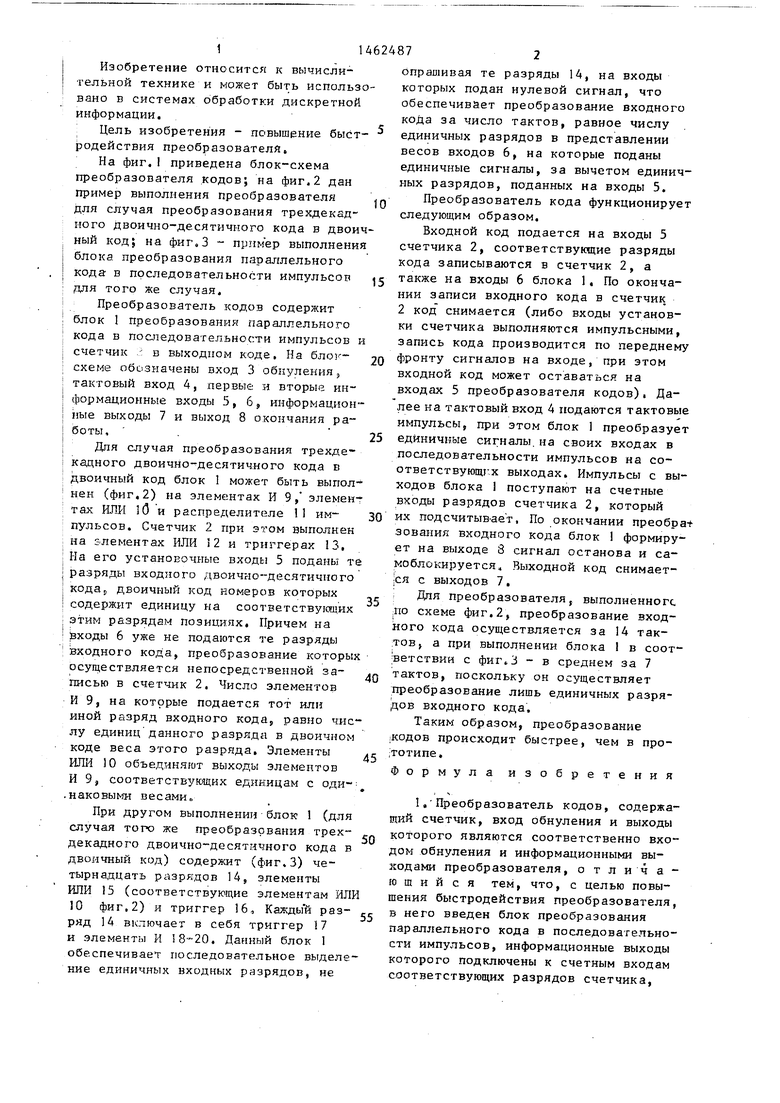

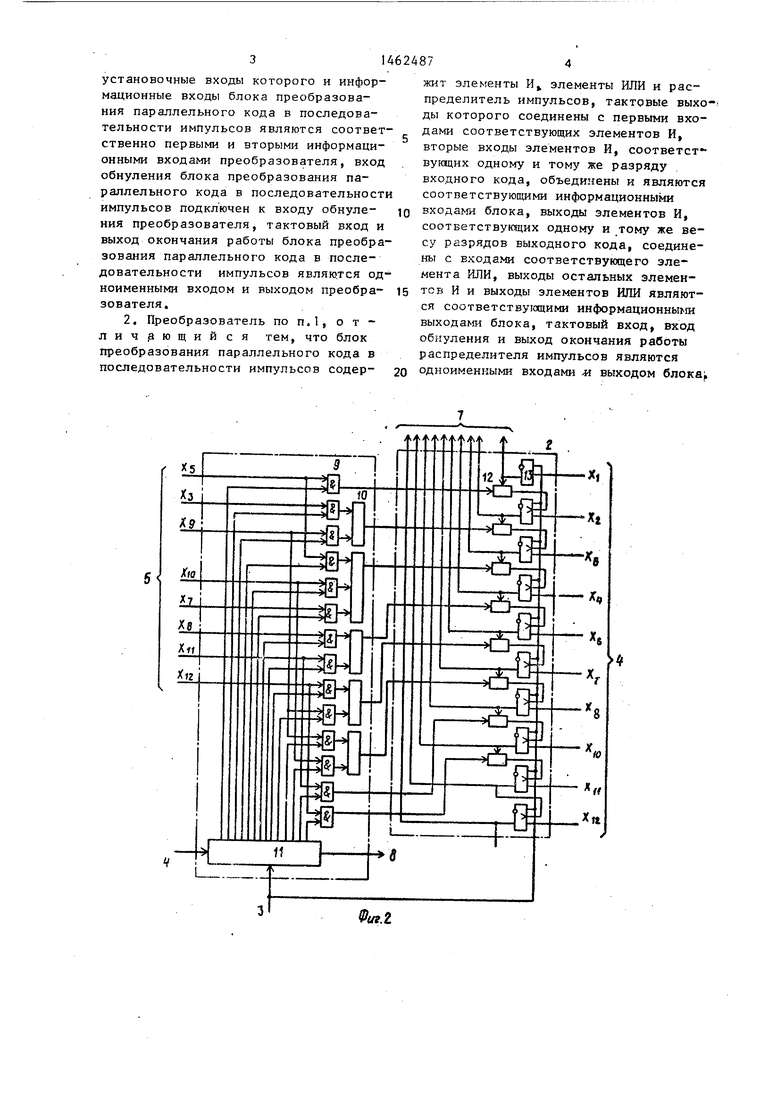

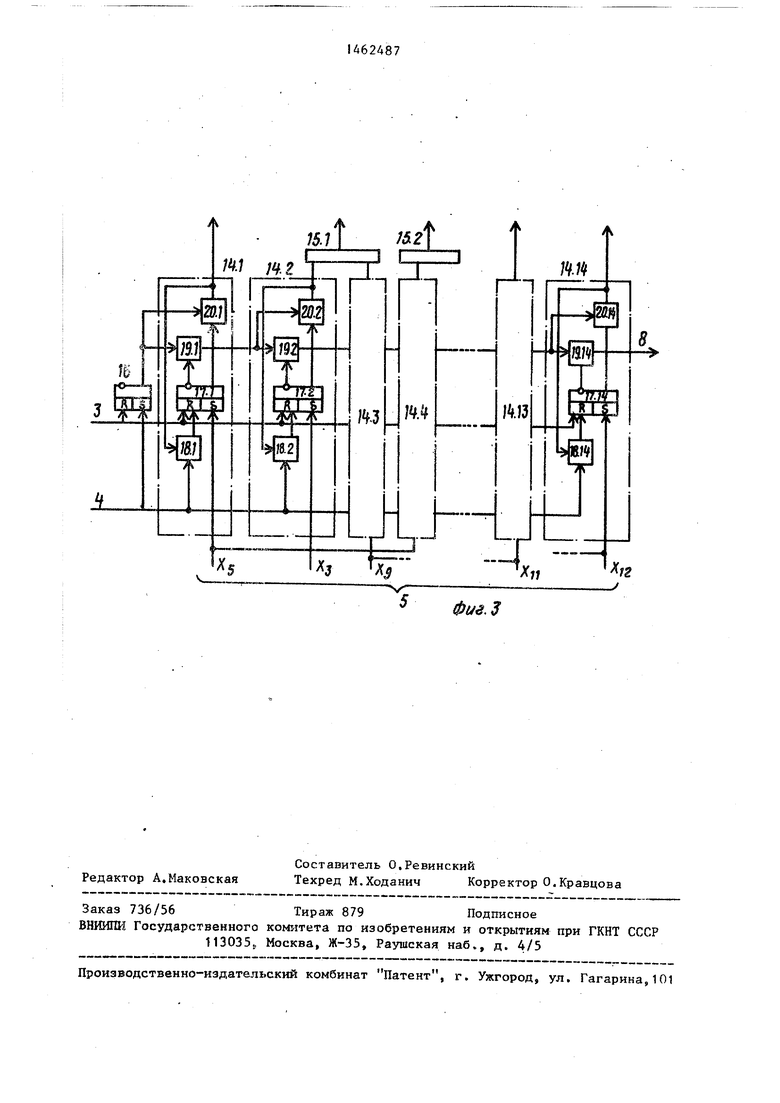

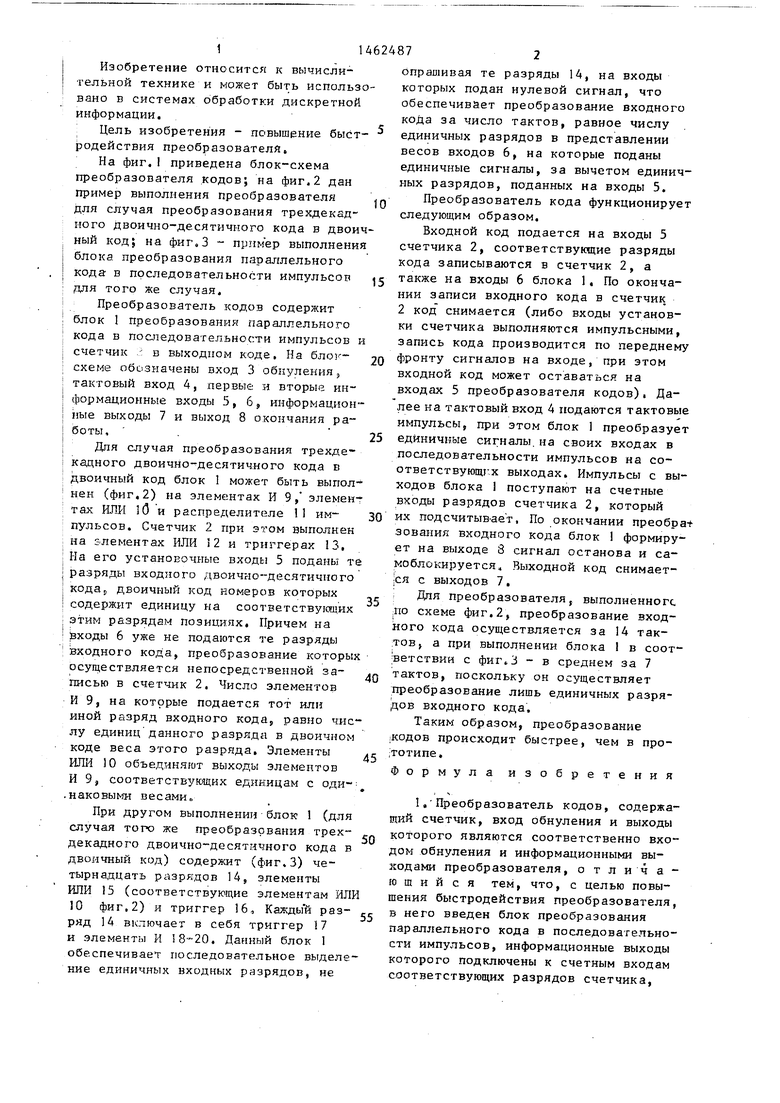

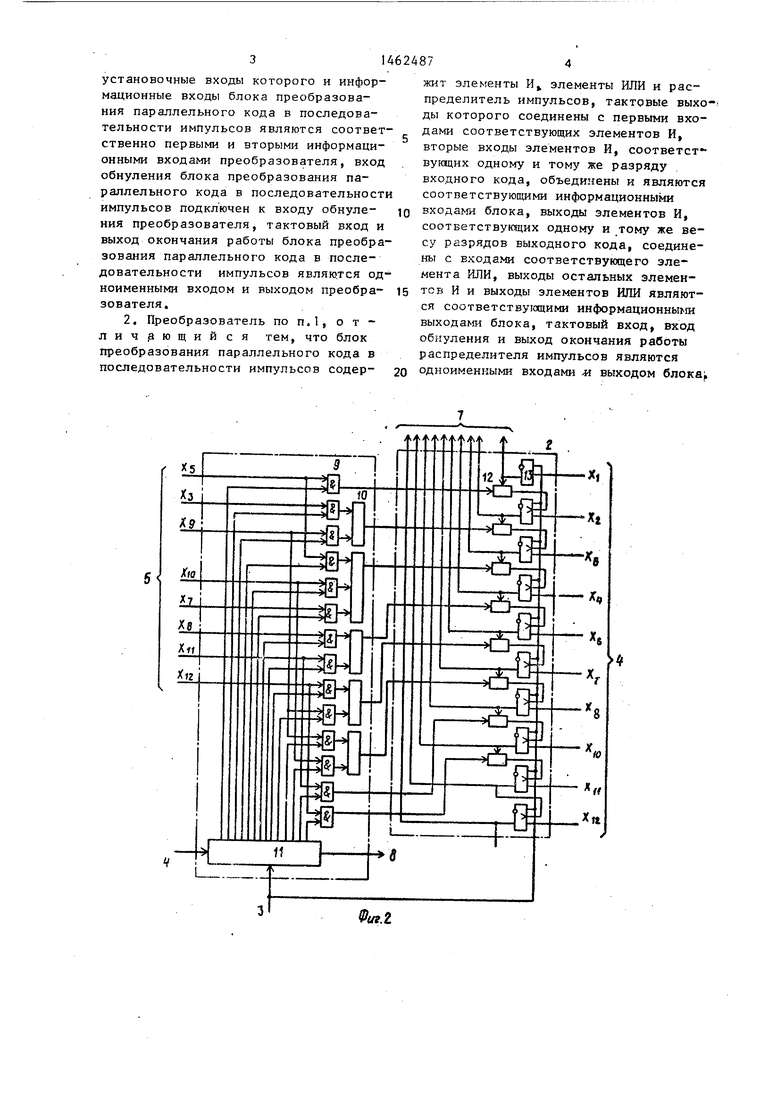

На фиг.1 приведена блок-схема преобразователя кодов; на фиг.2 дан пример выполнения преобразователя для случая преобразования трехдекад- ного двоично-десятичного кода в двоич- ный код; на фиг.З - пример выполнения блока преобразования параллельного кода в последовательности импульсов для того же случая.

Преобразователь кодов содержит блок 1 преобразования параллельного кода в последовательности импульсов и счетчик .: в выходном коде. На блок- jQ схеме обозначены вход 3 обнуления, тактовый вход 4, первые и вторые информационные входы 5, 6, информационные выходы 7 и выход 8 окончания работы, .25

Для случая преобразования трехде- кадного двоично-десятичного кода в I двоичный код блок 1 может быть выпол- : нен (фиг. 2) на элементах И 9 , элемен- : тах ИЛИ 10 и распределителе 1 им- зо

пульсов. Счетчик 2 при этом выполнен ; на глементах ИЛИ 12 и триггерах 13. j На его установочные входы 5 поданы те разряды входного двоично-десятичного I кодвр двоичный код номеров которых I содержит единицу на соответствуктих I этим разрядам позициях. Причем на I Ьходы 6 уже не подаются те разряды входного кода, преобразование которых осуществляется непосредственной записью в счетчик 2. Число элементов И 9, на которые подается тот или иной разряд входного кода равно числу единиц данного разряда в двоичном коде веса этого разряда. Элементы ИЛИ 0 обьеднняют выходы элементов И 9, соответствующих единицам с оди- .каковыми весами,,

При другом выполнении блок 1 (для случая того же преобразования трех- декадного двоично-десятичного кода в двоичный код) содержит (фиг.З) четырнадцать разрядов 14, элементы ИЛИ 15 (соответствующие элементам ИЛИ 10

ряд 14 включает в себя триггер 17 и элементы И 8-20. Данный блок 1 обеспечивает последовательное выделение единичных входных разрядов, не

14624872

опрашивая те разряды 14, на вход которых подан нулевой сигнал, ч обеспечивает преобразование вход кода за число тактов, равное чи единичных разрядов в представлен весов входов 6, на которые подан единичные сигналы, за вычетом ед ных разрядов, поданных на входы

Преобразователь кода функцион следующим образом.

Входной код подается на входы счетчика 2, соответствукщие разр кода записываются в счетчик 2, а также на входы 6 блока 1. По око нии записи входного кода в счетч 2 код снимается (либо входы уста ки счетчика выполняются импульсн запись кода производится по пере фронту сигналов на входе, при эт входной код может оставаться на входах 5 преобразователя кодов). лее на тактовый вход 4 подаются так импульсы, при этом блок 1 преобр единичные сигналы.на своих входа последовательности импульсов на ответствующгх выходах. Импульсы ходов блока 1 поступают на счетн входы разрядов счетчика 2, котор их подсчитыв.ает. По окончании пр зования входного кода блок фор ет на выходе 8 сигнал останова и коблокируется. Выходной код сним |ся с выходов 7.

: Дпя преобразователя, выполненн jHo схеме фиг.2, преобразование вх ного кода осуществляется за 14 та .тов, а при выполнении блока 1 в с ветствии с фиг.З - в среднем за 7 тактов, поскольку он осуществляет преобразование лишь единичных раз дов входного кода.

Таким образом, преобразование )Кодов происходит быстрее, чем в п

;ТОТИПе.

Формула изобретен

35

45

50

, тч,.. ио11.тридеистБия преооразоват

фиг.2) и триггер 16, Каждый раз-в него введен блок преобразования

lu Пи-ттиасп- о /-.пКгг ,„.,„„IT - - - - ocuin/I

1 ,преобразователь кодов, соде щий счетчик, вход обнуления и вых которого являются соответственно дом обнуления и информационными в кодами преобразователя, отлич ющийся тем, что, с целью по шения быстродействия преобразоват

параллельного кода в последовател сти импульсов, информационные вых которого подключены к счетным вход соответствующих разрядов счетчика

10

15

-

jQ 25

зо

4624872

опрашивая те разряды 14, на входы которых подан нулевой сигнал, что обеспечивает преобразование входного кода за число тактов, равное числу единичных разрядов в представлении весов входов 6, на которые поданы единичные сигналы, за вычетом единичных разрядов, поданных на входы 5.

Преобразователь кода функционирует следующим образом.

Входной код подается на входы 5 счетчика 2, соответствукщие разряды кода записываются в счетчик 2, а также на входы 6 блока 1. По окончании записи входного кода в счетчик. 2 код снимается (либо входы устано в- ки счетчика выполняются импульсными, запись кода производится по переднему фронту сигналов на входе, при этом входной код может оставаться на входах 5 преобразователя кодов). Далее на тактовый вход 4 подаются тактовые импульсы, при этом блок 1 преобразует единичные сигналы.на своих входах в последовательности импульсов на со- ответствующгх выходах. Импульсы с выходов блока 1 поступают на счетные входы разрядов счетчика 2, который их подсчитыв.ает. По окончании преобра зования входного кода блок формирует на выходе 8 сигнал останова и са- коблокируется. Выходной код снимает- |ся с выходов 7.

: Дпя преобразователя, выполненногс jHo схеме фиг.2, преобразование входного кода осуществляется за 14 так- .тов, а при выполнении блока 1 в соответствии с фиг.З - в среднем за 7 тактов, поскольку он осуществляет преобразование лишь единичных разрядов входного кода.

Таким образом, преобразование )Кодов происходит быстрее, чем в про;ТОТИПе.

Формула изобретения

35

5

0

. ио11.тридеистБия преооразоват

в него введен блок преобразования

1 ,преобразователь кодов, содержащий счетчик, вход обнуления и выходы которого являются соответственно входом обнуления и информационными вы- кодами преобразователя, отличающийся тем, что, с целью повышения быстродействия преобразователя.

в него введен блок преобразования

- - ocuin/I

параллельного кода в последовательности импульсов, информационные выходы которого подключены к счетным входам соответствующих разрядов счетчика.

установочные входы которого и информационные входы блока преобразования параллельного кода в последовательности импульсов являются соответственно первыми и вторыми информационными входами преобразователя, вход обнуления блока преобразования параллельного кода в последовательности импульсов подключен к входу обнуления преобразователя, тактовый вход и выход окончания работы блока преобразования параллельного кода в последовательности импульсов являются одноименными входом и выходом преобразователя.

BxoAaNM блока, выходы элементов И, соответствукщих одному и тому же весу разрядов выходного кода, соединены с входами соответствующего элемента ИЛИ, выходы остальных элементов И и выходы элементов ИЛИ являются соответствующими инфopмaциoнны iи выходами блока, тактовый вход, вход обнуления и выход окончания работы распределителя импульсов являются

одноименными входами « выходом блокад

Фиг.г

Фи.З

| Приборы и техника эксперимента, 1978, № 5, с.100-101 | |||

| Преобразователь кодов | 1986 |

|

SU1361723A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-02-28—Публикация

1987-01-23—Подача