1

Изобретение относится к импульсной технике и может быть использовано в устройствах измерения временных параметров импульсных последовательностей, а также в устройствах синхронизации.

Цель изобретения - расширение функциональных возможностей путем обеспечения возможности селекции пе риодической последовательности импульсов по периоду следования и фазе из потока входных сигналов с периодами, равными или кратными селектируемой последовательности.

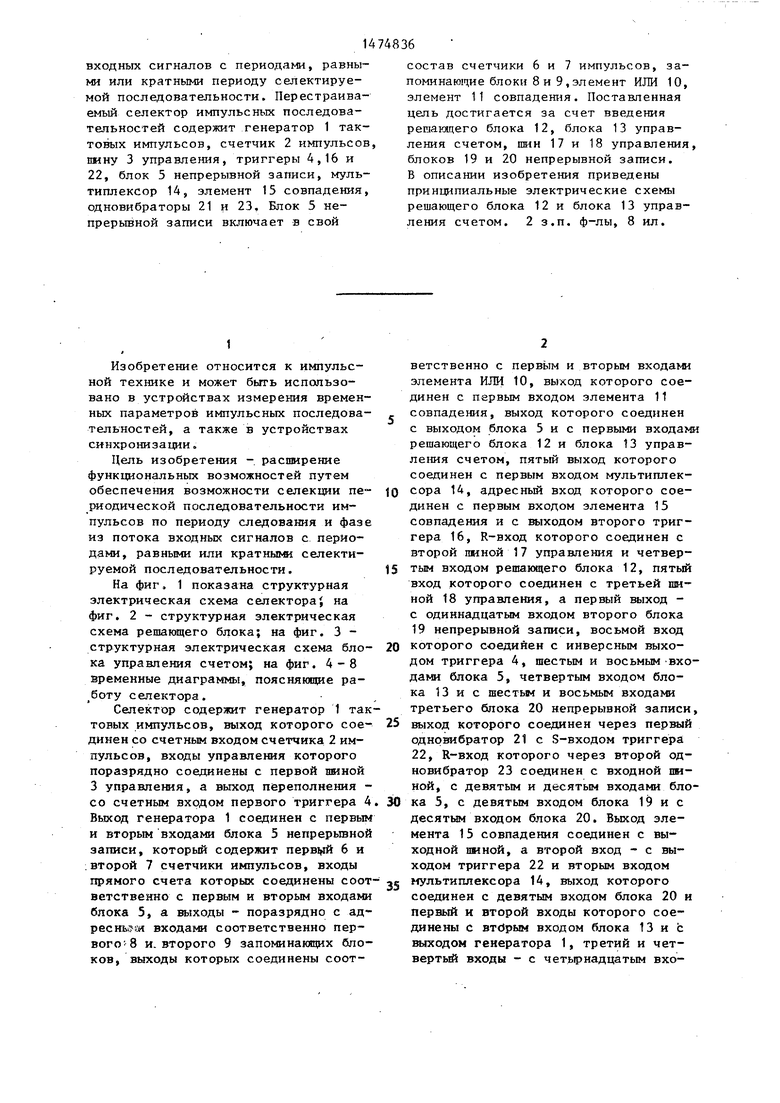

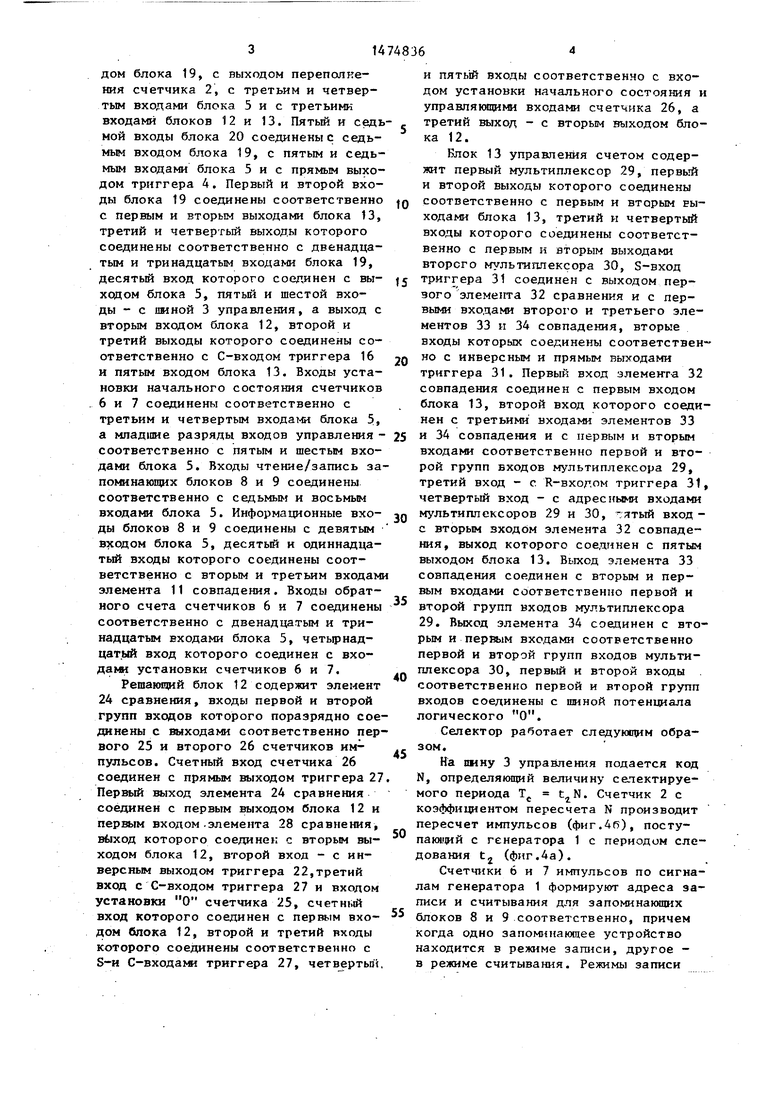

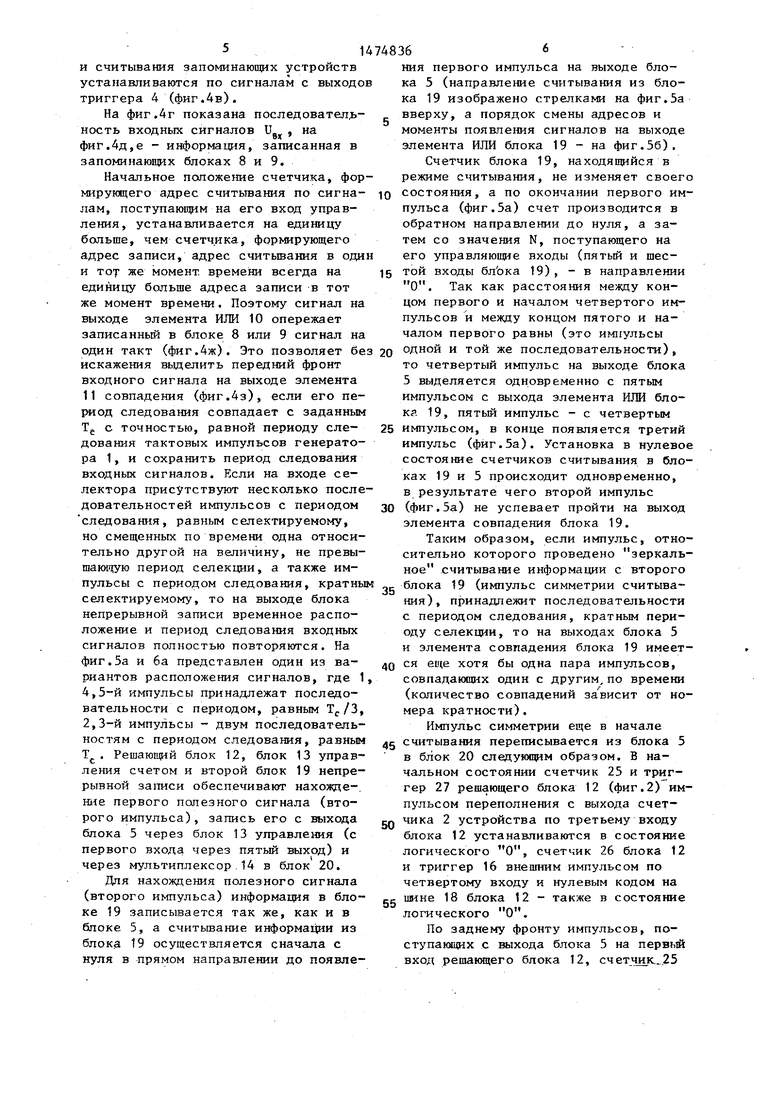

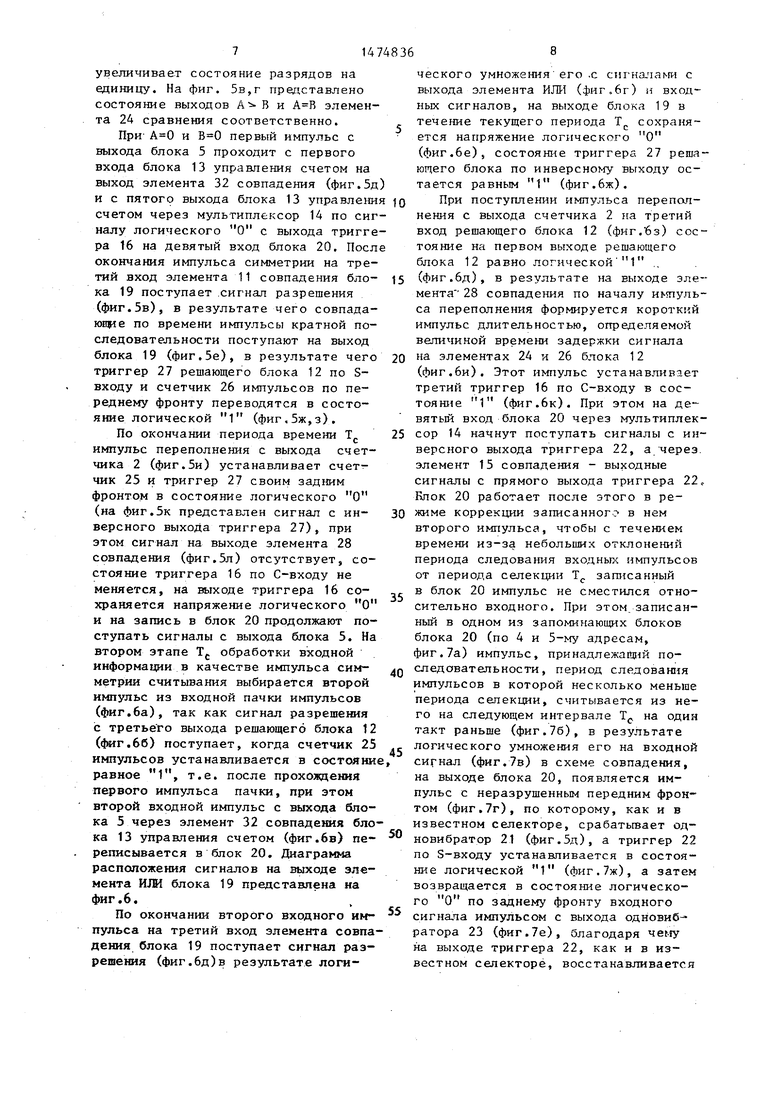

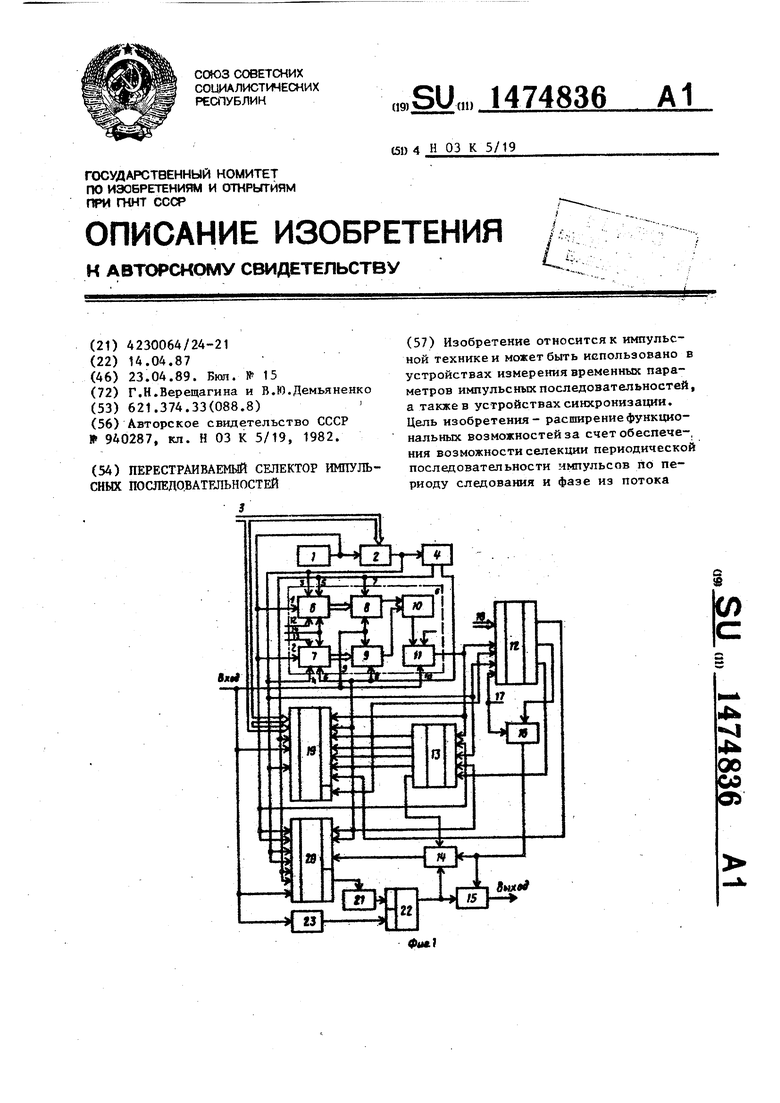

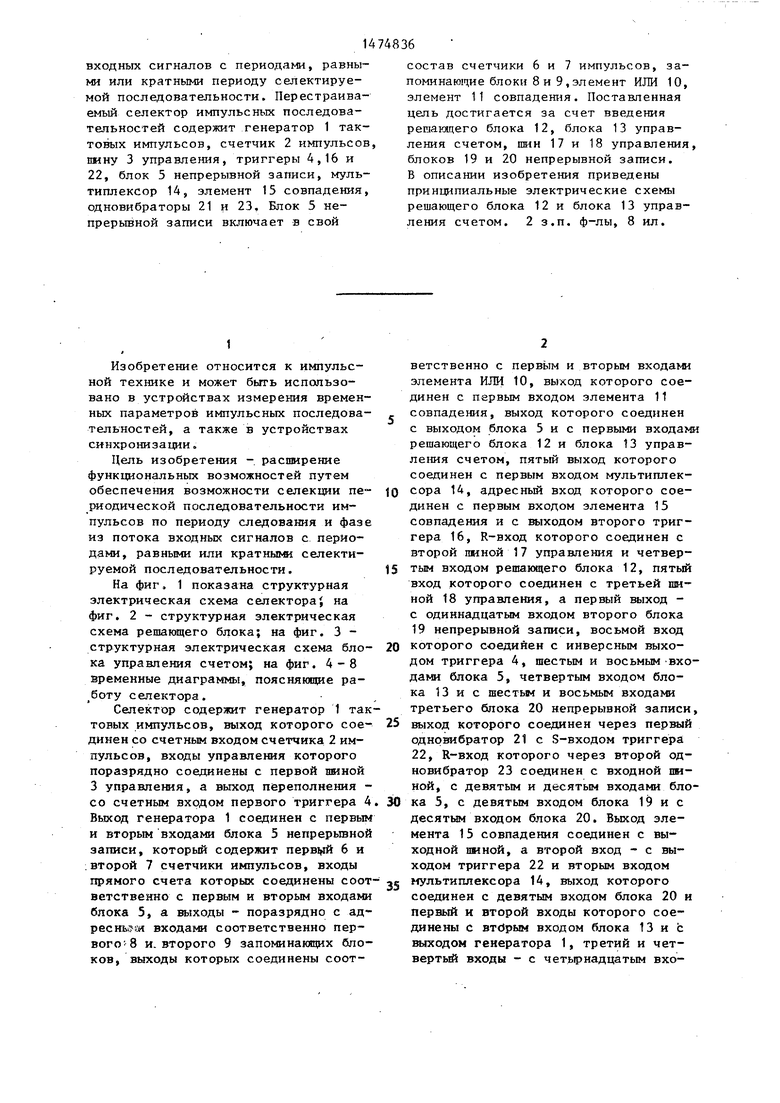

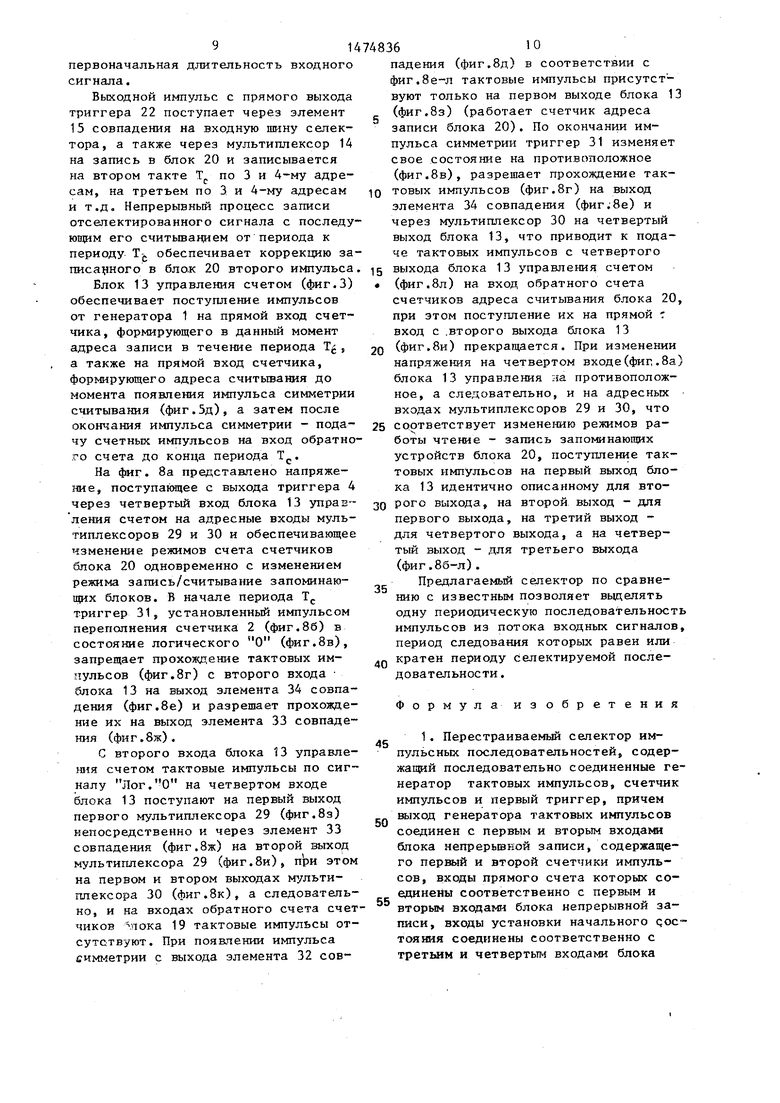

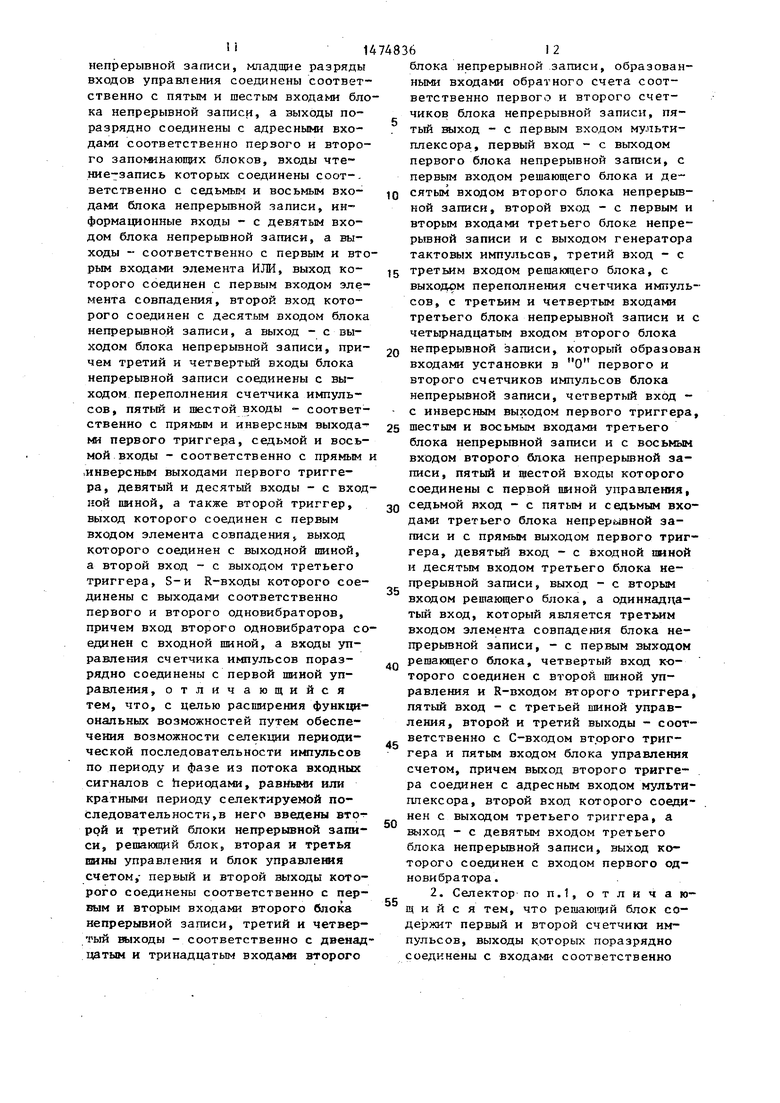

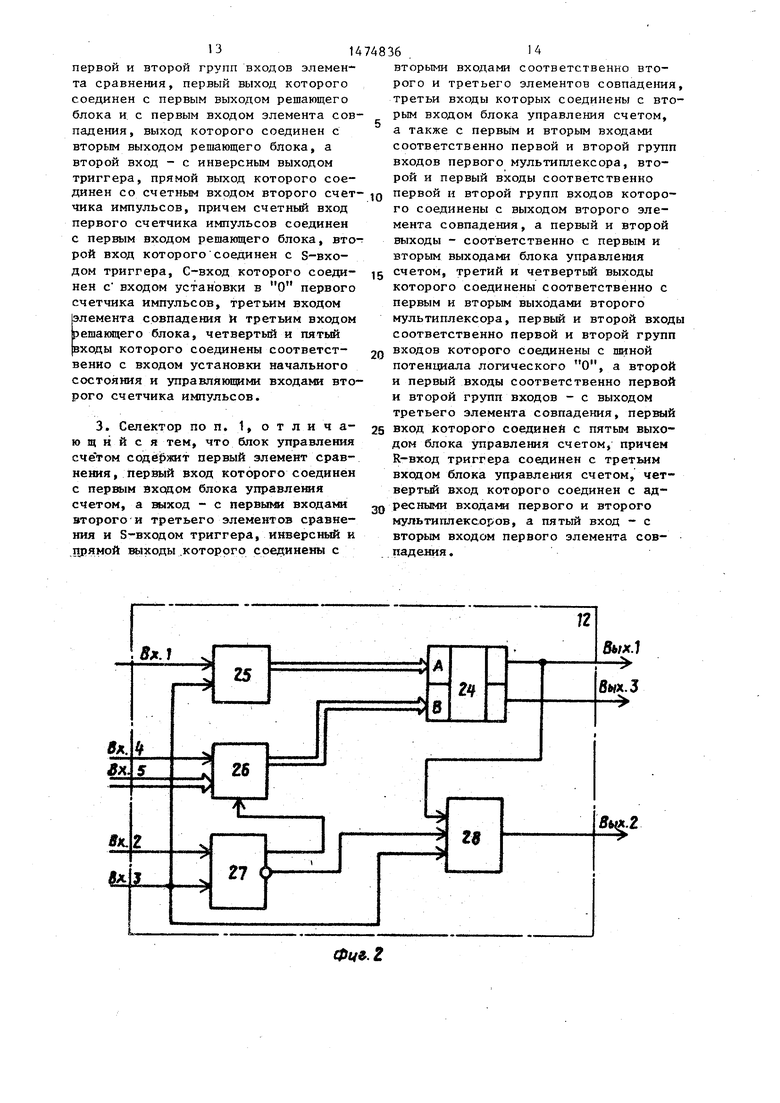

На фиг 1 показана структурная электрическая схема селектора, на фиг. 2 - структурная электрическая схема решающего блока; на фиг. 3 - структурная электрическая схема блока управления счетом; на фиг. 4-8 временные диаграммы, поясняющие ра- оту селектора.

Селектор содержит генератор 1 тактовых импульсов, выход которого соединен со счетным входом счетчика 2 импульсов, входы управления которого поразрядно соединены с первой шиной 3 управления, а выход переполнения

со счетным входом первого триггера 4 Выход генератора 1 соединен с первым и вторым входами блока 5 непрерывной записи, который содержит первый 6 и второй 7 счетчики импульсов, входы прямого счета которых соединены соот- ветственно с первым и вторым входами блока 5, а выходы - поразрядно с адресном входами соответственно первого 8 и. второго 9 запоминающих блоков, выходы которых соединены соот

0

5

0

с

ветственно с первым и вторым входами элемента ИЛИ 10, выход которого соединен с первым входом элемента 11 совпадения, выход которого соединен с выходом блока 5 и с первыми входами решающего блока 12 и блока 13 управления счетом, пятый выход которого соединен с первым входом мультиплексора 14, адресный вход которого соединен с первым входом элемента 15 совпадения и с выходом второго триггера 16, R-вход которого соединен с второй шиной 17 управления и четвертым входом решающего блока 12, пятый вход которого соединен с третьей шиной 18 управления, а первый выход - с одиннадцатым входом второго блока 19 непрерывной записи, восьмой вход которого соединен с инверсным выходом триггера 4, шестым и восьмым входами блока 5, четвертым входом блока 13 и с шестым и восьмым входами третьего блока 20 непрерывной записи, выход которого соединен через первый одновибратор 21 с S-входом триггера 22, R-вход которого через второй одновибратор 23 соединен с входной пн- ной, с девятым и десятым входами блока 5, с девятым входом блока 19 и с десятым входом блока 20. Выход элемента 15 совпадения соединен с выходной виной, а второй вход - с выходом триггера 22 и вторым входом мультиплексора 14, выход которого соединен с девятым входом блока 20 и первый и второй входы которого соединены с вторым входом блока 13 и с выходом генератора 1, третий и четвертый входы - с четырнадцатым входом блока 19, с выходом переполке- ния счетчика 2, с третьим и четвертым входами блока 5 и с третьими входами блоков 12 и 13. Пятый и седьмой входы блока 20 соединены с седьмым входом блока 19, с пятым и седьмым входами блока 5 и с прямым выходом триггера 4. Первый и второй входы блока 19 соединены соответственно с первым и вторым выходами блока 13, третий и четвертый выходы которого соединены соответственно с двенадцатым и тринадцатым входами блока 19, десятый вход которого соединен с выходом блока 5, пятый и шестой входы - с лнной 3 управления, а выход с вторым входом блока 12, второй и третий выходы которого соединены соответственно с С-входом триггера 16 и пятым входом блока 13. Входы установки начального состояния счетчиков 6 и 7 соединены соответственно с третьим и четвертым входами блока 5, а младшие разряды входов управления - соответственно с пятым и шестым входами блока 5. Входы чтение/запись запоминающих блоков 8 и 9 соединены соответственно с седьмым и восьмым входами блока 5. Информационные входы блоков 8 и 9 соединены с девятым входом блока 5, десятый и одиннадцатый входы которого соединены соответственно с вторым и третьим входами элемента 11 совпадения. Входы обратного счета счетчиков 6 и 7 соединены соответственно с двенадцатым и тринадцатым входами блока 5, четырнадцатый вход которого соединен с входами установки счетчиков 6 и 7.

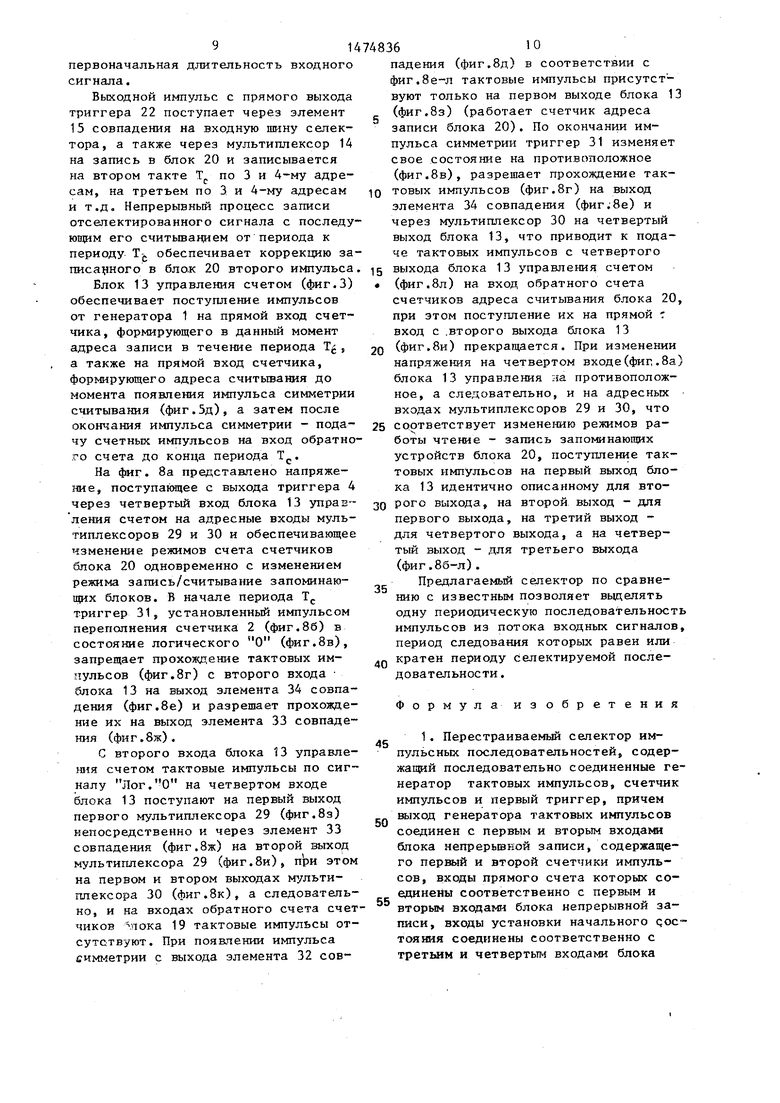

Решающий блок 12 содержит элемент 24 сравнения, входы первой и второй групп входов которого поразрядно соединены с выходами соответственно первого 25 и второго 26 счетчиков импульсов. Счетный вход счетчика 26 соединен с прямым выходом триггера 27 Первый выход элемента 24 сравнения соединен с первым выходом блока 12 и первым входом-элемента 28 сравнения, выход которого соединен с вторым выходом блока 12, второй вход - с инверсным выходом триггера 22,третий вход с С-входом триггера 27 и входом установки О счетчика 25, счетный вход которого соединен с первым входом блока 12, второй и третий входы которого соединены соответственно с S-и С-входами триггера 27, четвертый

0

5

0

5

0

5

0

5

0

5

и пятый входы соответственно с входом установки начального состояния и управляющими входами счетчика 26, а третий выход - с вторым выходом блока 12.

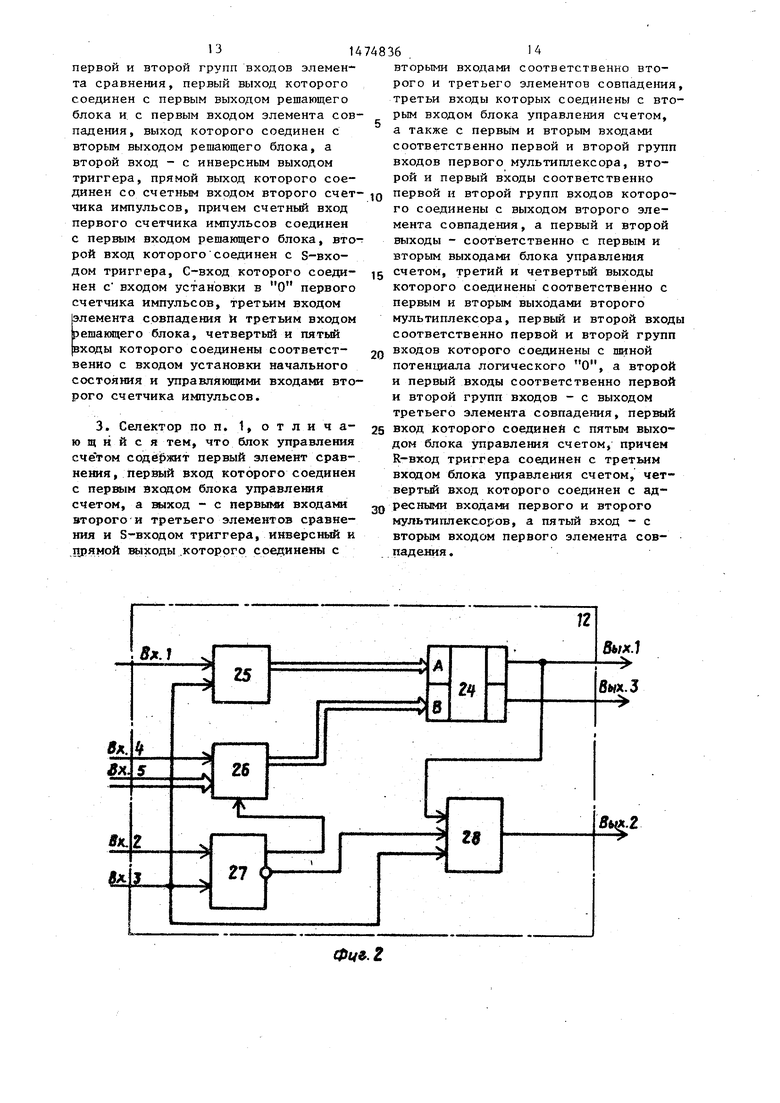

Блок 13 управления счетом содержит первый мультиплексор 29, первый и второй выходы которого соединены соответственно с первым и вторым выходами блока 13, третий и четвертый входы которого соединены соответственно с первым и вторым выходами второго мультиплексора 30, S-вход триггера 31 соединен с выходом пер- зого элемента 32 сравнения и с первыми входами второго и третьего элементов 33 и 34 совпадения, вторые входы которых соединены соответственно с инверсным и прямым выходами триггера 31. Первый вход элемента 32 совпадения соединен с первым входом блока 13, второй вход которого соединен с третьими входами элементов 33 и 34 совпадения и с первым и вторым входами соответственно первой и второй групп входов мультиплексора 29, третий вход - с R-входом триггера 31, четвертый вход - с адресными входами мультиплексоров 29 и 30, -ятый вход - с вторым входом элемента 32 совпадения, выход которого соединен с пятым выходом блока 13. Выход элемента 33 совпадения соединен с вторым и первым входами соответственно первой и второй групп входов мультиплексора 29. Выход элемента 34 соединен с вторым и первым входами соответственно первой и второй групп входов мультиплексора 30, первый и второй входы соответственно первой и второй групп входов соединены с шиной потенциала логического О.

Селектор работает следующим образом.

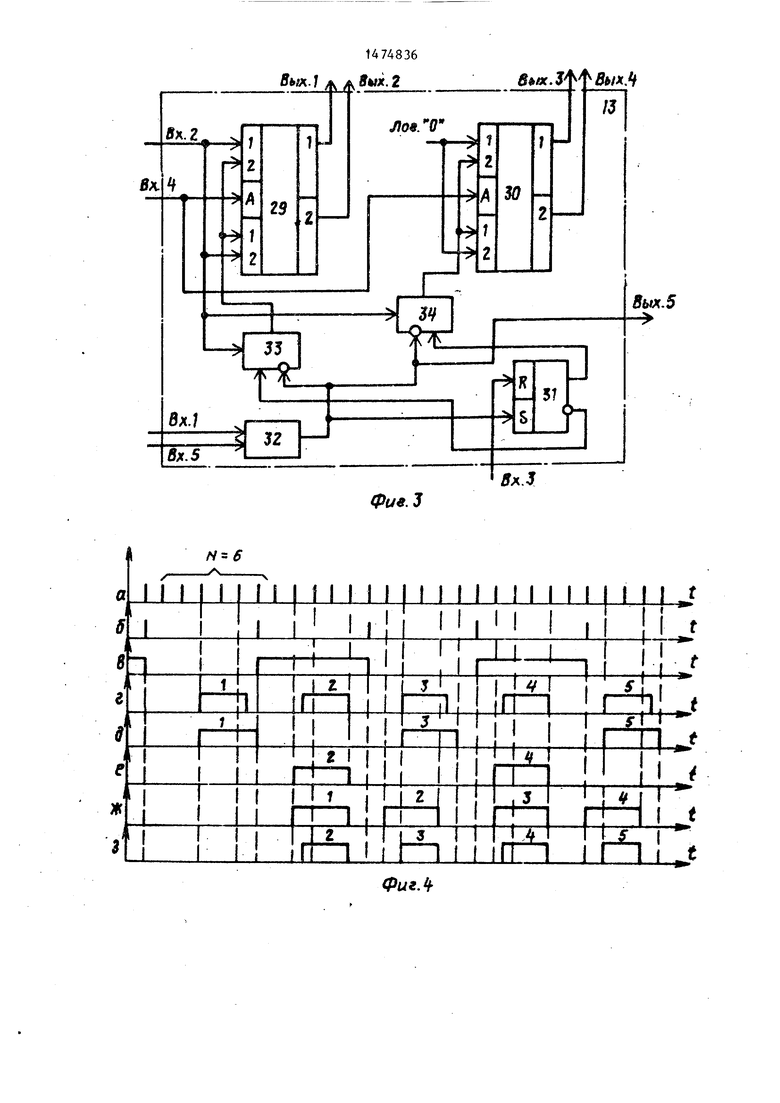

На шину 3 управления подается код N, определяющий величину селектируемого периода Тс ttN. Счетчик 2 с коэффициентом пересчета N производит пересчет импульсов (фиг.45), поступающий с генератора 1 с периодом следования t2 (фиг.4а).

Счетчики 6 н 7 импульсов по сигналам генератора 1 формируют адреса записи и считывания для запоминающих блоков 8 и 9 соответственно, причем когда одно запоминающее устройство находится в режиме записи, другое - в режиме считывания. Режимы записи

и считывания запоминающих устройств устанавливаются по сигналам с выходов триггера 4 (фиг.4в).

На фиг.4г показана последователь- ность входных сигналов V , на фиг.4д,е - информация, записанная в запоминающих блоках 8 и 9.

Начальное положение счетчика, формирующего адрес считывания по сигналам, поступающим на его вход управления, устанавливается на единицу больше, чем счетчика, формирующего адрес записи, адрес считывания в один и тот же момент времени всегда на единицу больше адреса записи в тот же момент времени. Поэтому сигнал на выходе элемента ИЛИ 10 опережает записанный в блоке 8 или 9 сигнал на

ния первого импульса на выходе блока 5 (направление считывания из блока 19 изображено стрелками на фиг.За вверху, а порядок смены адресов и моменты появления сигналов на выходе элемента ИЛИ блока 19 - на фиг.56). Счетчик блока 19, находящийся в режиме считывания, не изменяет своего

состояния, а по окончании первого импульса (фиг.За) счет производится в обратном направлении до нуля, а затем со значения N, поступающего на его управляющие входы (пятый и шес5 той входы бл ока 19) , - в направлении О. Так как расстояния между концом первого и началом четвертого импульсов и между концом пятого и началом первого равны (это импульсы

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2300112C2 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Многоканальный преобразователь интервалов времени в код | 1985 |

|

SU1273873A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для ввода информации | 1989 |

|

SU1649529A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах измерения временных параметров импульсных последовательностей, а также в устройствах синхронизации. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности селекции периодической последовательности импульсов по периоду следования и фазе из потока входных сигналов с периодами, равными или кратными периоду селектируемой последовательности. Перестраиваемый селектор импульсных последовательностей содержит генератор 1 тактовых импульсов, счетчик 2 импульсов, шину 3 управления, триггеры 4, 16,22, блок 5 непрерывной записи, мультиплексор 14, элемент 15 совпадения, одновибраторы 21 и 23. Блок 5 непрерывной записи включает в свой состав счетчики 6 и 7 импульсов, запоминающие блоки 8 и 9, элемент ИЛИ 10, элемент 11 совпадения. Поставленная цель достигается за счет введения решающего блока 12, блока 13 управления счетом, шин 17 и 18 управления, блоков 19 и 20 непрерывной записи. В описании изобретения приведены принципиальные электрические схемы решающего блока 12 и блока 13 управления счетом. 2 з.п. ф-лы. 8 ил.

один такт (фиг.4ж). Это позволяет без 20 °лной и той же последовательности),

искажения выделить передний фронт входного сигнала на выходе элемента 11 совпадения (фиг.4з), если его период следования совпадает с заданным Те с точностью, равной периоду следования тактовых импульсов генератора 1 , и сохранить период следования входных сигналов. Если на входе селектора присутствуют несколько последовательностей импульсов с периодом следования, равным селектируемому, но смещенных по времени одна относительно другой на величину, не превышающую период селекции, а также имто четвертый импульс на выходе блока 5 выделяется одновременно с пятым импульсом с выхода элемента ИЛИ блока 19, пятый импульс - с четвертым

25 импульсом, в конце появляется третий импульс (фиг.За). Установка в нулево состояние счетчиков считывания в бло ках 19 и 5 происходит одновременно, в результате чего второй импульс

30 (фиг.За) не успевает пройти на выход элемента совпадения блока 19.

Таким образом, если импульс, отно сительно которого проведено зеркаль ное считывание информации с второго

пульсы с периодом следования, кратным 3g блока 19 (импульс симметрии считываселектируемому, то на выходе блока непрерывной записи временное расположение и период следования входных сигналов полностью повторяются. На фиг.За и 6а представлен один из вариантов расположения сигналов, где 1, 4,5-й импульсы принадлежат последовательности с периодом, равным Тс/3, 2,3-й импульсы - двум последовательния), принадлежит последовательности с периодом следования, кратным периоду селекции, то на выходах блока 5 и элемента совпадения блока 19 имеет- 40 ся еще хотя бы одна пара импульсов, совпадающих один с другим,по времени (количество совпадений зависит от номера кратности).

Импульс симметрии еще в начале

50

ностям с периодом следования, равным считывания переписывается из блока 5 Тс. Решающий блок 12, блок 13 управления счетом и второй блок 19 непрерывной записи обеспечивают нахождение первого полезного сигнала (второго импульса), запись его с выхода блока 5 через блок 13 управления (с первого входа через пятый выход) и через мультиплексор 14 в блок 20.

Для нахождения полезного сигнала (второго импульса) информация в блоке 19 записывается так же, как и в блоке 5, а считывание информации из блока 19 осуществляется сначала с нуля в прямом направлении до появле55

в блок 20 следующим образом. В начальном состоянии счетчик 25 и триггер 27 решающего блока 12 (фиг.2) импульсом переполнения с выхода счетчика 2 устройства по третьему входу блока 12 устанавливаются в состояние логического О, счетчик 26 блока 12 и триггер 16 внешним импульсом по четвертому входу и нулевым кодом на шине 18 блока 12 - также в состояние логического О.

По заднему фронту импульсов, поступающих с выхода блока 5 на первый вход решающего блока 12, счетчик..25

то четвертый импульс на выходе блока 5 выделяется одновременно с пятым импульсом с выхода элемента ИЛИ блока 19, пятый импульс - с четвертым

импульсом, в конце появляется третий импульс (фиг.За). Установка в нулевое состояние счетчиков считывания в блоках 19 и 5 происходит одновременно, в результате чего второй импульс

(фиг.За) не успевает пройти на выход элемента совпадения блока 19.

Таким образом, если импульс, относительно которого проведено зеркальное считывание информации с второго

блока 19 (импульс симметрии считывания), принадлежит последовательности с периодом следования, кратным периоду селекции, то на выходах блока 5 и элемента совпадения блока 19 имеет- ся еще хотя бы одна пара импульсов, совпадающих один с другим,по времени (количество совпадений зависит от номера кратности).

Импульс симметрии еще в начале

считывания переписывается из блока 5

в блок 20 следующим образом. В начальном состоянии счетчик 25 и триггер 27 решающего блока 12 (фиг.2) импульсом переполнения с выхода счетчика 2 устройства по третьему входу блока 12 устанавливаются в состояние логического О, счетчик 26 блока 12 и триггер 16 внешним импульсом по четвертому входу и нулевым кодом на шине 18 блока 12 - также в состояние логического О.

По заднему фронту импульсов, поступающих с выхода блока 5 на первый вход решающего блока 12, счетчик..25

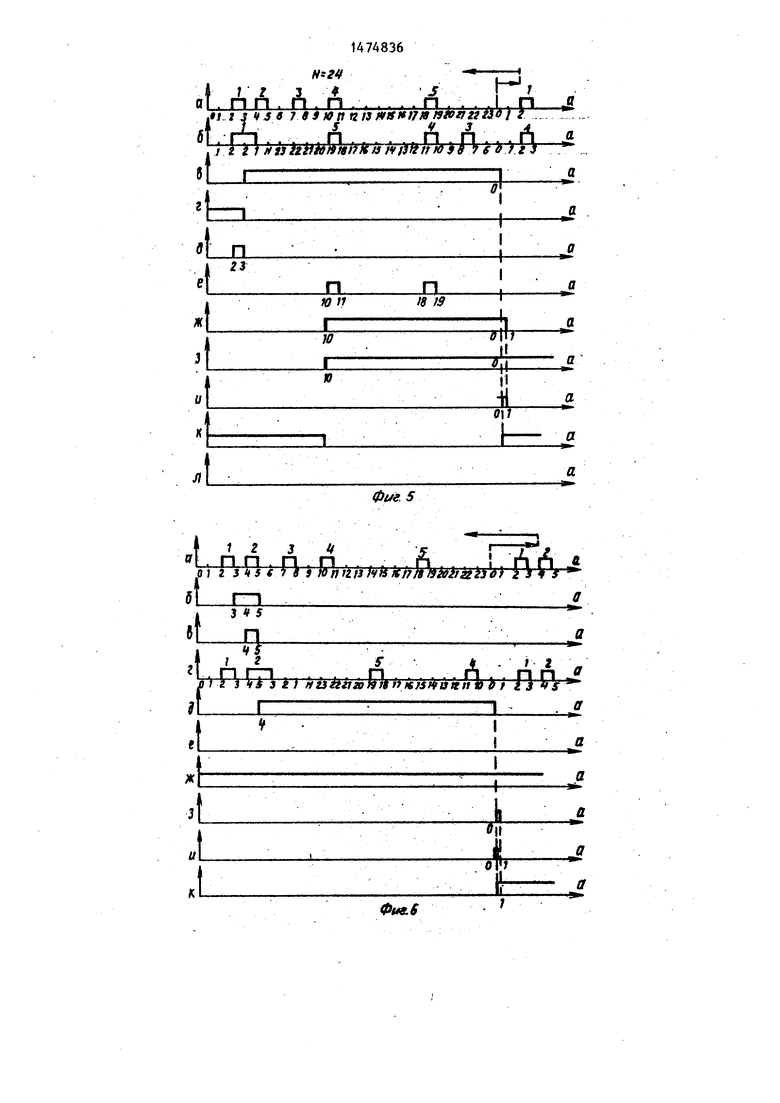

увеличивает состояние разрядов на единицу. На фиг. 5в,г представлено состояние выходов В и элемента 24 сравнения соответственно.

При и первый импульс с выхода блока 5 проходит с первого входа блока 13 управления счетом на выход элемента 32 совпадения (фиг.Зд и с пятого выхода блока 13 управлени счетом через мультиплексор 14 по сигналу логического О с выхода триггера 16 на девятый вход блока 20. Посл окончания импульса симметрии на третий вход элемента 11 совпадения бло- ка 19 поступает сигнал разрешения (фиг.Зв), в результате чего совпадающие по времени импульсы кратной последовательности поступают на выход блока 19 (фиг.Зе), в результате чего триггер 27 решающего блока 12 по S- входу и счетчик 26 импульсов по переднему фронту переводятся в состояние логической 1 (фиг«5ж,з).

По окончании периода времени Тс импульс переполнения с выхода счетчика 2 (фиг.5и) устанавливает счетчик 25 и триггер 27 своим задним фронтом в состояние логического О (на фиг.Зк представлен сигнал с ин- версного выхода триггера 27), при этом сигнал на выходе элемента 28 совпадения (фиг.5л) отсутствует, состояние триггера 16 по С-входу не меняется, на выходе триггера 16 со- храняется напряжение логического О и на запись в блок 20 продолжают поступать сигналы с выхода блока 5. На втором этапе Тс обработки входной информации в качестве импульса сим- метрии считывания выбирается второй импульс из входной пачки импульсов (фиг.ба), так как сигнал разрешения с третьего выхода решающего блока 12 (фиг.66) поступает, когда счетчик 25 импульсов устанавливается в состояни равное 1, т.е. после прохождения первого импульса пачки, при этом второй входной импульс с выхода блока 5 через элемент 32 совпадения блока 13 управления счетом (фиг.бв) пе- реписывается в блок 20. Диаграмма расположения сигналов на выходе элемента ИЛИ блока 19 представлена на фиг.6.

По окончании второго входного им- пульса на третий вход элемента совпадения блока 19 поступает сигнал разрешения (фиг.бд)в результате логического умножения его .с сигналами с выхода элемента ИЛИ (фиг.бг) и входных сигналов, на выходе блока 19 в течение текущего периода Тс сохраняется напряжение логического О (фиг.бе)5 состояние триггера 27 решающего блока по инверсному выходу остается равным 1 (фиг.бж).

При поступлении импульса переполнения с выхода счетчика 2 на третий вход решающего блока 12 (фиг.бз) состояние на первом выходе решающего блока 12 равно логической 1 (фиг.бд), в результате на выходе элемента 28 совпадения по началу импупь са переполнения формируется короткий импульс длительностью, определяемой величиной времени задержки сигнала на элементах 24 и 26 блока 12 (фиг.би). Этот импульс устанавливает третий триггер 16 по С-входу в состояние 1 (фиг.бк). При этом на девятый вход блока 20 через мультиплексор 14 начнут поступать сигналы с инверсного выхода триггера 22, а через элемент 15 совпадения - выходные сигналы с прямого выхода триггера 22 Клок 20 работает после этого в режиме коррекции записанного в нем второго импульса, чтобы с течением времени из-за небольших отклонений периода следования входных импульсов от периода селекции Тс записанный в блок 20 импульс не сместился относительно входного. При этом записанный в одном из запоминающих блоков блока 20 (по 4 и 5-му адресам, фиг.7а) импульс, принадлежащий последовательности, период следования импульсов в которой несколько меньше периода селекции, считывается из него на следующем интервале Тс на один такт раньше (фиг.7б), в результате логического умножения его на входной сигнал (фиг.7в) в схеме совпадения, на выходе блока 20, появляется импульс с неразрушенным передним фронтом (фиг.7г), по которому, как и в известном селекторе, срабатывает од- новибратор 21 (фиг.5д), а триггер 22 по S-входу устанавливается в состояние логической 1 (фиг.7ж), а затем возвращается в состояние логического О по заднему фронту входного сигнала импульсом с выхода одновиб- ратора 23 (фиг.7е), благодаря чему на выходе триггера 22, как и в известном селекторе, восстанавливается

первоначальная длительность входного сигнала.

Выходной импульс с прямого выхода триггера 22 поступает через элемент 15 совпадения на входную шину селектора, а также через мультиплексор 14 на запись в блок 20 и записывается на втором такте Тс по 3 и 4-му адресам, на третьем по 3 и 4-му адресам и т.д. Непрерывный процесс записи отселектированного сигнала с последующим его считыванием от периода к периоду Т-., обеспечивает коррекцию записанного в блок 20 второго импульса. 5 выхода блока 13 управления счетом

Блок 13 управления счетом (фиг.З) обеспечивает поступление импульсов от генератора 1 на прямой вход счет(фиг.8л) на вход обратного счета счетчиков адреса считывания блока при этом поступление их на прямой вход с второго выхода блока 13

t t

чика, формирующего в данный момент адреса записи в течение периода Т, а также на прямой вход счетчика, формирующего адреса считывания до момента появления импульса симметрии считывания (фиг.Зд), а затем после окончания импульса симметрии - подачу счетных импульсов на вход обратного счета до конца периода Тс.

На фиг. 8а представлено напряжение, поступающее с выхода триггера 4 через четвертый вход блока 13 управления счетом на адресные входы мультиплексоров 29 и 30 и обеспечивающее изменение режимов счета счетчиков блока 20 одновременно с изменением режима запись/считывание запоминающих блоков. В начале периода Тс триггер 31, установленный импульсом переполнения счетчика 2 (фиг.86) в состояние логического О (фиг.8в), запрещает прохождение тактовых импульсов (фиг.Зг) с второго входа блока 13 на выход элемента 34 совпадения (фиг.8е) и разрешает прохождение их на выход элемента 33 совпадения (фиг.8ж).

С второго входа блока 13 управления счетом тактовые импульсы по сигналу Лог.О на четвертом входе блока 13 поступают на первый выход первого мультиплексора 29 (фиг.8з) непосредственно и через элемент 33 совпадения (фиг.8ж) на второй выход мультиплексора 29 (фиг.8и), при этом на первом и втором выходах мультиплексора 30 (фиг.8к), а следовательно, и

чиков пока 19 тактовые импульсы отсутствуют. При появлении импульса симметрии с выхода элемента 32 сов(фиг.8л) на вход обратного счета счетчиков адреса считывания блока 20 при этом поступление их на прямой . вход с второго выхода блока 13

2Q (фиг.8и) прекращается. При изменении напряжения на четвертом входе(фиг.8а блока 13 управления па противоположное, а следовательно, и на адресных входах мультиплексоров 29 и 30, что

25 соответствует изменению режимов работы чтение - запись запоминающих устройств блока 20, поступление тактовых импульсов на первый выход блока 13 идентично описанному для второго выхода, на второй выход - для первого выхода, на третий выход - для четвертого выхода, а на четвертый выход - для третьего выхода (фиг.8б-л).

Предлагаемый селектор по сравнению с известным позволяет выделять одну периодическую последовательност импульсов из потока входных сигналов период следования которых равен или

40 кратен периоду селектируемой последовательности .

Формула изобретения

30

35

45

50

на входах обратного счета счет- вторым входами блока непрерывной записи, входы установки начального достояния соединены соответственно с третьим и четвертым входами блока

падения (фиг.вд) в соответствии с фиг. тактовые импульсы присутствуют только на первом выходе блока 13 (фиг.8з) (работает счетчик адреса записи блока 20). По окончании импульса симметрии триггер 31 изменяет свое состояние на противоположное (фиг.бв), разрешает прохождение тактовых импульсов (фиг.8г) на выход элемента 34 совпадения (фиг.8е) и через мультиплексор 30 на четвертый выход блока 13, что приводит к подаче тактовых импульсов с четвертого

(фиг.8л) на вход обратного счета счетчиков адреса считывания блока 20, при этом поступление их на прямой . вход с второго выхода блока 13

(фиг.8и) прекращается. При изменении напряжения на четвертом входе(фиг.8а) блока 13 управления па противоположное, а следовательно, и на адресных входах мультиплексоров 29 и 30, что

соответствует изменению режимов работы чтение - запись запоминающих устройств блока 20, поступление тактовых импульсов на первый выход блока 13 идентично описанному для второго выхода, на второй выход - для первого выхода, на третий выход - для четвертого выхода, а на четвертый выход - для третьего выхода (фиг.8б-л).

Предлагаемый селектор по сравнению с известным позволяет выделять одну периодическую последовательность импульсов из потока входных сигналов, период следования которых равен или

кратен периоду селектируемой последовательности .

Формула изобретения

писи, входы установки начального достояния соединены соответственно с третьим и четвертым входами блока

непрерывной записи, младшие разряды входов управления соединены соответственно с пятым и шестым входами блока непрерывной записи, а выходы поразрядно соединены с адресными входами соответственно первого и второго запоминающих блоков, входы чтение-запись которых соединены соот-. ветственно с седьмым и восьмым входами блока непрерывной записи, информационные входы - с девятым входом блока непрерывной записи, а выходы - соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с первым входом элемента совпадения, второй вход которого соединен с десятым входом блока непрерывной записи, а выход - с выходом блока непрерывной записи, причем третий и четвертый входы блока непрерывной записи соединены с выходом переполнения счетчика импульсов, пятый и шестой входы - соответственно с прямым и инверсным выходами первого триггера, седьмой и восьмой входы - соответственно с прямым .инверсным выходами первого триггера, девятый и десятый входы - с входной шиной, а также второй триггер, выход которого соединен с первым входом элемента совпаденияf выход которого соединен с выходной шиной, а второй вход - с выходом третьего триггера, S-и R-входы которого соединены с выходами соответственно первого и второго одновибраторов, причем вход второго одновибратора соединен с входной шиной, а входы управления счетчика импульсов поразрядно соединены с первой шиной управления, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности селекции периодической последовательности импульсов по периоду и фазе из потока входных сигналов с периодами, равными или кратными периоду селектируемой последовательности, в него введены второй и третий блоки непрерывной записи, решающий блок, вторая и третья шины управления и блок управления счетом,- первый и второй выходы которого соединены соответственно с первым и вторым входами второго блока непрерывной записи, третий и четвертый выходы - соответственно с двенадцатым и тринадцатым входами второго

блока непрерывной записи, образованными входами обратного счета соответственно первого и второго счетчиков блока непрерывной записи, пятый выход - с первым входом мультиплексора, первый вход - с выходом первого блока непрерывной записи, с первым входом решающего блока и де

сятым входом второго блока непрерывной записи, второй вход - с первым и вторым входами третьего блока непрерывной записи и с выходом генератора тактовых импульсов, третий вход - с

5 третьим входом решающего блока, с

выходом переполнения счетчика импульсов, с третьим и четвертым входами третьего блока непрерывной записи и с четырнадцатым входом второго блока

о непрерывной записи, который образован входами установки в О первого и второго счетчиков импульсов блока непрерывной записи, четвертый вход - - с инверсным выходом первого триггера,

5 шестым и восьмым входами третьего блока непрерывной записи и с восьмым входом второго блока непрерывной записи, пятый и шестой входы которого соединены с первой шиной управления,

о седьмой вход - с пятым и седьмым входами третьего блока непрерывной записи и с прямым выходом первого триггера, девятый вход - с входной шиной и десятым входом третьего блока непрерывной записи, выход - с вторым входом решающего блока, а одиннадцатый вход, который является третьим входом элемента совпадения блока непрерывной записи, - с первым выходом

„ решающего блока, четвертый вход которого соединен с второй шиной управления и R-входом второго триггера, пятый вход - с третьей шиной управления, второй и третий выходы - соответственно с С-входом второго триггера и пятым входом блока управления счетом, причем выход второго триггера соединен с адресным входом мультиплексора, второй вход которого соединен с выходом третьего триггера, а выход - с девятым входом третьего блока непрерывной записи, выход которого соединен с входом первого одновибратора.

5

5

0

5

первой и второй групп входов элемента сравнения, первый выход которого соединен с первым выходом решающего блока и с первым входом элемента совпадения, выход которого соединен с вторым выходом решающего блока, а второй вход - с инверсным выходом триггера, прямой выход которого соединен со счетным входом второго счет- 10 первой и второй групп входов которочика импульсов, причем счетный вход первого счетчика импульсов соединен с первым входом решающего блока, второй вход которого соединен с S-вхо- дом триггера, С-вход которого соединен с входом установки в О первого счетчика импульсов, третьим входом элемента совпадения и третьим входом решающего блока, четвертый и пятый входы которого соединены соответственно с входом установки начального состояния и управляющими входами второго счетчика импульсов.

го соединены с выходом второго элемента совпадения, а первый и второй выходы - соответственно с первым и вторым выходами блока управления

jg счетом, третий и четвертый выходы которого соединены соответственно с первым и вторым выходами второго мультиплексора, первый и второй входы соответственно первой и второй групп

2Q входов которого соединены с шиной потенциала логического О, а второй и первый входы соответственно первой и второй групп входов - с выходом третьего элемента совпадения, первый

25 вход которого соединен с пятым выходом блока управления счетом, причем R-вход триггера соединен с третьим входом блока управления счетом, четвертый вход которого соединен с ад2Q ресными входами первого и второго мультиплексоров, а пятый вход - с вторым входом первого элемента совпадения .

Фиг. Z

вторыми входами соответственно второго и третьего элементов совпадения, третьи входы которых соединены с вторым входом блока управления счетом, а также с первым и вторым входами соответственно первой и второй групп входов первого мультиплексора, второй и первый входы соответственно

го соединены с выходом второго элемента совпадения, а первый и второй выходы - соответственно с первым и вторым выходами блока управления

счетом, третий и четвертый выходы которого соединены соответственно с первым и вторым выходами второго мультиплексора, первый и второй входы соответственно первой и второй групп

входов которого соединены с шиной потенциала логического О, а второй и первый входы соответственно первой и второй групп входов - с выходом третьего элемента совпадения, первый

вход которого соединен с пятым выходом блока управления счетом, причем R-вход триггера соединен с третьим входом блока управления счетом, четвертый вход которого соединен с адресными входами первого и второго мультиплексоров, а пятый вход - с вторым входом первого элемента совпадения .

Вых.1

AJS.

ffx.2

f-

7

HW

A

23

J

L-5 55

vr

В.1

Bx.S

I

52

.

1474836

8ux.2

.5ффЛ/лЛ

«.ff

W

/F4L.

Ябл.5

D

фиь.Ъ

ФигЛ

1474836

fГ-1;

а

N tlt--rj

Л А А Л rf....rri

Л

1 2 3 ЦА{ .

2Пз П f П И Р/

ГП .Ј

з # 5

П;;а

гfА 2

П Ш i ) Л EV

ii

/

J:-г

J:-г

а

«ь.

|I

|

j i .«

«tI-/

Фиг. 5

J:-г

а

«ь.

.LФиг 7 a.1.1

t

L

fc

g|l Э I S I I 8 I И II

il

fr

II i

111 И

.ЗГс

H II Ml I II JL ,- 2/i:JTJT

ittltlll I 1 Ml II e

. . m

.Г g

ZU

STc I

a

гтс, я

I I It I И I I I IN 1 И J

.ftp

JTc

i a

.TC

II i

,37t

И l a

| Перестраиваемый селектор импульсных последовательностей | 1980 |

|

SU940287A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-04-23—Публикация

1987-04-14—Подача