| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления микропроцессорной системой | 1985 |

|

SU1283760A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1510012A1 |

| Устройство динамического преобразования адреса | 1988 |

|

SU1501055A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1999 |

|

RU2153699C1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| УСТРОЙСТВО ДЛЯ КЛАССИФИКАЦИИ ПОСЛЕДОВАТЕЛЬНОСТИ ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2453915C1 |

| Электронное устройство (его варианты) | 1982 |

|

SU1086414A1 |

| Устройство для решения задач математической физики | 1989 |

|

SU1656552A1 |

| Оперативное запоминающее устройство | 1989 |

|

SU1656591A1 |

| Устройство буферной памяти | 1988 |

|

SU1596390A1 |

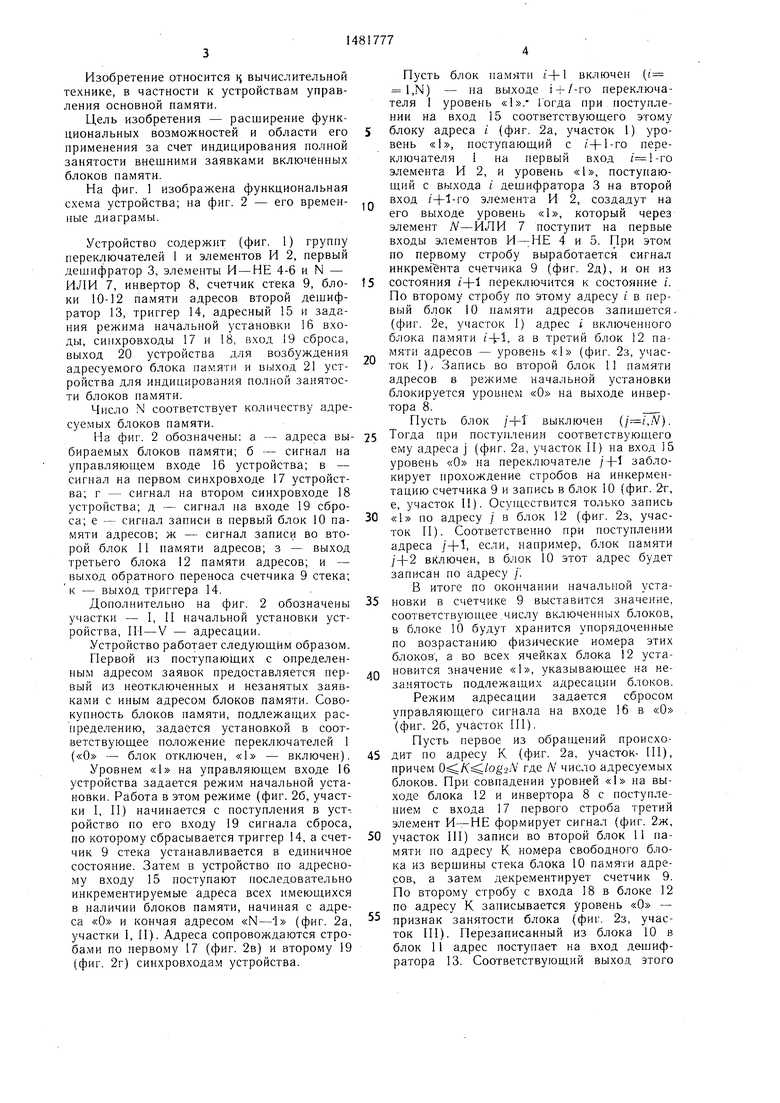

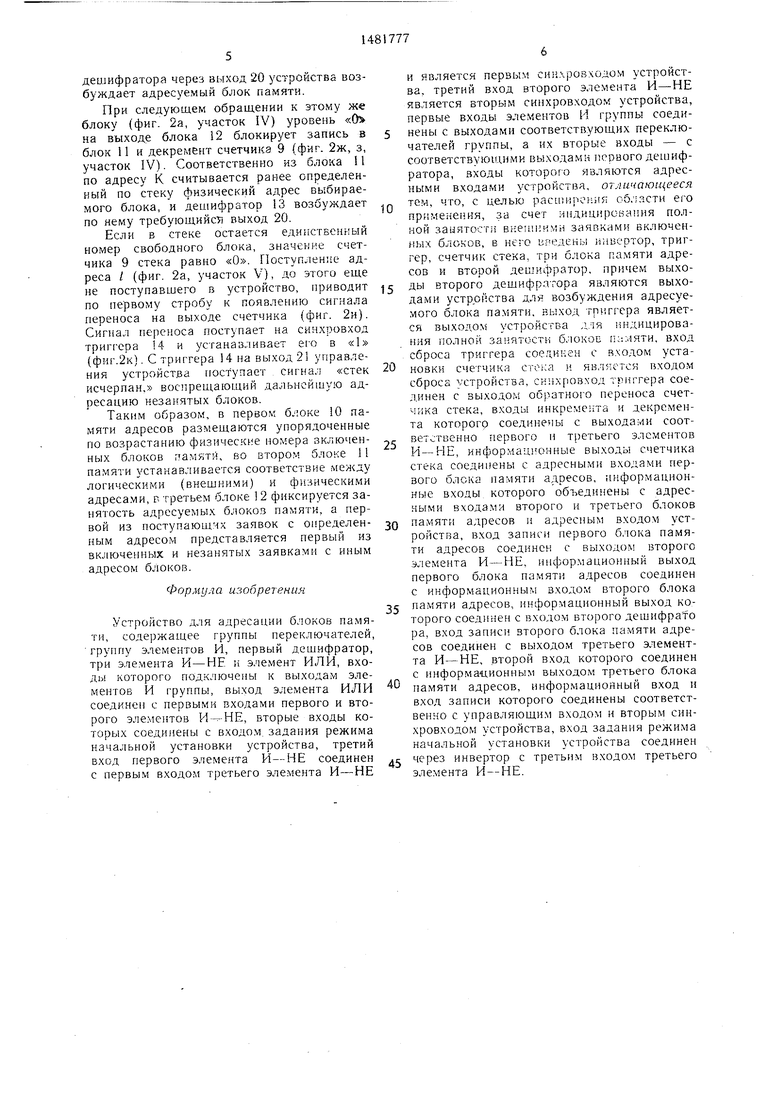

Изобретение относится к вычислительной технике и ,в частности, к устройствам управления основной памятью. Целью изобретения является расширение области применения устройства за счет индицирования полной занятости внешними заявками включенных блоков. Устройство для адресации блоков памяти содержит N переключателей 1 и элементов И 2, первый дешифратор 3, три элемента И-НЕ 4-6, элемент N -ИЛИ 7, инвертор 8, счетчик стека 9, три блока памяти адресов 10-12, второй дешифратор 13 и триггер 14. 2 ил.

| Устройство для адресации блоков памяти | 1980 |

|

SU1024926A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для адресации блоков памяти | 1984 |

|

SU1198565A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-26—Подача