1305

фрируется. На одном из выходов блока 2 формируется сигнал, поступающий на вход 19 соответствующего элемента 4. Сигнал с выхода 14 также изменяет состояние счетчика 3, сигнал на соответствующем выходе которого поступает на вход 24 соответствующе

1

Изобретение относится к вычислительной технике и может быть использовано при построении буферных запоминающих устройств,

Целью изобретения является повыше ние быстродействия устройства.

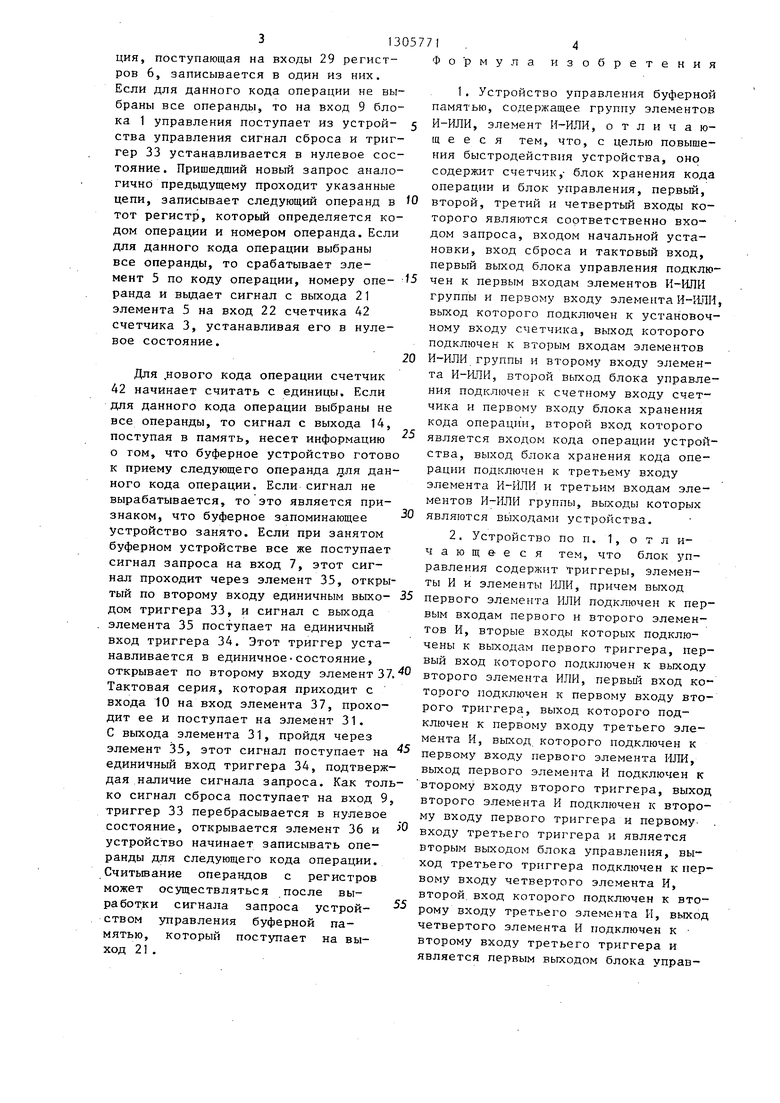

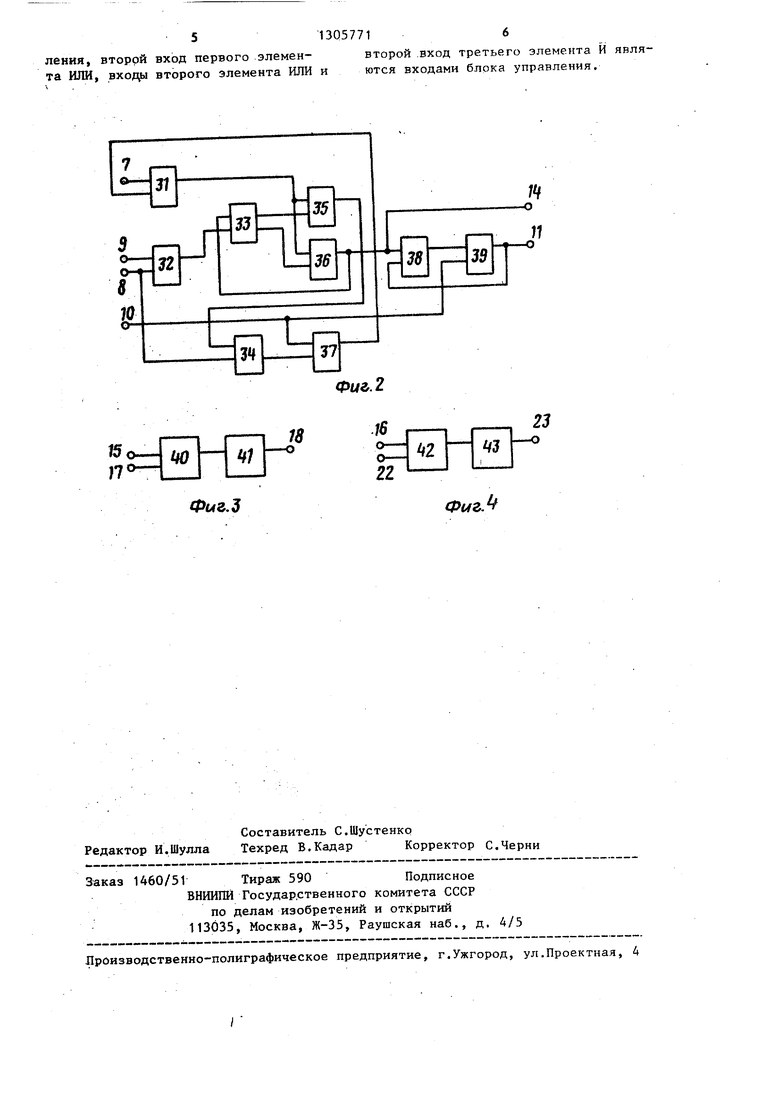

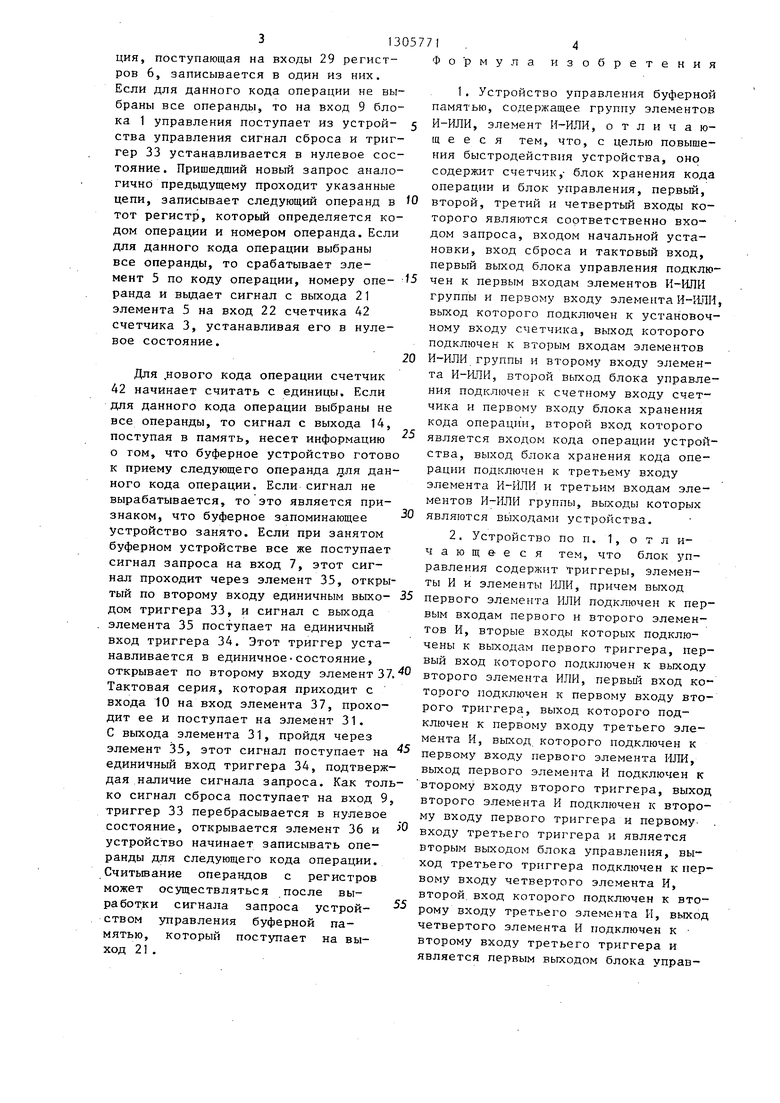

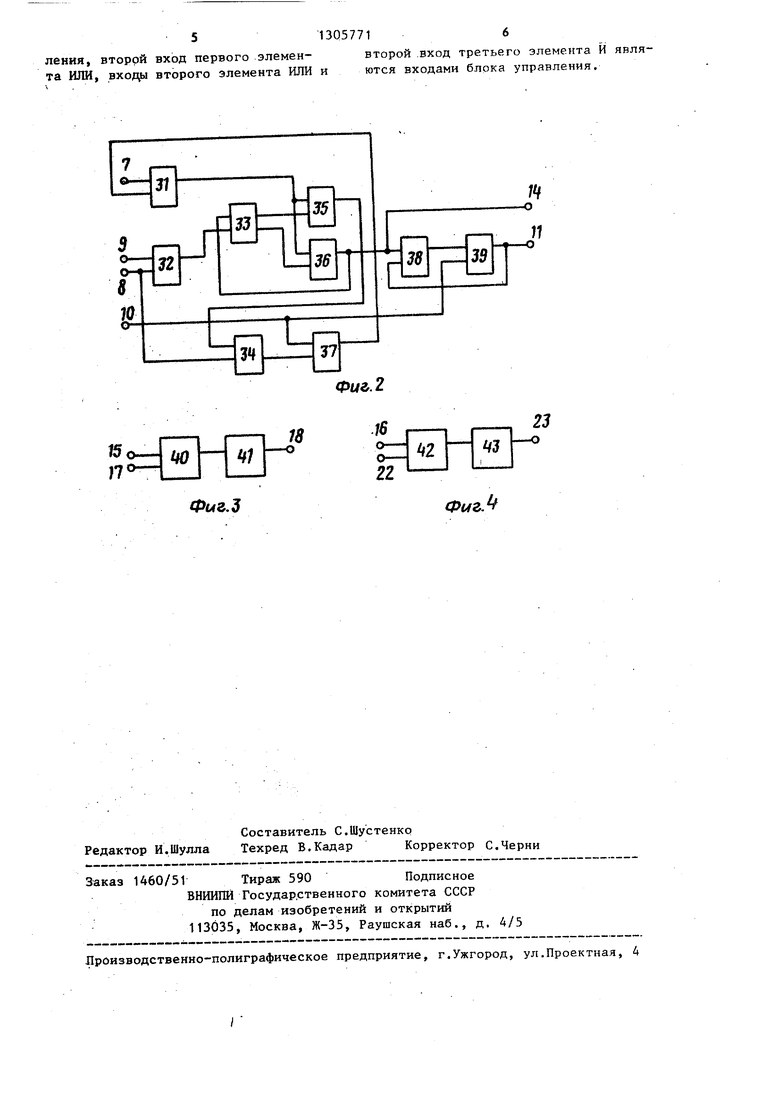

На фиг. 1 приведена структурная схема устройства управления буферной памятью; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема счетчика; на, фиг. 4 - функциональная схема блока хранения кода операции.

Устройство включает блок 1 управления, блок 2 хранения кода операций счётчик 3, группу элементов И-ИЛИ 4, элемент И-ИЛИ 5, регистры 6, вход 7 запроса, вход 8 начальной установки, вход 9 сброса, тактовый вход 10, выход 11 блока 1 управления, входы 12 элементов И-ИЛИ 4, вход 13 элемента И-ИЛИ 5, выход 14 блока 1 управления вход 15 блока 2 хранения кода операций, вход 16 счетчика 3, вход 17 бло- ка 2 хранения кода операций, вькод 18 блока 2 хранения кода операции, входа 19 элементов И-ИЛИ 4, вход 20 элемента И-ИЖ 5, выход 21 элемента И-ИЛИ 5 вход 22 счетчика 3, выход 23 счетчи- ка 3, входы 24 элементов И-ИЛИ 4, вход 25 элемента И-ИЛИ 5, выходы 26 элементов И-ИЛИ 4, входы 27 регистров 6, информационный вход 28, входы 29 регистров 6 являются выходом устройства, и информационные выходы 30.

Блок 1 управления включает элементы РШИ 31 и 32, триггер 33 занятости триггер 34 запроса, элементы И 35 - 37, триггер 38 пуска, элемент И 39. Блок 2 хранения кода операции включает регистр 40 (кода операции) и деши

го элемента 4. На выходе этого элемента 4 формируется выходной сигнал устройства. Если для данного кода операций выбраны все операнды, то на выходе 21 элемента 5 появляется сигнал, устанавливающий счетчик 5 в нулевое состояние. 1 з.п, ф-лы, 4 ил.

5

0

5 о

Q

5

фратор 41. Счетчик 3 (номера операндов) включает счетчик 42 и дешифратор 43.

Устройство работает следующим образом.

В исходное Состояние устройство устанавливается при приходе сигнала на вход 8. При этом триггер 33 (занятости) , триггер 34 (запросов) и триггер 38 (пуска) устанавливаются а нулевое состояние. При поступлении сигнала запроса , к входу 7 он проходит через элемент ИЛИ 31, через элемент И 36,. открытьй по второму входу нулевым выходом триггера 33, и поступает на единичные входы триггеров 38 и 33 и вькод 14. Триггер 38 устанавливается в единичное состояние и выходным сигналом открывает элемент И 39. Тактовый импульс, который поступает по входу 10, проходит элемент И 39 и поступает на выход 11, а затем - на входы 12 элементов 4. Сигнал с выхода 14 поступает на вход 15 регистра 40 блока 2 и записывает текущий код операции, который поступает по входу 17. С выхода регистра 40 код операции поступает на вход дещифратора 41, на одном из выходов которого появляется высокий уровень, который поступает на входы 19 элементов 4 и вход 20 элемента 5. Кроме того, сигнал с выхода 14 поступает на вход 16 счетчика 42 счетчика 3 и добавляет в счетчик единицу. Состояние счетчика 3 с выхода 23 поступает на входы 24 элементов 4 и на вход 25 элемента 5.

Один из элементов 4 открывается и пропускает сигнал на выход 26, а также на выход элемента 5. Та схема, которая пропускает сигнал, стробиру- ет свой регистр 6, поэтому информа3130577

ция, поступающая на входы 29 регистров 6, записывается в один из них. Если для данного кода операции не выбраны все операнды, то на вход 9 блока 1 управления поступает из устрой- 5 ства управления сигнал сброса и триггер 33 устанавливается в нулевое состояние. Пришедший новый запрос аналогично предьщущему проходит указанные

Формула изобретения

1. Устройство управления буферной памятью, содержащее группу элементов И-ИЛИ, элемент Н-ИЛИ, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит счетчик,- блок хранения кода операции и блок управления, первый.

цепи, записывает следующий операнд в 0 второй, третий и четвертый входы ко- тот регистр, который определяется кодом операции и номером операнда. Если для данного кода операции выбраны все операнды, то срабатывает элемент 5 по коду операции, номеру one- 5 ранда и вьщает сигнал с выхода 21 элемента 5 на вход 22 счетчика 42 счетчика 3, устанавливая его в нулевое состояние.

торого являются соответственно входом запроса, входом начальной установки, вход сброса и тактовый вход, первый выход блока управления подключен к первым входам элементов И-ИЛН группы и первому входу элемента И-1ШИ выход которого подключен к установочному входу счетчика, выход которого подключен к вторым входам элементов И-ИЛИ группы и второму входу элемента И-ВДИ, второй выход блока управления подключен к счетному входу счетчика и первому входу блока хранения кода операции, второй вход которого является входом кода операции устрой25

торого являются соответственно входом запроса, входом начальной установки, вход сброса и тактовый вход, первый выход блока управления подключен к первым входам элементов И-ИЛН группы и первому входу элемента И-1ШИ, выход которого подключен к установочному входу счетчика, выход которого подключен к вторым входам элементов И-ИЛИ группы и второму входу элемента И-ВДИ, второй выход блока управления подключен к счетному входу счетчика и первому входу блока хранения кода операции, второй вход которого является входом кода операции устрой30

Для .нового кода операции счетчик 42 начинает считать с единицы. Если для данного кода операции выбраны не все операнды, то сигнал с выхода 14, поступая в память, несет информацию о том, что буферное устройство готово к приему следующего операнда ля данного кода операции. Если сигнал не вырабатывается, то это является признаком, что буферное запоминающее устройство занято. Если при занятом буферном устройстве все же поступает сигнал запроса на вход 7, этот сигнал проходит через элемент 35, открытый по второму входу единичным выхо- 35 первого элемента ИЛИ подключен к пер- дом триггера 33, и сигнал с выхода вым входам первого и второго элемен- элемента 35 поступает на единичный тов И, вторые входы которых подклю- вход триггера 34. Этот триггер устанавливается в единичное-состояние,

открывает по второму входу элемент 37. второго элемента ИЛИ, первьш вход ко- Тактовая серия, которая приходит с торого подключен к первому входу вто- входа 10 на вход элемента 37, проходит ее и поступает на элемент 31. С выхода элемента 31, пройдя через элемент 35, этот сигнал поступает на единичный вход триггера 34, подтверждая наличие сигнала запроса. Как только сигнал сброса поступает на вход 9, триггер 33 перебрасывается в нулевое состояние, открывается элемент 36 и устройство начинает записывать операнды для следующего кода операции. Считьюание операндов с регистров может осуществляться после выработки сигнала запроса устройством управления буферной памятью, который поступает на выства, выход блока хранения кода операции подключен к третьему входу элемента И-ЙЛИ и третьим входам элементов И-ИЛИ группы, вькоды которых являются выходами устройства.

2. Устройство по п. 1, о т л и- чающее ся тем, что блок управления содержит триггеры, элементы И и элементы ИЛИ, причем выход

чены к выходам первого триггера, первый вход которого подключен к выходу

55

рого триггера, выход которого подключен к первому входу третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход первого элемента И подключен к второму входу второго триггера, выход второго элемента И подключен к второму входу первого триггера и первому- . входу третьего триггера и является вторым выходом блока управления, выход третьего триггера подключен к первому входу четвертого элемента И, второй, вход которого подключен к второму входу третьего элемента И, выход четвертого элемента И подключен к второму входу третьего триггера и является первым выходом блока управход 21 .

Формула изобретения

1. Устройство управления буферной памятью, содержащее группу элементов И-ИЛИ, элемент Н-ИЛИ, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит счетчик,- блок хранения кода операции и блок управления, первый.

второй, третий и четвертый входы ко-

торого являются соответственно входом запроса, входом начальной установки, вход сброса и тактовый вход, первый выход блока управления подключен к первым входам элементов И-ИЛН группы и первому входу элемента И-1ШИ, выход которого подключен к установочному входу счетчика, выход которого подключен к вторым входам элементов И-ИЛИ группы и второму входу элемента И-ВДИ, второй выход блока управления подключен к счетному входу счетчика и первому входу блока хранения кода операции, второй вход которого является входом кода операции устройпервого элемента ИЛИ подключен к пер- вым входам первого и второго элемен- тов И, вторые входы которых подклю-

первого элемента ИЛИ подключен к пер- вым входам первого и второго элемен- тов И, вторые входы которых подклю-

ства, выход блока хранения кода операции подключен к третьему входу элемента И-ЙЛИ и третьим входам элементов И-ИЛИ группы, вькоды которых являются выходами устройства.

2. Устройство по п. 1, о т л и- чающее ся тем, что блок управления содержит триггеры, элементы И и элементы ИЛИ, причем выход

первого элемента ИЛИ подключен к пер- вым входам первого и второго элемен- тов И, вторые входы которых подклю-

второго элемента ИЛИ, первьш вход ко- торого подключен к первому входу вто-

чены к выходам первого триггера, первый вход которого подключен к выходу

второго элемента ИЛИ, первьш вход ко- торого подключен к первому входу вто-

5

рого триггера, выход которого подключен к первому входу третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход первого элемента И подключен к второму входу второго триггера, выход второго элемента И подключен к второму входу первого триггера и первому- . входу третьего триггера и является вторым выходом блока управления, выход третьего триггера подключен к первому входу четвертого элемента И, второй, вход которого подключен к второму входу третьего элемента И, выход четвертого элемента И подключен к второму входу третьего триггера и является первым выходом блока управ513057716

ления, второй вход первого -элемен- второй .вход третьего элемента И явля- та ШШ, Bxof второго элемента ИЛИ и ются входами блрка управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении буферных запоминающих устройств. Цель изобретения - повышение быстродействия устройства управления буферной памятью. Устройство содержит блок 1 управле- : ния, блок 2 хранения кода операции, счетчик 3, группу элементов И-ИЛИ 4 и элемент И-ИЛИ 5. В исходное состояние устройство устанавливается сиг- налом на входе 8 начальной установки. При поступлении сигнала на вход 7 запроса он синхронизируется тактовыми сигналами, поступающими на вход 10. На выходе 11 блока 1 формируется импульс, стробируюп1ий по входам 12 элементы И-ИЛИ 4. Одновременно сигнал с выхода 14 блока 1 записывает код one- с рация с входа 17 в блок 2, где деши- сл 30 со о ел J

щ

Фмг.2

15 17

18

.16

23

22

Фмг.5

Составитель С.Щустенко Редактор И.Шулла Техред В.Кадар Корректор С.Черни

Заказ 1460/51 Тираж 590 Подписное ВНИИПИ Государ.ственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фиг.

| Буферное запоминающее устройство | 1982 |

|

SU1053163A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1109798A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-23—Публикация

1985-10-14—Подача