1}

7

4

СО

о:

8

ю

12

ел

ФиеЛ

Изобретение относится к импульс нсзй технике и может использоваться в вычислительных системах.

Целью изобретения является расширение области применения устройства за счет формирования знаковго разряда.

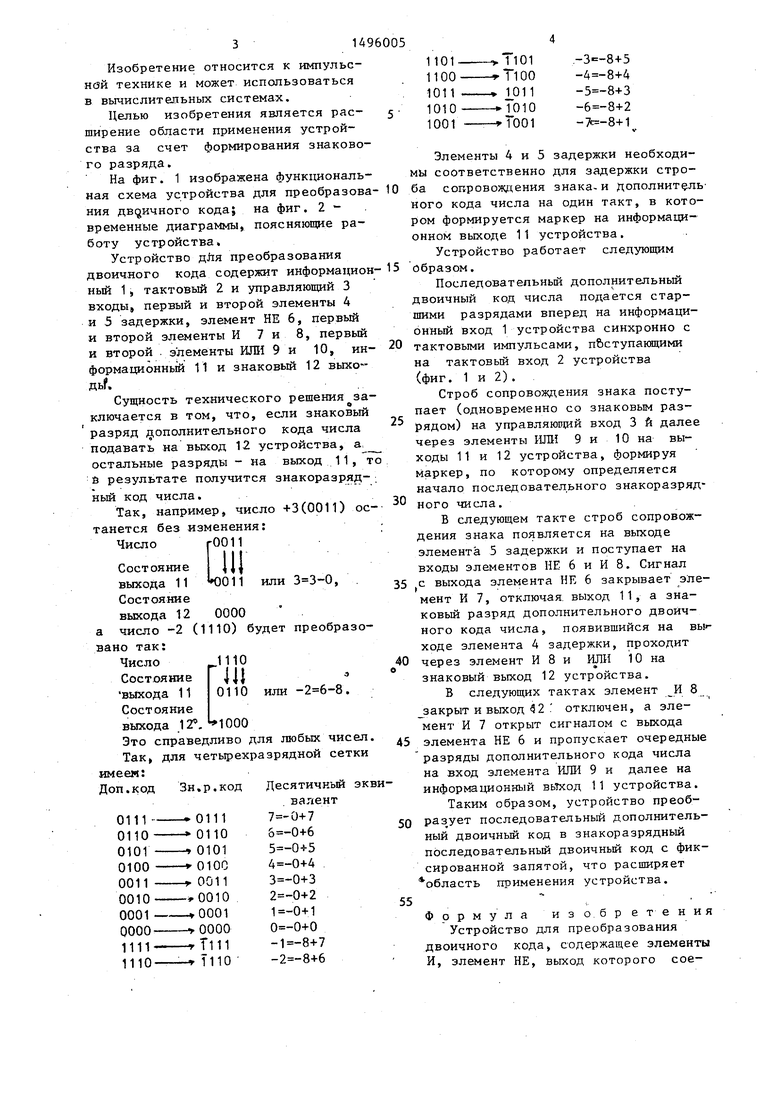

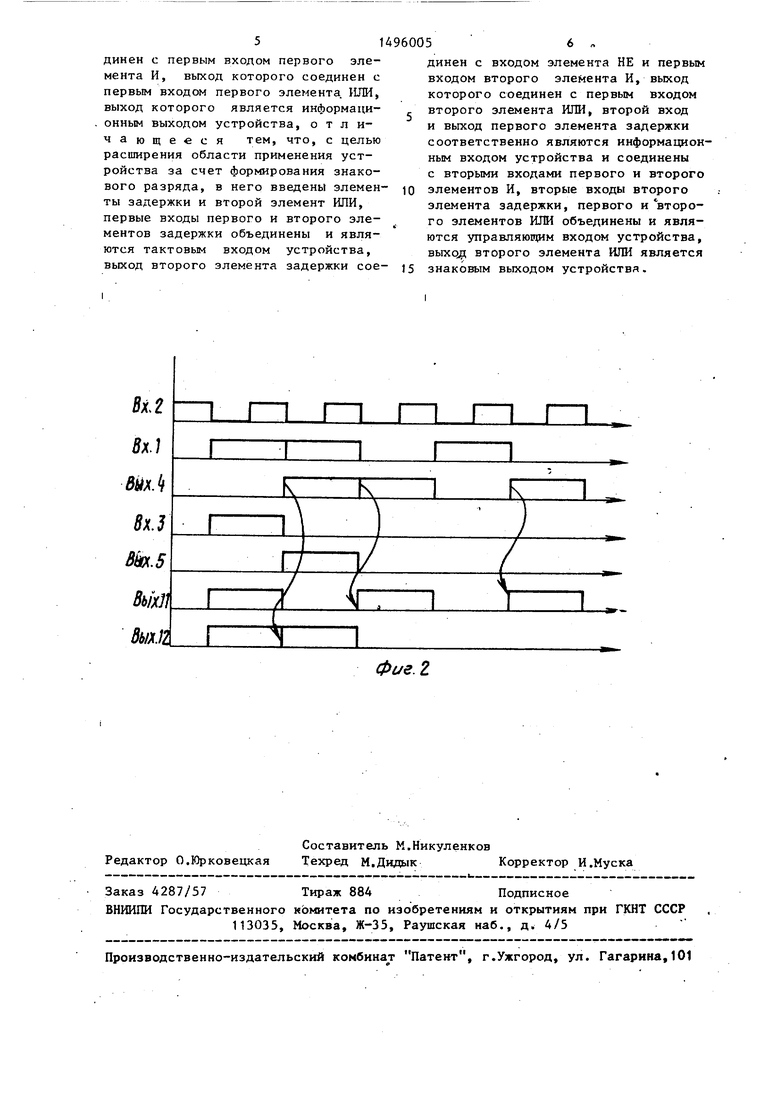

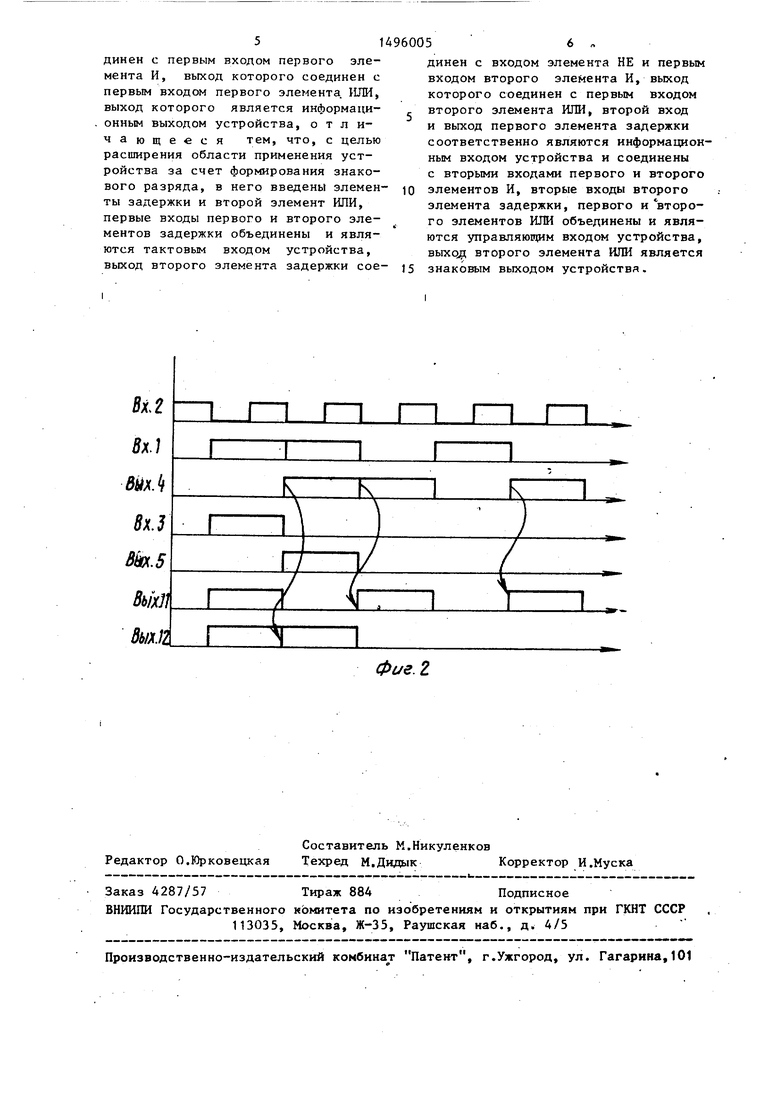

На фиг. 1 изображена функционалная схема устройства для преобразония дв(2ичного кода; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство дйя преобразования

двоичного кода содержит информаци

ный 1, тактовый 2 и управляющий 3

входы, первый и второй элементы 4

и 5 задержки, элемент НЕ 6, первый

и второй элементы И 7 и 8, первы

и второй -элементы ИЛИ 9 и 10, иформационньй 11 и знаковый 12 выко

Hbf.

Сущность технического решения зключается в том, что, если знаковы разряд дополнительного кода числа подавать на выход 12 устройства, а остальные разряды - на выход 11, и результате получится знакоразряд ный код числа.

Так, например, число +3(0011) отанется без изменения:

Число rOOII

Состояниеill

выхода 114)011 или ,

Состояние

выхода 120000

а число -2 (1110) будет преобразовано так:

Число.1110

Состояние выхода 11 Состояние выхода 1 Т,

0110

1000

или .

Это справедливо для любых чисел. Так, для четырехразрядной сетки имееп:

Элементы 4 и 5 задержки необходимы соответственно для задержки стро- ба сопровождения знака-и дополнит ль кого кода числа на один такт, в котором формируется маркер на информационном выходе 11 устройства.

Устройство работает следующим

0

5

0

5

0

5

0

5

Последовательньй дополнительньй двоичный код числа подается старшими разрядами вперед на информационный вход 1 устройства синхронно с тактовыми импульсами, пбступающими на тактовый вход 2 устройства (фиг. 1 и 2).

Строб сопровождения знака поступает (одновременно со знаковым разрядом) на управляюпщй вход 3 и далее через элементы ИЛИ 9 и 10 на выходы 11 и 12 устройства, формируя Маркер, по которому определяется начало последовательного знакоразряд- ного числа.

В следующем такте строб сопровождения знака появляется на выходе элемента 5 задержки и поступает на входы элементов НЕ 6 и И 8. Сигнал с выхода элемента HR 6 закрывает элемент И 7, отключая выход 11, а знаковый разряд дополнительного двоичного кода числа, появившийся на вы ходе элемента 4 задержки, проходит через элемент И 8 и Ш1И 10 на знаковый выход 12 устройства.

В следующих тактах элемент И 8 закрыт и выход 42 отключен, а элемент И 7 открыт сигналом с выхода элемента НЕ 6 и пропускает очередные разряды дополнительного кода числа на вход элемента ИЛИ 9 и далее на информационный вьтход 11 устройства.

Таким образом, устройство преоб- последовательный дополнительный двоичный код в знакоразрядный последовательный двоичный код с фиксированной запятой, что расширяет область применения устройства.

Формула изобретения

Устройство для преобразования двоичного кода, содержащее элементы И, элемент НЕ, выход которого сое-

динен с первым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого является информационным выходом устройства, отличающееся тем, что, с целью расширения области применения устройства за счет формирования знакового разряда, в него введены элементы задержки и второй элемент ИЛИ, первые входы первого и второго элементов задержки объединены и являются тактовым входом устройства, выход второго элемента задержки сое

5

0

динен с входом элемента НЕ и первым входом второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход и вьпсод первого элемента задержки соответственно являются информационным входом устройства и соединены с вторыми входами первого и второго элементов И, вторые входы второго элемента задержки, первого и второго элементов ИЛИ объединены и являются управляющим входом устройства, выхрд второго элемента ИЛИ является знаковым выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования дополнительного двоичного кода в знакоразрядный | 1987 |

|

SU1496004A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для умножения | 1987 |

|

SU1411733A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Преобразователь кодов | 1987 |

|

SU1527715A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1988 |

|

SU1569983A1 |

| Устройство для умножения 12N-разрядных двоичных чисел | 1988 |

|

SU1589271A1 |

Изобретение относится к импульсной технике и может использоваться в вычислительных системах. Устройство преобразует последовательный дополнительный двоичный код в знакоразрядный последовательный двоичный код с фиксированной запятой, подавая на выход 12 знаковый, а на выход 11 остальные разряды кода, что расширяет область применения устройства. Устройство содержит информационный 1, тактовый 2 и управляющий 3 входы, элементы 4,5 задержки, элемент НЕ 6, элементы И 7,8, элементы ИЛИ 9 и 10, информационный 11 и знаковый 12 выходы. 2 ил.

Фиг. 2,

| Клингман Э | |||

| Проектирование специализированных микропроцессорных систем | |||

| - М.: Мир, 1985, с | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Папернов А.А | |||

| Логические основы цифровой вычислительной техники.- М.: Советское радио, 1972, с | |||

| Способ приготовления кирпичей для футеровки печей, служащих для получения сернистого натрия из серно-натриевой соли | 1921 |

|

SU154A1 |

Авторы

Даты

1989-07-23—Публикация

1987-10-19—Подача