8

Ш

Ю

СЛ

Изобретение относится к вычислительной технике и может быть использовано при построении преобразователя двоичного кода со знаком в много- значный код.

Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования двоичного кода в знакоразрядньш код.

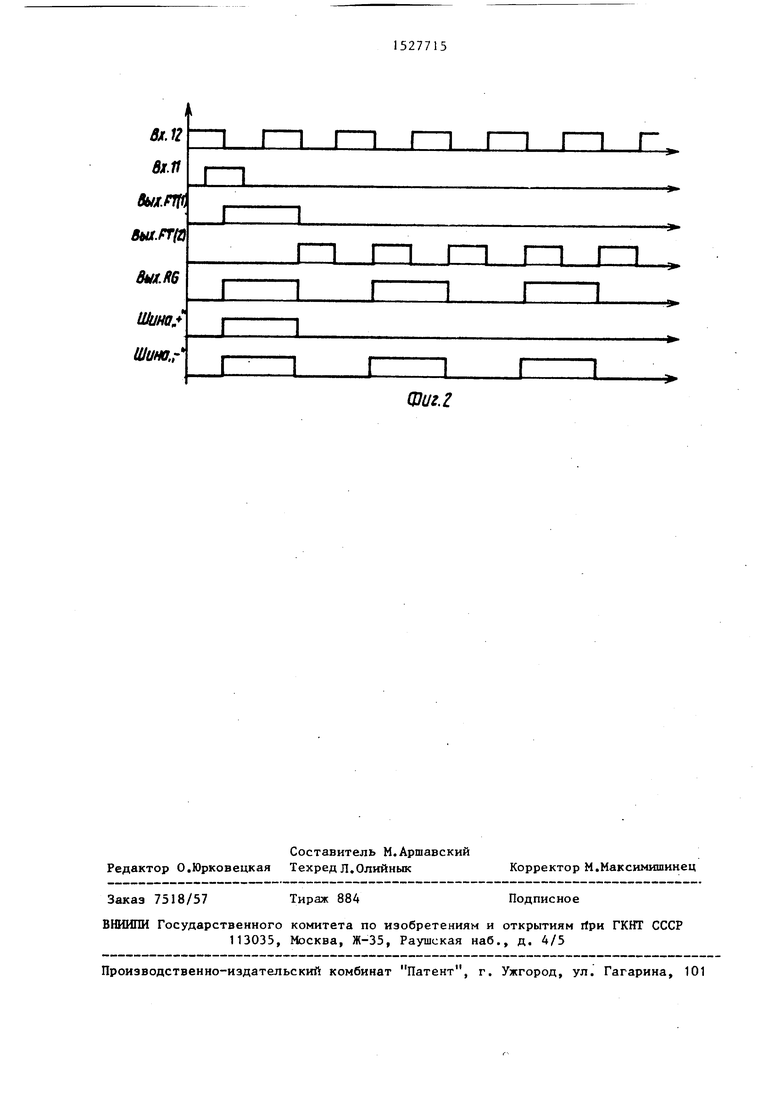

Па фиг.1 представлена схема предлагаемого преобразователя; на фиГо2 - временная диаграмма его работы.

Преобразователь содержит распре- делитель 1 импульсов, сдвиговый регистр 2, элемент НЕ 3, элементы И 4 и 5, элементы НЛИ 6 и 7, выходы отрицатбльного 8 и положительного 9 чисел преобразователя, информационный вход 10 преобразователя, вход 11 записи преобразователя, .тактовый вход 12 преобразователя и триггер 13. Совокупность элементов 3 - 7 с соответствующими связями является выходным преобразователем 14.

Преобразователь работает следующим образом.

По стробу записи, поступающему на вход 11 записи, входной код числа вводится в преобразователь через ин формационньш вход 10, причем знако-. вый разряд попадает в триггер 13, а остальные заносятся в сдвиговый регистр 2 так, что на его последова- тельном выходе оказывается старший разряд числа. Распределитель 1 импульсов устанавливается в исходное состояние. Импульс с первого выхода распределителя 1 импульсов поступает через элементы ИЛИ 6 и 7 на выходы положительного 9 и отрицательного 8 чисел преобразователя, формируя мар-i кер,. по которому определяется начало последовательного знакоразрядного чис ла. Сигнал с выхода триггера 13, эквивалентный знаковому разряду .входного кода, подключает выход сдвигового регистра 2 к выходам отрицательного 8 либо положительного 9 чисел преобра- зователя соответственно через пары элементов 4, 6 и 5, 7.

В каждом последующем такте под действием импульсов с второго выхода распределителя 1 импульсов происходит сдвиг кода в сдвиговом регистре 2 на один разряд в сторону старших разрядов.

Очередные разряды последовательног кода с выхода сдвигового регистра 2 поступают на выбранный в первом такте выход. Второй выход остается отключенным до поступления на информационный вход преобразователя следующего числа.

Формула изобретения

Преобразователь кодов, содержащий сдвиговый регистр, распределитель импульсов и выходной преобразователь, информационньй вход которого соединен с выходом сдвигового регистра, а тактовый вход выходного преобразователя соединен с первым выходом распределителя импульсов, второй выход которого соединен с тактовым входом сдвигового регистра, информационный вход которого соединен с информационным входом преобразователя, вход записи которого соединен с входом записи сдвигового регистра и входом пуска распределителя импульсов, тактовый вход которого соединен с тактовым входом преобразователя, выходы которого соединены с выходами выходного преобразователя, отличающийся тем, что, с целью расширения класса решаемых задач за счет обеспечения преобразования в зна коразрядный код, в него введены триггер знака, а выходной преобразователь содержит первьй и второй элементы ИЛИ, первый и второй элементы И и элемент НЕ, выход которого соединен с первым входом первого элемен та И, а вход элемента НЕ соединен с выходом триггера и первым входом второго элемента И, второй вход которого соединен с вторым входом первого элемента И и является информационным входом выходного преобразователя, тактовый вход которого соединен с первыми входами первого и второго элементов ИЛИ, вторые входы которых соответственно соединены с выходами первого и второго элементов И, выходы первого и второго элементов ИЛИ являются соответственно выходами положи тельных и отрицательных чисел преобразователя, информационный вход которого соединен с информационным входом триггера, синхровход которого соединен с входом записи преобразователя .

Составитель М.Аршавский Редактор О.Юрковецкая Техред Л.Олийнык

Корректор М.Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| МАКРОПРОЦЕССОР | 2001 |

|

RU2210808C2 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Генератор последовательности чисел | 1983 |

|

SU1166089A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Преобразователь последовательного знакоразрядного кода в дополнительный двоичный код | 1983 |

|

SU1113796A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении преобразователей двоичного кода со знаком в многозначный код. Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования двоичного кода в знакоразрядный код. Поставленная цель достигается тем, что в преобразователь кодов, содержащий распределитель импульсов 1, сдвиговый регистр 2, выходной преобразователь 14, дополнительно введен триггер 13, а выходной преобразователь выполнен из элемента НЕ 3, элементов И 4, 5, элементов ИЛИ 6, 7. 2 ил.

Заказ 7518/57

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям йри ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

-П-|-|ЩЦт ЦТ . -- --- -- -

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписиое

| Клингман Э, Проектирование специализированных микропроцессорных систем.- М.: Мир, 1985, с | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1453598A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-07—Публикация

1987-11-23—Подача