Изобретеш1е относится к вычислительной технике, предназначено для генерации адресных последовательностей при функциональном контроле опе- j)aTHBHbix запоминающих устройств и может быть использовано также для задания тестовых последовательностей при функциональном контроле других цифро вьгх устройств, генерации псевдослучайных чисел с равномерным законом распределения.

Цель изобретения - расширение области применения за счет генерации произвольных тестовых последователь- ностей.

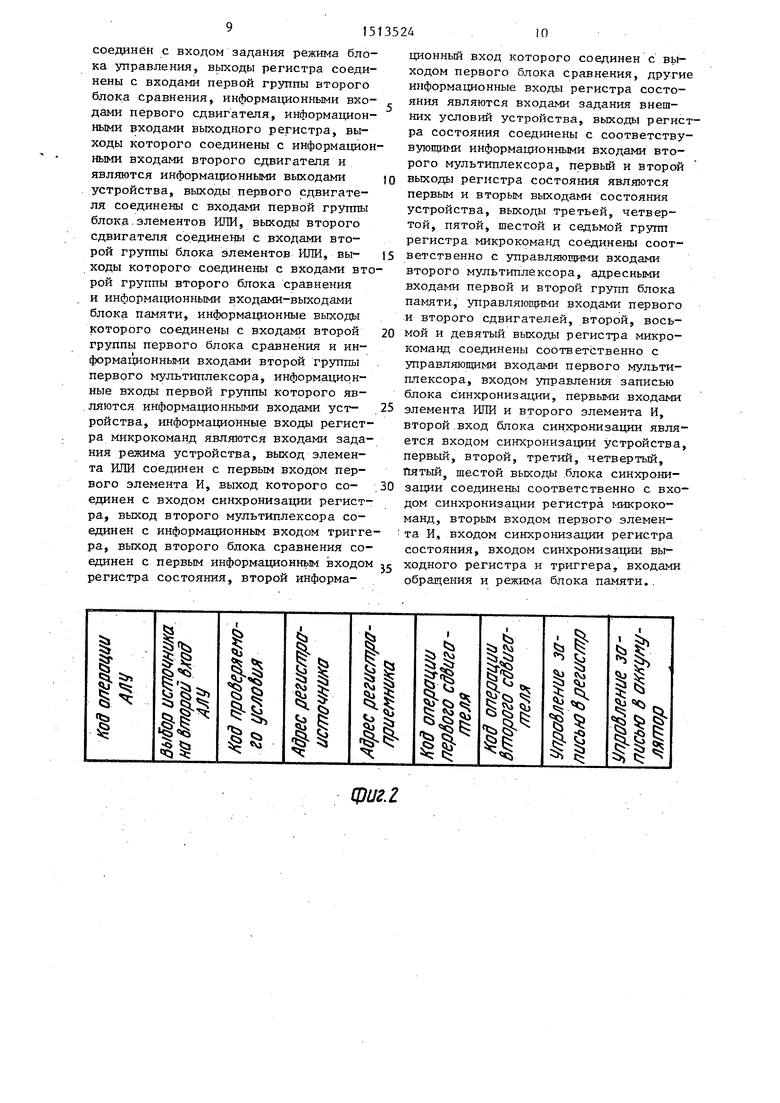

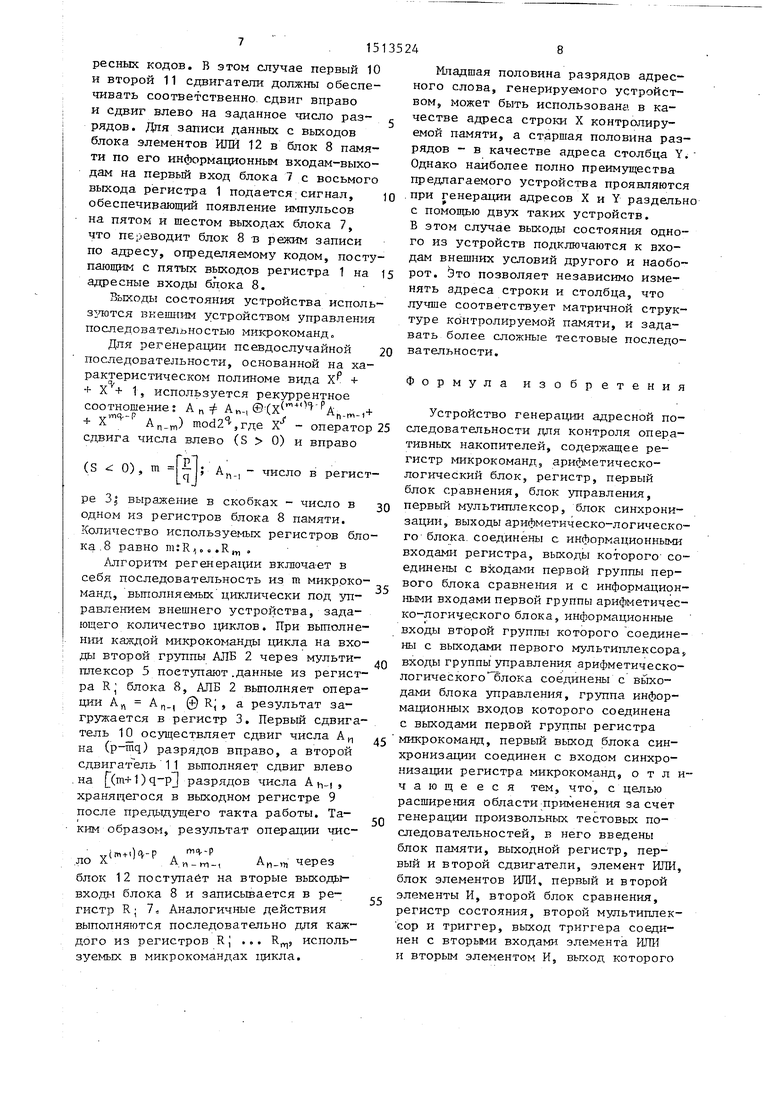

На фиг. 1 приведена структурная, схема устройства; на фиг. 2 - структура слова микрокоманды, вьтолняемой устройством; на-фиг. 3 - време:нная диаграмма работы устройства.

Устройство содержит регистр 1 .микрокоманд, арифметическо-логический бло (АЛБ) 2, регистр 3, первый блок 4 сравнения, блок 5 управления, йервый мультиплексор 6, блок 7 синхронизации .блок 8 памяти, выходной регистр 9, первый 10 и второй 11 сдвигатели, блок элементов ИЛИ 12, второй блок 13 сравнения, регистр 14 состояния, второй мультиплексор 15, триггер 16, элемент ИГШ 17, первый 18 и второй 1 элементы И, информационные входы 20 устройства, входы 21 задания режима, информационные,выходы 22 устройства, выходы 23.состояния устройства вход 24 синхр.онизации, входы 25 задания внешних условий.

В качестве АЛБ 2, блока 8 памяти, сдвигателей 10 и 11 могут быть испол зованы БИС соответствующего функционального назначения, ..например БИС АЛУ К500Ш1181, БИС двухадресной регистровой памяти К1800РП6,. многоразрядный программируемый сдвигатель К1800ВР8. Для получения необходимой разрядности устройства используется параллельное подключение нескольких секций указанных БИС.

Устройство генерирует адресные последовательности путем выполнения мирокоманд, загружаемых в регистр 1. Выходы и группы выходов регистра 1 соответствуют полям микрокоманды, приведенным на фиг. 2.

Устройство работает следующим образом,

В начале работы проводится загруз ка регистров блока 8 через информа

з

0

о

g

5

5

0

5

ционцые входы устройства. Для этого сигнал с первого выхода регистра 1 переключает мультиплексор на прием информации с информаи;ионных входов. Информация с первых выходов регистра 1 задает режим пересылки данных с входа АЛБ 2 на его выход и далее на вход регистра 3. Сигнал с выхода регистра 1, проходя через элемент ИЛИ 17 на вход первого элемента И 18, разрешает прохождение сигнала с второго выхода блока 7 через первый элемент И 18 на вход синхронизации регистра 3, в результате чего данные с выхода АЛБ 2 записьтаются в регистр 3. Информация с выходов регистра 1 устанавливает первый сдвигатель 10 в режим передачи информации на выход без изменения, а второй сдвигатель 11 с помощью сигналов управления с седьмых выходов регистра 11 поддерживает на своих выходах состояние логического нуля. Поэтому с выхода регистра 3 данные без изменения проходят через первый сдвигате ть 10 и блок элементов ИЛИ 12 на информационные входы-выходы блока 8 памяти. Сигнал, поступающий с выхода регистра 1 на первый вход блока 7, определяет подачу сигналов с пятого и шестого выходов блока 7 соответственно на входы запрета выхода и записи по второму информационно- Яу выходу-входу блока 8. При этом пре- кращается вьшод информации из блока 8 на его входы-выходы, разрешает- . ся ввод информации в блок 8 с выходов блока элементов ИЛИ 12 через Заказанные выходы-входы и производится запись в блок 8 по адресу, определяемому кодом, поступающим с выходов регистра 1 на вторые адресные входы блока В . Описанные действия вьшолргяются за один такт работы устройства. Для загрузки регистров блока 8 необходимо выполнение соответствующего числа микрокоманд.

Рассматривается работа устройства в течение одного такта работы. Вначале проводится загрузка микрокоманды в регистр .1. Это происходит по переднему фронту сигнала, поступа- ЮЕчего с первого выхода блока 7 на вход синхронизации регистра 1. Во всех случаях, когда на входе блока 5 установлен уровень логического О, код операции АЛУ определяется информацией, поступающей с первых выходов регистра 1 на входы блока 5 и далее

515

с выходов блока 5 на входы управления АЛБ 2. Если с выхода регистра 1 и с выхода триггера 16 на входы второго элемента И 19 подаются логические 1, то сигнал с выхода элемента И 19, поступая на вход блока 5 управления, определяет для АЛБ 2 режим передачи данных с его входов на выход без изменения, независимо от информации на первых выходах регистра 1 Сигнал, поступающий с выхода регистра 1 на вход управления м льтиплексором 6, подключает к входам АЛБ 2 либо информационные входы устройства, либо выходы блока 8. Адреса регистров блока 8, подключаемые к информационным выходам, определяются соответственно кодами, поступающими с четвертых и пятых выходов регистра 1 на первые и вторые адресные входы блока 8. При наличии на первом входе первого элемента И 18 сигнала разрешения, который поступает через второй элемент ИЛИ 17 либо с вькода регистра 1, либо с выхода триггера 16, синхронизирующий импульс- с второго выхода блока 7 через элемент И 18 поступает на вход синхронизащш регистра 3, обеспечивая запись в него с выходов АЛБ 2 результата вьтолне- ния арифметического или логического действия. Таким образом, кроме безусловных операций, устройство позволяет выполнять условные операции двух видов: причем условные операции 1-го вида (на выходе регистра 1 в этом случае логический О) изменяют содержимое регистра 3 в соответствии

с кодом на первых выходах регистра 1 лишь после удовлетворения проверяемого условия. Условные микрокоманды 2-го вида (на выходе регистра 1 логическая 1) при отсутствии условия выполняют операцию АЛБ 2 в соответствии с кодом на первых выходах регистра 1, а при наличии условия осуществляют передачу данных с вторьгх входов АЛБ 2 на выходы без изменения благодаря тому, что сигнал с выхода второго элемента И 19, поступая на вход блока 5 управления, устанавливает на входах управления АЛБ 2 соответствующий код операции. Очевидно, что для

такэй микрокоманды в любом случае

I

производится запись данных в регистр

3. Минимальный набор.операций АЛБ 2 включает в себя: сложение, вычитание

46

увеличение и уменьшение на единицу, логические И, ИЛИ и HCIOIHHAJODIEE ИЛИ. Поступая с выходов регистра 3 на

первые входы блоков 4 и 13 сравнения, адресный код сравнивается с данньП Ш, подаваемыми на вторые входы этих элементов с выходов блока 8. С выходов элементов 4 и 13 результаты

сравнения поступают соответственно на второй и первьй входы регистра 14 и записьшаются в него по импульсу с третьего выхода блока 7. Информация с выходов регистра 14, а также с

входов внешних условрщ постзшает на входы мультиплексора 15, на входы управления которого с выходов регистра 1 подается код для выбора проверяемого условия при вьшолнении устройством условной операцш-1. Таким образом, проверяемый сигнал поступает с одного из входов мультиплексора 15 на его выход и далее на информационный вход триггера 16, причем логическал 1 означает, что условие удовлетворено. Информация записывается в триггер 16 в конце такта сигналом, подаваемым на вход синхронизации триггера с четвертого выхода блока 7,

Результат проверки условия может быть использован в следующем такте работы устройства для выполнения условной микрокоманды..

Данные с выходов регистра 3 поступают также на входы первого сдвига- теля 10 и выходного регистра 9, запись в который производится в конце такта сигналом с четвертого вькода блока 7. Это обеспечивает подачу адресного кода на выходы устройства и на информационные входы второго сдвигателя 11 с задержкой на один такт. Выполняемые сдвигателями 10и 11 операции определяются кодами, задаваемыми на их входах управления соответственно с шестых и седьмых выходов регистра 1. В зависимости от микрокоманды первый сдвигатель 10 может пересьшать данные с входов на выходы

без изменения, осуществлять их сдвиг на нужное число разрядов или поддерживать на выходах уровни логического О. Выходы второго сдвигателя 11 также могут быть установлены в состояние

логического О. Кроме того, возможен также сдвиг данных, задержанных на один такт. Операция сдвига для.второго сдвигателя 11 используется только при генерации псевдослучайных ад

ресных кодов. В этом случае первый 10 и второй 11 сдвигатели должны обеспечивать соответственно, сдвиг вправо и СДВ.ИГ влево на заданное число разрядов. Для записи данных с выходов блока элементов ИЛИ 12 в блок 8 памяти по его информационным входам-выходам на первый вход блока 7 с восьмого выхода регистра 1 подается;сигнал, обеспечивающий появление импульсов на пятом и шестом выходах блока 7, что переводит блок 8 -в режим записи по адресу, определяемому кодом, поступающим с пятых выходов регистра 1 на адресные входы блока 8.

Выходы состояния устройства исполь ззтотся вкешиим устройством управления последовательностью микрокоманд„

Для регенерации псевдослучайной последовательности, основанной на характеристическом полиноме вида Х + + X + 1, используется рекзфрентное соотношение; А „ , .,+ + Х АГ,„) mod2 ,гдe Х - оператор сдвига числа влево (S 0) и вправо

-fP

(S 0) , та - - ; - число в регистре 3| вьгражение в скобках - число в одном из регистров блока 8 памяти. Количество используемых регистров блока. В равно m:R;)oe. ,

Алгоритм регенерации включает в себя последовательность из m микрокоманд, вьшолняемых циклически под управлением внешнего устройства, задающего количество циклов. При выполнении каждой микрокоманды цикла на входы второй группы АЛБ 2 через мультиплексор 5 поступают.данные из регистра R; блока 8, АЛБ 2 выполняет операции А„ А„., © Rj а результат за- грз ается в регистр 3. Первый сдвига- тель 10 осуществляет сдвиг числа А, на (p-mq) разрядов вправо, а второй сдвигатЪль 11 выполняет сдвиг влево .на (т+1) разрядов числа А ji-.) , хранящегося в выходном регистре 9 после предьщущего такта работы. Таким образом, результат операции чис

ло ,.„ через

блок 12 поступает на вторые выходы- ВХОД1Ч блока 8 и записьшается в регистр R; 7. Аналогичные действия выполняются последовательно для каждого из регистров RJ . зуемьк в микрокомандах цикла.

исполь

Младшая половина разрядов адресного слова, генерируемого устройством, может быть использована в ка- честве адреса строки X контролируемой памяти, а старшая половина разрядов - в качестве адреса столбца Y. Однако наиболее полно преим5тцества предлагаемого устройства проявляются

при генерации адресов X и Y раздельно с помощью двух таких устройств. В этом случае выходы состояния одного из устройств подключаются к входам внешних условий другого и наоборот. Это позволяет независимо изменять адреса строки и столбца, что лучше соответствует матричной структуре контролируемой памяти, и задавать более сложные тестовые последо-

вательности.

Формула изобретения

Устройство генерации адресной последовательности для контроля оперативных накопителей, содержащее регистр микрокоманд, арифметическо- логический блок, регистр, первый блок сравнения, блок управления,

первый мультиплексор, блок синхронизации, выходы арифметическо-логическо- го-блока, соединены с информационными входами регистра, выходы которого соединены с входами первой группы первого блока сравнет-1я и с информационными входами первой группы арифметичас- ко-логиуеского блока, информационные входы второй группы которого соединены с выходами первого мультиплексора,

входы группы управления арифметическо- логического лока соединены с выходами блока управления, группа информационных входов которого соединена с выходами первой груцпы регистра

микрокоманд, первый выход блока синхронизации соединен с входом синхронизации регистра микрокоманд, о т л и- чающе еся тем, что, с целью расширения области применения за счет

0

генерации произвольных тестовых последовательностей, в него введены блок памяти, выходной регистр, первый и второй сдвигатели, элемент ИЛИ, блок элементов ИЛИ, первый и второй элементы И, второй блок сравнения, регистр состояния, второй мультиплек- сор и триггер, выход триггера соединен с вторыми входами элемента ИЛИ и вторым элементом И, выход которого

соединен с входом задания режима блока управления, вькоды регистра соединены с входами первой группы второго блока сравнения, информационными входами первого сдвигателя, информационными входами выходного регистра, выходы которого соединены с информационными входами второго сдвигателя и являются информационными выходами устройства, выходы первого сдвигателя соединены с входами первой группы блока.элементов ИЛИ, выходы второго сдвигателя соединены с входами второй группы блока элементов ИЛИ, вы- ходы которого соединены с входами второй группы второго блока сравнения и информаьщонными входами-выходами блока памяти, информационные выходы которого соединены с входами второй группы первого блока сравнения и информационными входами второй группы первого мультиплексора, информационные входы первой группы которого являются информационными входами уст- ройства, информационные входы регистра микрокоманд являются входами задания режима устройства, выход элемента ИЛИ соединен с первьш входом первого элемента И, выход которого со- единен с входом синхронизации регистра, выход второго мультиплексора соединен с информационным входом триггера, выход второго блока сравнения соединен с первым информационнь1м входом регистра состояния, второй информационный вход которого соединен с выходом первого блока сравнения, други информационные входы регистра состояния являются входами задания внешних условий устройства, выходы регисра состояния соединены с соответству вующиьи информационными входами второго мультиплексора, первый и второй выходы регистра состояния являются первым и вторым выходами состояния устройства, выходы третьей, четвертой, пятой, шестой и седьмой групп регистра микрокоманд соединены соответственно с управляющими входами второго мультиплексора, адресными входами первой и второй групп блока памяти, управляюпщми входами первого и второго сдвигателей, второй, восьмой и девятый выходы регистра микрокоманд соединены соответственно с управляющими входами первого мультиплексора, входом управления записью блока синхронизации, первыми входами элемента ШШ и второго элемента И, второй.вход блока синхронизации является входом синхронизации устройства первый, второй, третий, четвертый, Пятый шестой выходы блока синхронизации соединены соответственно с входом синхронизации регистра микрокоманд, вторым входом первого элемен- та И, входом синхронизации регистра состояния, входом синхронизации выходного регистра и триггера, входами обращения и режима блока памяти..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Микропроцессор | 1984 |

|

SU1257657A1 |

| Устройство для контроля блоков памяти | 1988 |

|

SU1569904A1 |

| Контроллер памяти команд | 1988 |

|

SU1617440A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

Изобретение относится к вычислительной технике и предназначено для генерации адресных последовательностей при функциональном контроле оперативных запоминающих устройств. Устройство может быть использовано также для задания тестовых последовательностей при функциональном контроле других цифровых устройств, генерации псевдослучайных чисел с равномерным законом распределения. Цель изобретения - расширение области применения за счет генерации произвольных тестовых последовательностей. Устройство содержит регистр 1 микрокоманд, арифметико-логический блок 2, регистр 3, первый блок 4 сравнения, блок 5 управления, первый мультиплексор 6, блок 7 синхронизации, блок 8 памяти, выходной регистр 9, первый 10 и второй 11 сдвигатели, блок 12 элементов ИЛИ, второй блок 13 сравнения, регистр 14 состояния, второй мультиплексор 15, триггер 16, элемент ИЛИ 17, первый 18 и второй 19 элементы И. 3 ил.

фиг.г

Запись В pezucmp

I

Та к mi

Редактор Г, Гербер

Составитель Ю. Сычев Техред Л-Олийнык

Заказ 6088/52

Тираж 558

ВНЙИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб,, д. 4/5

i - ™.-.------------- ------

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

ToHmi l

Корректор М. Самборская

Подписное

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент ClilA N 4293950, ют | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-10-07—Публикация

1987-04-16—Подача