Изобретение относится к вычислительной технике и может быть использовано для сопряжения разноскоростных источника и приемника информации.

Цель изобретения - повьшениедосто- верности работы устройства путем использования однофазной синхронизации, уменьшения числа контролируемых сиг- :налов при определении состояний заполнения и освобождения накопителя.

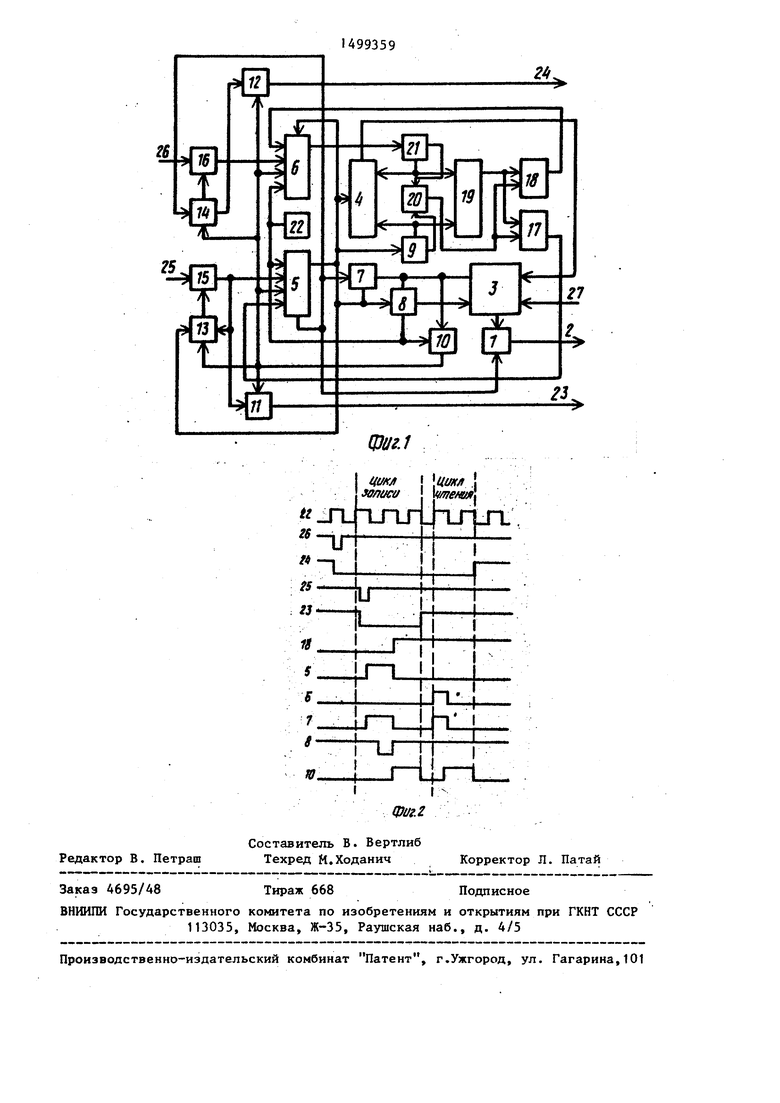

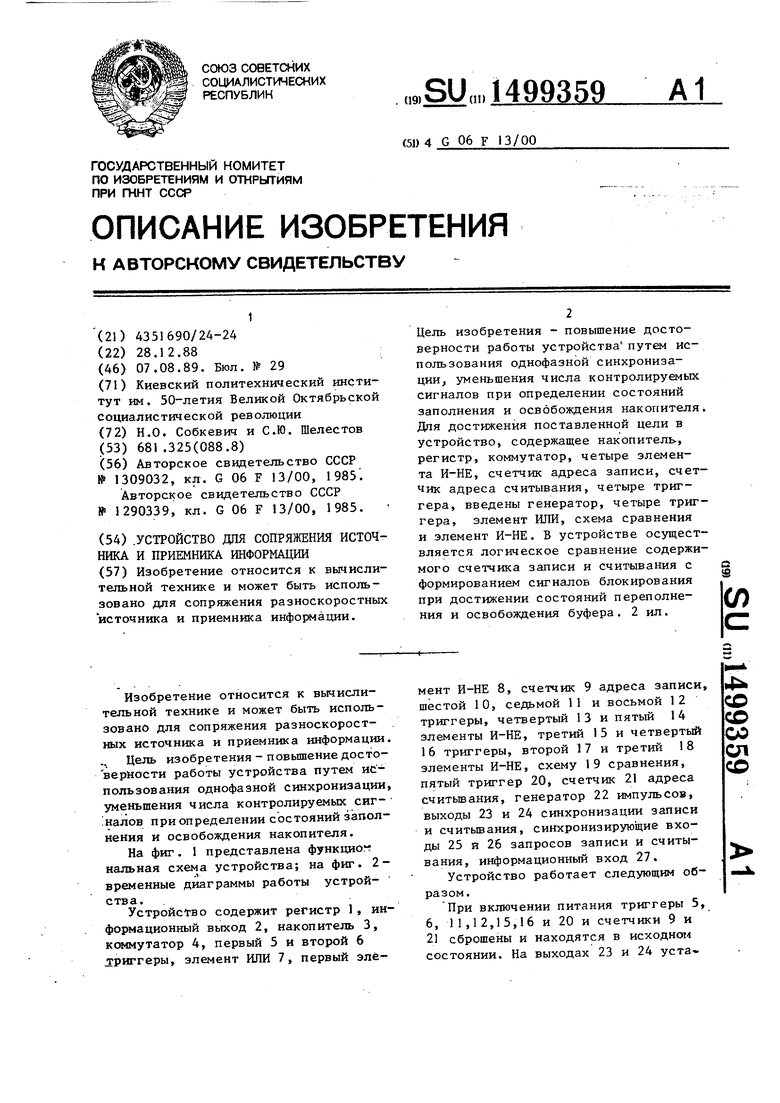

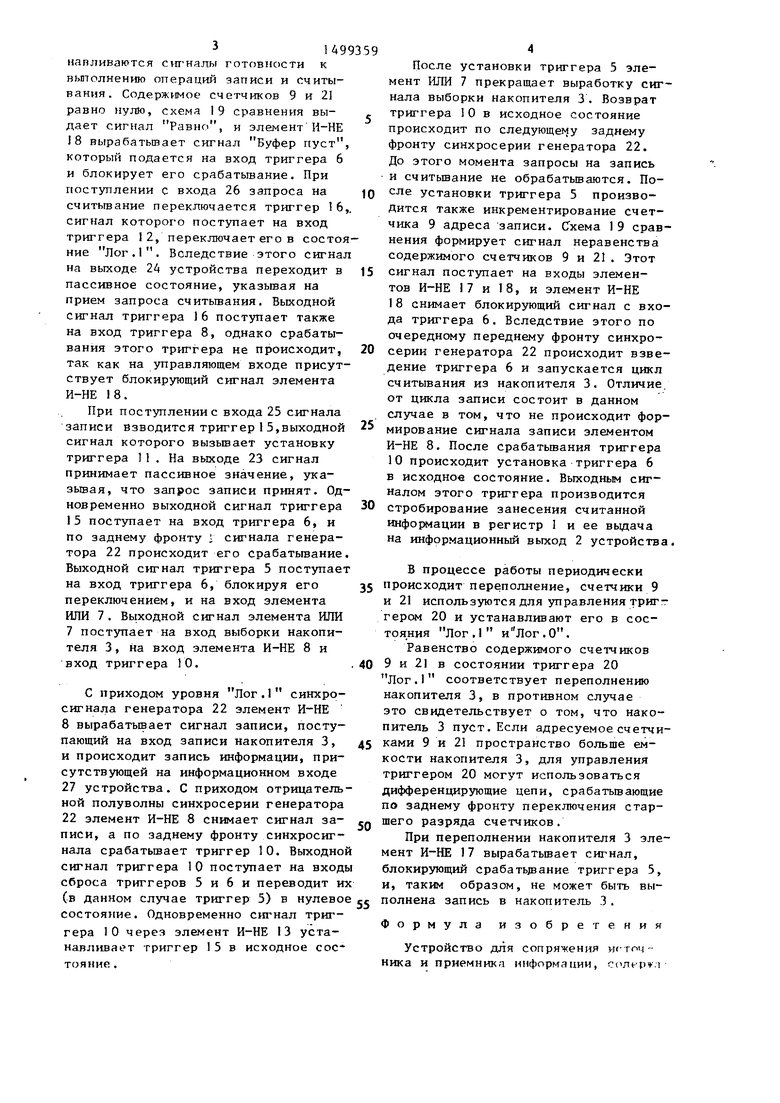

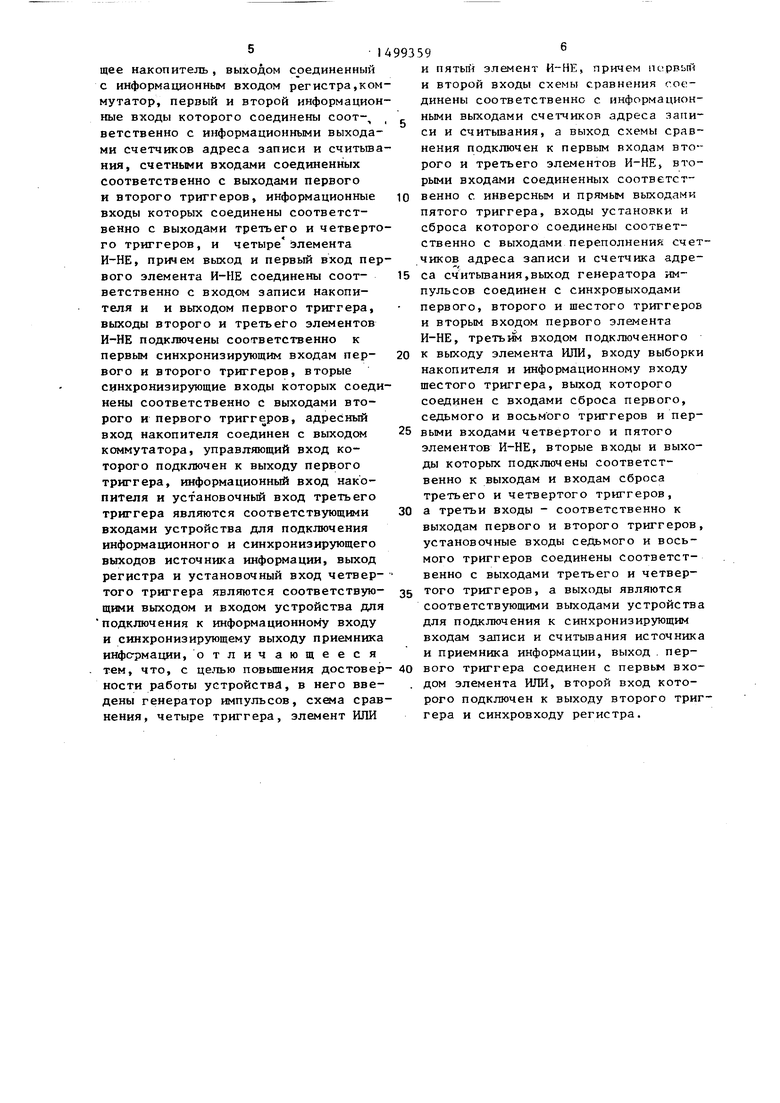

На фиг. 1 представлена функцио г нальная схема устройства; на фиг. 2- временные диаграммы работы устройства.

Устройство содержит регистр 1 , информационный выход 2, накопитель 3, коммутатор 4, первый 5 и второй 6 триггеры, элемент ИЛИ 7, первый элемент И-НЕ 8, счетчик 9 адреса записи, шестой 10, седьмой 11 и восьмой 12 триггеры, четвертый 13 и пятый 14 элементы И-НЕ, третий 15 и четвертый 16 триггеры, второй 17 и третий 18 элементы И-НЕ, схему 19 сравнения, пятый триггер 20, счетчик 21 адреса считьшания, генератор 22 импульсов, выходы 23 и 24 синхронизации записи и считьшания, синхронизирующие входы 25 и 26 запросов записи и считывания, информационный вход 27.

Устройство работает следующим образом.

При включении питания триггеры 5, 6, 11,12,15,16 и 20 и счетчики 9 и 21 сброшены и находятся в исходном состоянии. На выходах 23 и 24 уста

СО

СдЭ

ел

31499

напливаются с ст-налы готовности к

вьтолнению операций записи и считывания. Содержимое счетчиков 9 и 21 равно нулю, Схема 19 сравнения вы- дает сигнал Равно, и элемент И-НЕ 18 вырабатьшает сигнал Буфер пуст, который подается на вход триггера 6 и блокирует его срабатьшание. При поступлении с входа 26 запроса на считывание переключается триггер 16,. сигнал которого поступает на вход триггера I2, переключает его в состояние Лог.1. Вследствие этого сигнал на выходе 24 устройства переходит в пассивное состояние, указьшая на прием запроса считьшания. Выходной сигнал триггера 16 поступает также на вход триггера 8, однако срабатывания этого триггера не происходит, так как на управляющем входе присутствует блокирующий сигнал элемента И-НЕ 18,

При поступлении с входа 25 сигнала записи взводится триггер 1 5,выходной сигнал которого вызывает установку триггера 11, На выходе 23 сигнал принимает пассивное значение, указьшая, что запрос записи принят. Одновременно выходной сигнал триггера 15 поступает на вход триггера 6, и по заднему фронту i сигнала генератора 22 происходит его срабатьшание. Выходной сигнал триггера 5 поступает на вход триггера 6, блокируя его переключением, и на вход элемента ИЛИ 7. Вцходной сигнал элемента ИЛИ 7 поступает на вход выборки накопителя 3, на вход элемента И-НЕ 8 и вход триггера 10.

С приходом уровня Лог.Г синхросигнала генератора 22 элемент И-НЕ 8 вырабатывает сигнал записи, поступающий на вход записи накопителя 3, и происходит запись информации, присутствующей на информационном входе 27 устройства. С приходом отрицательной полуволны синхросерии генератора 22 элемент И-НЕ 8 снимает сигнал записи, а по заднему фронту синхросигнала срабатьшает триггер 10. Выходной сигнал триггера 10 поступает на входы сброса триггеров 5 и 6 и переводит их (в данном случае триггер 5) в нулевое состояние. Одновременно сигнал триггера 10 через элемент И-НЕ 13 устанавливает триггер 15 в исходное сос тояние.

Q 0

5 0 5 0

5

0

После установки триггера 5 элемент ИЛИ 7 прекращает выработку сигнала выборки накопителя 3. Возврат триггера 10 в исходное состояние происходит по следующему заднему фронту синхросерии генератора 22. До этого момента запросы на запись и считьшание не обрабатьшаются. После установки триггера 5 производится также инкрементирование счетчика 9 адреса записи. Схема 19 сравнения формирует сигнал неравенства содержимого счетчиков 9 и 21. Этот сигнал поступает на входы элементов И-НЕ 17 и 18, и элемент И-НЕ 18 снимает блокирующий сигнал с входа триггера 6. Вследствие этого по очередному переднему фронту синхросерии генератора 22 происходит взведение триггера 6 и запускается цикл считывания из накопителя 3. Отличие, от цикла записи состоит в данном случае в том, что не происходит формирование сигнала записи элементом И-НЕ 8. После срабатьюания триггера 10 происходит установка триггера 6 в исходное состояние. Выходным сигналом этого триггера производится стробирование занесения считанной информации в регистр 1 и ее выдача на информационный выход 2 устройства.

В процессе работы периодически происходит переполнение, счетчики 9 и 21 используются для управления тркгт

герсм 20 и устанавливают его в состояния Лог.Г и Лог.О.

Равенство содержимого счетчиков 9 и 21 в состоянии триггера 20 Лог.1 соответствует переполнению накопителя 3, в противном случае это свидетельствует о том, что накопитель 3 пуст.Если адресуемое счетчиками 9 и 21 пространство больше емкости накопителя 3, для управления триггером 20 могут использоваться дифференцирующие цепи, срабатьгоающие по заднему фронту переключения старшего разряда счетчиков.

При переполнении накопителя 3 элемент И-НЕ 17 вырабатьшает сигнал, блокирующий срабатьдаание триггера 5, и, таким образом, не может быть выполнена запись в накопитель 3 .

Формула изобретения

Устройство для сопряжения vicroq- ника и приемника информации, солеч .

ь1

щее накопитель, выходом соединенный с информационным входом регистра,коммутатор, первый и второй информационные входы которого соединены соот-, ветственно с информационными выходами счетчиков адреса записи и считьша ния, счетными входами соединенных соответственно с выходами первого и второго триггеров, информационные входы которых соединены соответственно с выходами третьего и четвертого триггеров, и четыре Элемента И-НЕ, причем выход и первый вход первого элемента И-НЕ соединены соот- ветственно с входом записи накопителя и и выходом первого триггера, выходы второго и третьего элементов И-НЕ подключены соответственно к первым синхронизирующим входам пер- вого и второго триггеров, вторые синхронизирующие входы которых соединены соответственно с выходами второго и первого триггеров, адресный вход накопителя соединен с выходом коммутатора, управляющий вход которого подключен к выходу первого триггера, информационный вход накопителя и установочный вход третьего триггера являются соответствующими входами устройства для подключения информационного и синхронизирующего выходов источника информации, выход регистра и установочный вход четвер- того триггера являются соответствую- щими выходом и входом устройства для подключения к информационному входу и синхронизирующему выходу приемника инфс-рмации, отличающееся тем, что, с целью повьшения достовер ности работы устройства, в него введены генератор импульсов, схема сравнения, четыре триггера, элемент ИЛИ

59

и пятый элемент И-НЕ, причем псрвьй и второй входы схемы сравнения соединены соответственно с информационными выходами счетчикор адреса записи и считьшания, а выход схемы сравнения подключен к первым входам второго и третьего элементов И-НЕ, вторыми входами соединенных соответственно с инверсным и прямым выходами пятого триггера, входы установки и сброса которого соединены соответственно с выходами переполнения счетчиков адреса записи и счетчика адреса считьшания,выход генератора импульсов соединен с синхрояыходами первого, второго и шестого триггеров и вторым входом первого элемента И-НЕ, третьим входом подключенного к выходу элемента ИЛИ, входу выборки накопителя и информационному входу щестого триггера, выход которого соединен с входами сброса первого, седьмого и восьмого триггеров и первыми входами четвертого и пятого элементов И-НЕ, вторые входы и выходы которых подключены соответственно к выходам и входам сброса третьего и четвертого триггеров, а третьи входы - соответственно к выходам первого и второго триггеров, установочные входы седьмого и восьмого триггеров соединены соответственно с выходами третьего и четвертого триггеров, а выходы являются соответствующими выходами устройства для подключения к синхронизирующим входам записи и считывания источника и приемника информации, выход . первого триггера соединен с первьм входом элемента ИЛИ, второй вход которого подключен к выходу второго триггера и синхровходу регистра.

лг/ге/су

Пги1

цикл I

/fft/tfVt

2,

г/ге/су

ЦЗиг.1

цикл I UiM/f

/fft/tfVt иггшлил,

«revesf

rLTLTL

фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения | 1979 |

|

SU857967A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249591A1 |

| Устройство ранжирования чисел | 1987 |

|

SU1425653A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1987 |

|

SU1453397A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1222098A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Устройство для сопряжения | 1983 |

|

SU1176337A1 |

| Устройство для обмена данными между оперативной памятью и внешним устройством | 1984 |

|

SU1180908A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения разноскоростных источника и приемника информации. Цель изобретения - повышение достоверности работы устройства путем использования однофазной синхронизации, уменьшения числа контролируемых сигналов при определении состояний заполнения и освобождения накопителя. Для достижения поставленной цели в устройство, содержащее накопитель, регистр, коммутатор, четыре элемента И-НЕ, счетчик адреса записи, счетчик адреса считывания, четыре триггера, введены генератор, четыре триггера, элемент ИЛИ, схема сравнения и элемент И-НЕ. В устройстве осуществляется логическое сравнение содержимого счетчика записи и считывания с формированием сигналов блокирования при достижении состояний переполнения и освобождения буфера. 2 ил.

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1290339A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-07—Публикация

1988-12-28—Подача