Изобретение относится к вычислительной технике и может быть использовано в мультипроцессорных вычислительных системах.

Цель изобретения - расширение области применения устройства за счет одновременного обслуживания до М запросов (М - число каналов выдачи команд) с различными приоритетами.

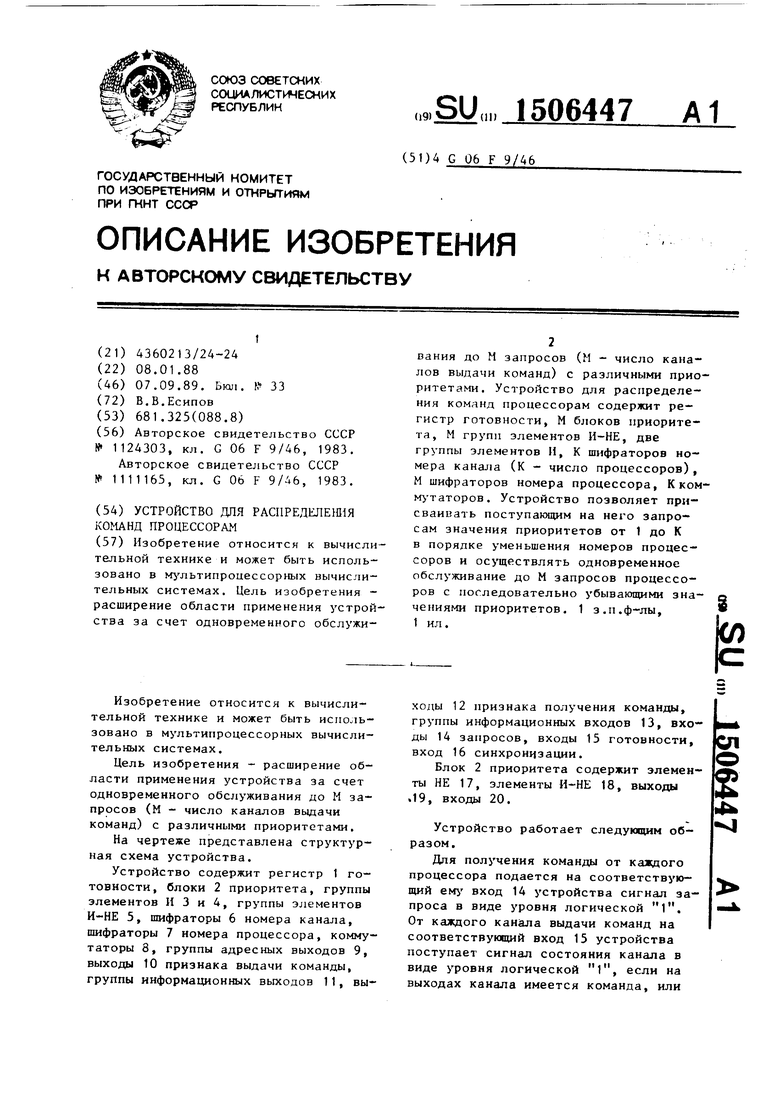

На чертеже представлена структурная схема устройства.

Устройство содержит регистр 1 готовности, блоки 2 приоритета, группы элементов И 3 и 4, группы элементов И-НЕ 5, шифраторы 6 номера канала, шифраторы 7 номера процессора, коммутаторы 8, группы адресных выходов 9, выходы 10 признака выдачи команды, группы информационных выходов 11, выходы 12 признака получения команды, группы информационных входов 13, входы 14 запросов, входы 15 готовности, вход 16 синхронизации.

Блок 2 приоритета содержит элементы НЕ 17, элементы И-НЕ 18, выходы .19, входы 20.

Устройство работает следующим образом.

Дпя получения команды от каждого процессора подается на соответствующий ему вход 14 устройства сигнал запроса в виде уровня логической 1. От каждого канала выдачи команд на соответствующий вход 13 устройства поступает сигнал состояния канала в виде уровня логической 1, если на выходах канала имеется команда, или

сд

о

| Kj

логического О, если команда отсутствует ,

Положительным фронтом импульса синхронизации, поступающего на вход 16 устройства, производится запись сигналов запросов процессоров и сигналов состояний каналов на регистр 1 готовности. С выходов данного регистра сигналы запросов поступают на вторые входы соответств тощих элементов И-НЕ 5 каждой группы, а сигналы состояний каналов поступают на первые входы каждого элемента И-НЕ 5 соответствующих групп.

Инвертированные сигналы запросов появляются на выходах только тах элементов И-НЕ 5 какой-либо группы, у которых на первые входы и выходы.

запросов только одни,принадлежащий процессору с наименьим номером, появляется на соответствующем его выходе 19.

С данного выхода 19 .блока приоритета инвертирозанный сигнал запроса поступает на подключенные к нему вход шифратора 6 номера канала, вход шифратора 7 номера процессора, вход элемента И 3 первой группы, вход элемента И 4 второй группы и входа элементов И-}1Ь 5 всех остш1ьных групп с большими, чем у рассматриваемой группы, номерами. Поступая на входы элементов И-НЕ 5, сигнал блокирует прохождение через них сигнала запроса от того же процессора и обеспечивает тем самым однозначное соответст

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для приоритетного обращения к памяти | 1985 |

|

SU1283766A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Устройство для обслуживания групповых приоритетных запросов | 1990 |

|

SU1753473A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Многоканальное устройство управления вводом информации в микроЭВМ | 1984 |

|

SU1234844A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

Изобретение относится к вычислительной технике и может быть использовано в мультипроцессорных вычислительных системах. Цель изобретения - расширение области применения устройства за счет одновременного обслуживания до М запросов (М - число каналов выдачи команд) с различными приоритетами. Устройство для распределения команд процессорам содержит регистр готовности, М блоков приоритета, М групп элементов И-НЕ, две группы элементов И, К шифраторов номера канала (К - число процессоров), М шифраторов номера процессора, К коммутаторов. Устройство позволяет присваивать поступающим на него запросам значения приоритетов от 1 до К в порядке уменьшения номеров процессоров и осуществлять одновременное обслуживание до М запросов процессоров с последовательно убывающими значениями приоритетов. 1 з.п. ф-лы, 1 ил.

подключенные к выходам блоков 2 прио-;)Q вие между каналом, выдаюшлм команду, ритета с меньшими, чем у рассматрии прини(й)щим ее процессором. Пройдя шифратор 6 номера канала и шифратор 7 номера процессора, инвертированный сигнал запроса появляется на их выхо дах соответственно в виде кода номера канала и в виде кода номера процессора. Поступая на входы указанных вь:ше элементов И, инвертированный сигнал запроса всегда появляется

ваемой группы, номерами, поступают сигналы в виде уровня логической 1 Это имеет место только при условии наличия команды на выходах канала.

соответствующего рассматриваемой группе, и отсутствия удовлетворения запросов соответствующих данным элементам И-НЕ 5 процессоров каналами с

меньшими, чем у рассматриваемой iруп- jg на их выходах.

пы номерами.

1С выходов элементов И-НЕ 5 инвертированные сигналы запросов поступают на подключенные к ним входы 20 блока

2приоритета и приходят далее на соединенные с ними входы элементов НЕ 17 за исключением инвертированного сигнала запроса 1-го процессора, и входы элементов И-НЕ 18, за исключением инвертированного сигнала запроса п-го процессора.

Поступив на входы элементов И-НЕ 18, инвертированньй сигнал запроса какого-либо процессора блокирует прохождение через них сигналов запросов всех остальных процессоров с большими, чем у рассматриваемого процессора, номерами, которые поступают с выходов элементов НЕ 17 на подключенные к ним первые входы данных элементов И-НЕ 18. Сигнал запроса 1-го процессора никогда не блокируется и поступает инвертированным на 1-й выход 19 блока приоритета не с выхода элемента И-НЕ 18, как сигналы запросов остальных процессоров, а непосредственно с 1-го входа 20. Поэтому из всех поступивших на входы 20 блока приоритета инвертг.рованных сигналов

вие между каналом, выдаюшлм команду,

и прини(й)щим ее процессором. Пройдя шифратор 6 номера канала и шифратор 7 номера процессора, инвертированный сигнал запроса появляется на их выходах соответственно в виде кода номера канала и в виде кода номера процессора. Поступая на входы указанных вь:ше элементов И, инвертированный сигнал запроса всегда появляется

С выхода элемента И 4 второй группы инвертированный сигнал запроса поступает на подключенный к выход 10 признака выдачи команды устройства, а код номера процессора с выходов шифратора 7 номера процессора приходит на соединенные с ним адресные выходы 9 соответствующей каналу группы устройства.

С выхода элемента И 3 первой группы инвертированный сигнал запроса поступает на подключенный к нему выход 12 признака получения команды устройства, а код номера канала с выходов шифратора 6 номера канала приходит на соединенные с ними адресные входы коммутатора 8, переключая его на прием команды с выходов соответствующего рассматриваемой группе элементов И-НЕ 5 канала. Данная команда поступает на информационные входы 13 соответствующей каналу группы устройства и подключенные к ним информационные входы указанного выше комьгу- татора 8. Далее команда проходит через этот комг татор и появляется на его выходах и связанных с ними информационных вЕ 1ходах 11 соответствующей процессору группы устройствя

С данной группы информацноннь х выходов 11 устройства команда поступает на соединенные с ними входы процессора и записывается на его регист при получении процессором сигнала в виде уровня логического О с выхода 12 устройства. Этот сигнал вызывает также сброс текущего, утче удовлетворенного запроса процессора к моменту прихода следующего импульса синхронизации на вход 16 устройства.

Код номера процессора, получившего команду, который поступает с адресных выходов 9 рассматриваемой группы устройства, используется при приеме результата выполнения команды от данного процессора.

Формула изобретения 20

канала, m шифраторов номера процессора, п KOMbfyraTopoB, причем i-ft вход j-ro блока приоритета (,2,...,п; ,2,...,m) подключен к выходу i-ro элемента И-НЕ j-й группы, первый вход которого соединен с выходом (n-t-j)-ro разряда регистра готовности, второй вход i-го элемента Н-НЕ j-й группы подключен к выходу i-ro разряда регистра готовности, J-1 оставшихся входов i-ro элемента И-НЕ j-й группы подключены к i-м выходам соответственно 1-го, 2-го, ..., (j-l)-ro бло- -я приоритета, i-й выход j-oro блока

0

5

0

5

0

5

0

5

приоритета соединен с J-M входо м 1-го шифратора номера канала, j-M входом i-fo элемента И первой группы, i-м входом j-ro элемента Н второй группы и i-M входом j-ro шифратора номера процессора, выходы которого подключены к одноименным адресным выходам j--й группы устройства, выход j-ro элемента И второй группы соединен с j-M выходом признака выдачи команды устройства, выходы i-ro шифратора номера канала подключены к одноименным адресным входам i-ro комм татора, выходы которого соединены с одноименными информационными выходами i-й группы устройства, выход i-ro элемента И первой группы подключен к i-му выходу признака получения команды устройства, информационные входы j-й группы i-ro коммутатора соединены с одноименными информагщонными входами j-й группы устройства, информационные входы 1-го, 2-го,...,п-го разрядов регистра готовности подключены к соответствующим входам запросов устройства, информационные входы (n-t-l)-ro, (п+2)-го, . . . , ()-го разрядов регистра готовности подклк ч8ны к соответствующим входам готовности устройства, вход синхронизации регистра готовности подключен к входу синхронизации устройства.

li

П Q/J г QJ f2

//

11

П

l:i

:i

:й

I

9 rff 9 TO 9 re

| Многоканальное устройство для управления очередностью в системе обмена информацией | 1983 |

|

SU1124303A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1111165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-07—Публикация

1988-01-08—Подача