112

Изобретение относится к вьгчиспи- тельной технике и может быть использовано в 1чультнпроцессорных вычислительных системах для разрешения конфликтов при одновременном обращении нескольких процессоров или каналов к общей модульной памяти.

Цель изобретения - расширение области применения устройства путем обеспечения одновременного обслуживания нескольких запросов.

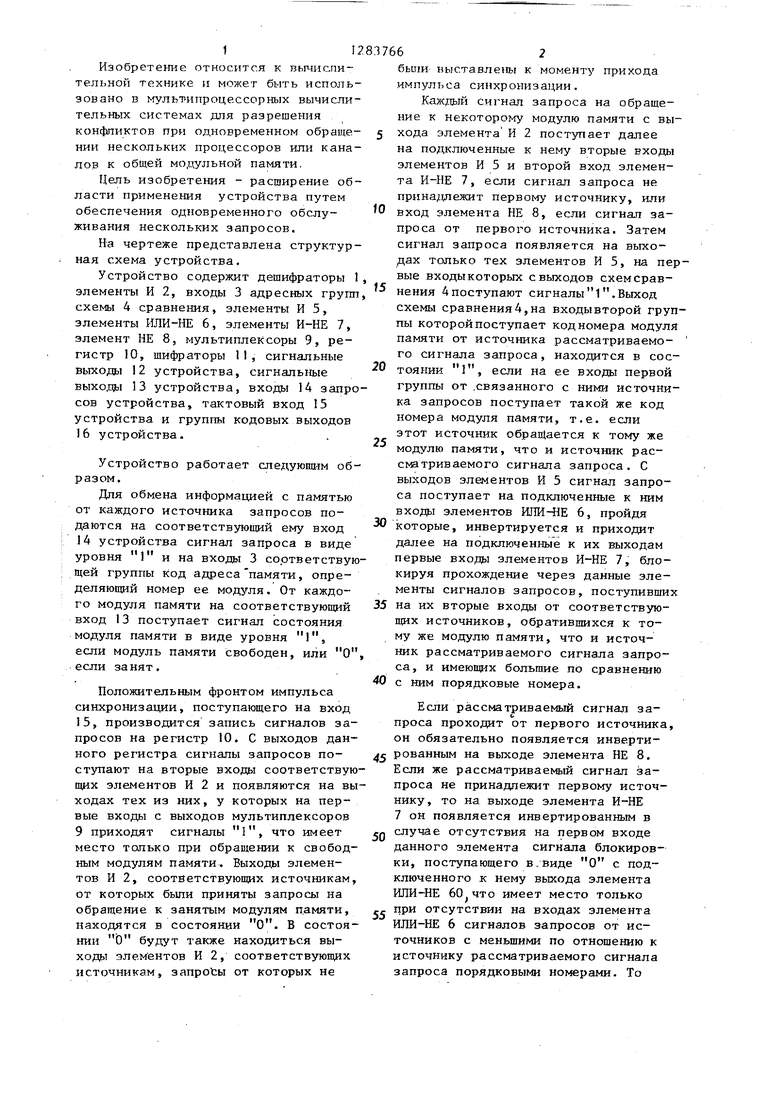

Н-а чертеже представлена структурная схема устройства.

Устройство содержит дешифраторы 1 элементы И 2, входы 3 адресных групп схемы 4 сравнения, элементы И 5, элементы ИЛИ-НЕ 6, элементы И-НЕ 7, элемент НЕ 8, мультиплексоры 9, регистр 10, шифраторы II, сигнальные выходы 12 устройства, сигнальные выхо,гды 13 устройства, входы 14 запросов устройства, тактовый вход 15 устройства и группы кодовых выходов 16 устройства.

Устройство работает следующим образом.

Для обмена информацией с памятью от каждого источника запросов подаются на соответствующий ему вход 14 устройства сигнал запроса в виде уровня 1 и на входы 3 соответствующей группы код адреса памяти, определяющий номер ее модуля. От каждого модуля памяти на соответствующий вход 13 поступает сигнал состояния модуля памяти в виде уровня 1, если модуль памяти свободен, или О если занят.

Положительным фронтом импульса синхронизации, поступающего на вход 15, производится запись сигналов запросов на регистр 10. С выходов данного регистра сигналы запросов поступают на вторые входы соответствующих элементов И 2 и появляются на выходах тех из них, у которых на первые входы с выходов мультиплексоров 9 приходят сигналы 1, что имеет место только при обращении к свободным модулям памяти. Выходы элементов И 2, соответствующих источникам, от которых были приняты запросы на обращение к занятым модулям памяти, находятся в состоянии О. В состоянии О будут также находиться выхода элементов И 2, соответствующих источникам, запроЬы от которых не

62

были выставлены к моменту прихода импульса синхронизации.

Каждый си1 нал запроса на обращение к некоторому модулю памяти с выхода элемента И 2 поступает далее на подключенные к нему вторые входы элементов И 5 и второй вход элемента И-НЕ 7, если сигнал запроса не принадлежит первому источнику, или

вход элемента НЕ 8, если сигнал запроса от первого источника. Затем сигнал запроса появляется на выходах только тех элементов И 5, на первые входыкоторых с выходов схемсравнения 4поступают сигналы.Выход схемы сравнения4,на входывторой группы которойпоступает кодномера модуля памяти от источника рассматриваемого сигнала запроса, находится в состоянии 1, если на ее входы первой группы от .связанного с ними источника запросов поступает такой же код номера модуля памяти, т.е. если этот источник обрап1ается к тому же модулю памяти, что и источник рассматриваемого сигнала запроса. С выходов элементов И 5 сигнал запроса поступает на подключенные к ним входы элементов ИЛИ-НЕ 6, пройдя которые, инвертируется и приходит далее на подключенные к их выходам первые входы элементов И-НЕ 7, блокируя прохождение через данные элементы сигналов запросов, поступивших

на их вторые входы от соответствующих источников, обратившихся к тому же модулю памяти, что и источник рассматриваемого сигнала запроса , и имеющих большие по сравнению

с ним порядковые номера.

Если рассматриваемый сигнал запроса проходит от первого источника, он обязательно появляется инвертированным на выходе элемента НЕ 8, Если же рассматриваемый сигнал запроса не принадпежит первому источнику, то на выходе элемента И-НЕ 7 он появляется инвертированным в

случае отсутствия на первом входе данного элемента сигнала блокировки, поступающего в.виде О с подключенного к нему выхода элемента

55

ЕПИ-НЕ 60 что имеет место только при отсутствии на входах элемента ИЛИ-НЕ 6 сигналов запросов от источников с меньшими по отношению к источнику рассматриваемого сигнала запроса порядковыми номерами. То

есть если на одаи из источ}шков с MeHbiiiHNfH порядкрвЕ 1ми номерами не обращается к тому же модулю памяти, что и источник рассматриваемого сигнала запроса.

С выхода элемента НЕ 8 при поступлении от первого источника или с выходов элементов 7 при поступлении от остальных источников инвертированные сигналы запросов прихо- дят далее на соответствующие выходы 12 и соединенные с ними входы разрешения дешифраторов, появляясь затем на их выходах, которые определяются кодами номеров модулей памяти, посту пающими на информационные входь дешифраторов. С выходов дешифраторов инвертированные слгналы запросов поступают на подключенные к ним входы шифраторов, появляясь на их выхо- дах в виде кодов номеров источников запросов. Далее кодь номеров источников запросов с информационных выходов шифраторов приходят на соединенные с ними выходы

16 устройства.

С выходов 12 устройства инверти- рованнь1е сигналы запросов после прекращения переходных процессов по- даются на соответствующие источники, вызывая в них сброс текувщх принятых на обслуживание запросов и выставление в случае необходимости

новых запросов к моменту прихода сле- 35 элемента И j-ro канала, второй вход

дующего импульса синхронизации на вход 15 устройства. Коды с выходов 16 устройства после прекращения переходных процессов подаются на соответствующие модули памяти, вызывая в них прием от источников запросов необходимой для обслуживания информации, включение режимов обслуживания и выставление.сигналов состояния в виде уровней О.

Формула изобретения

Многоканальное устройство для приоритетного обраще1шя к памяти, содержащее регистр, в каждом канале первый элемент И и дешифратор, в каждом 1-м канале ( п число источников запросов) группу из (1-1) элементов И, причем группа информационных входов регистра является группой запросных входов устг

10-15 20 25

30

283766

ройства,

о т л и ч а ю П1 е е

с я

тем, что, с цепью расширения области применения устройства путем обеспечения возможности одновременного обслуживания нескольких запросов, оно содержит в первом канале элемент НЕ, шифратор и мультиплексор, а в каждом i-M канале (, ..., п) элемент ШШ-НЕ, элемент И-НЕ, мультиплексор и группу из (i-1) схем сравнения,, причем выходы шифраторов являются группами кодовых выходов устройства, выход элемента НЕ первого канала и выходы элементов И-НЕ остальных каналов, являются сигнальными выходами устройства, группа информационных выходов мультиплексора каждого канала соединена с группой сигнальных вхо- дов устройства, тактовьй вход которого соединен с тактовым входом регистра, выход мультиплексора канала соединен с первым входом элемента И своего канала, каждая группа кодовых входов устройства соединена с группой управляющих входов мультиплексора, группой входов дешифратора и первыми группами входов схем сравнения группы одноименного канала, вторая группа входов j-й схемы сравнения группы (, .., п) i-ro канала (, ..., п) соединена с j-й группой кодовых входов устройства, первые входи j-x элементов И группы в каждом канале соединены с выходом

0

5

0

каждого элемента И группы канала соединен с выходом одноименной схемы сравнения группы своего канала, второй вход элемента И j-ro канала соединен с j-м выходом регистра, выход элемента И первого канала через элемент НЕ первого канала соединен с управляющим входом дешифратора своего канала, выход элемента И каждого канала, начиная со второго, соединен с первым входом элемента И-НЕ своего канала, выходы элементов И-НЕ каналов, начиная с второго, соединены с управляюш ми входами дешифраторов своих каналов, второй вход элемента И-НЕ каждого канала соединен с выходом элемента ИЛИ-НЕ своего канала, входы элементов ИЛИ- НЕ каналов со.единены с выходами элементов И своих каналов, j-е выходы дешифраторов соединены с входами шифратора j-ro канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения команд процессорам | 1988 |

|

SU1506447A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для выбора запросов по приоритетам | 1985 |

|

SU1307458A1 |

Изобретение относится к, области вычислительной техники и может быть использовано при построении мультипроцессорных вычислительных систем. Цель изобретения - расширение области применения устройства за счет возможности одновременного обслуживания нескольких запросов, для чего необходимо увеличить количество одновременно обслуживаемых запросов, а также взаимодействующих с помощью устройства источников запросов и модулей памяти, между которыми осуществляется обмен информацией. С этой целью устройство содержит регистр запросов, куда принимаются запросы от m источников на обмен с п модулями памяти, указывающие заняты они или свободны, схемы сравнения, осуществляющие сравнение кодов номеров модулей памяти, к -которйм обращаются источники, шифраторы, на входы которых поступают принятые на обслуживание запросы, а с выходов снимаются коды номеров их источников. Поступающим запросам присваиваются значения приоритетов от 1 до тп в порядке уменьшения, номеров их источников. Запрос к модулю памяти принимается на обслуживание, -если модуль памяти свободен и код его номера не совпадает ни с одним из кодов номеров модулей памяти, соответствующих запросам с большими, чем с рассматриваемого запроса, значениями приоритетов. То есть осуществляется одновременное обслуживание запросов с различными приоритетами к разным и свободным модулям памяти и обслуживание запросов к одному и тому же модулю памяти в порядке убывания значений, их приоритетов. 1 ил. с $ (Л

Составитель М .Кудряшев Редактор Л .Пчолинская Техред Л.ОлейникКорректор С .Черни

Заказ 7443/48Тираж 670-Подписное

ВНИИШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство приоритета | 1979 |

|

SU840905A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1987-01-15—Публикация

1985-04-29—Подача