Изобретение относится к автоматике и вычислительной технике и может использоваться для поиска неисправностей в цифровых устройствах.

Цель изобретения - повышение глубины регистрации.

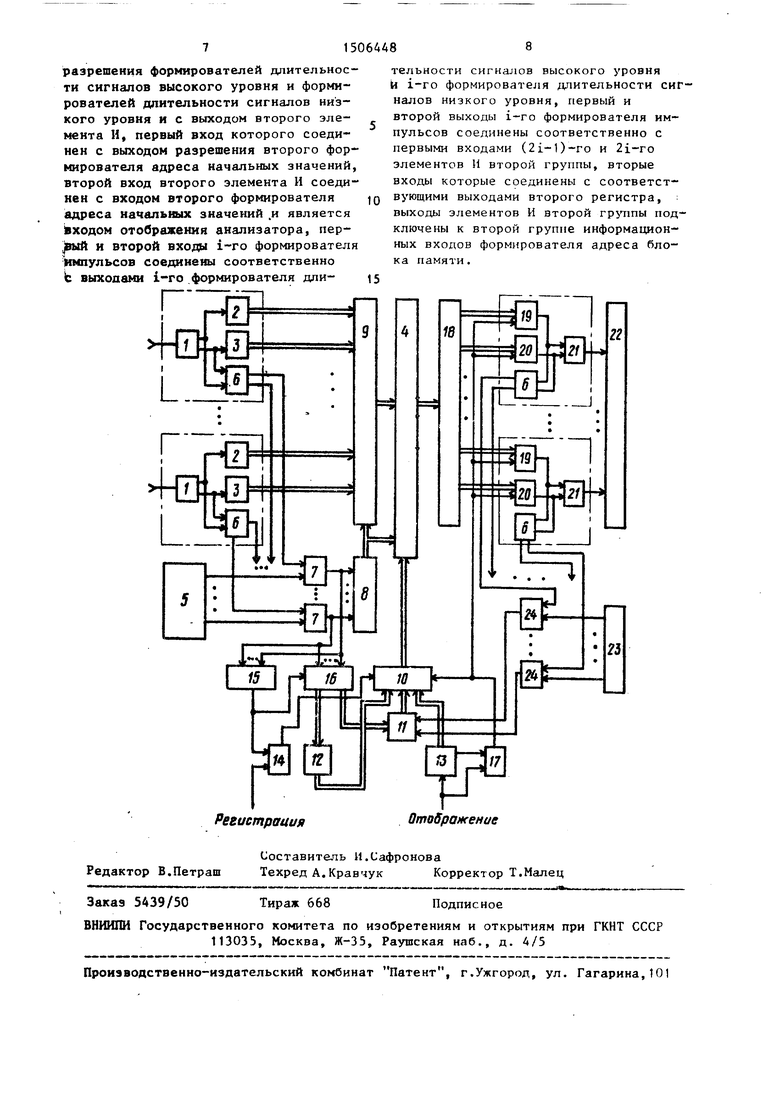

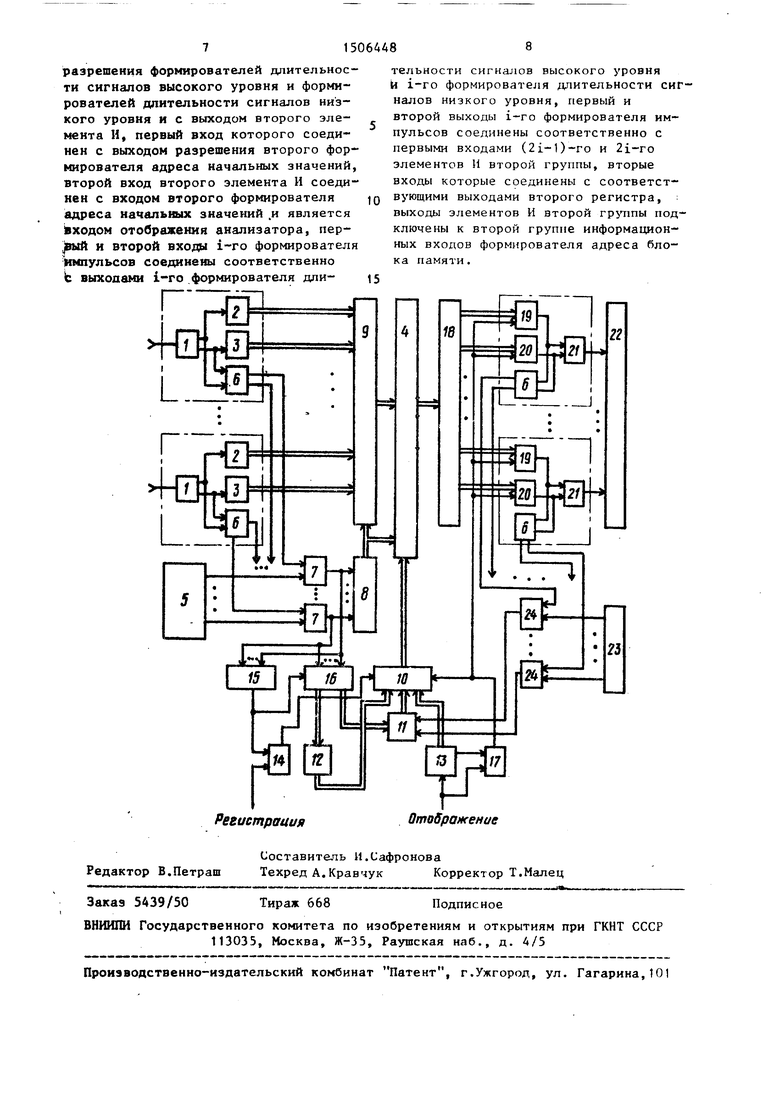

На чертеже представлена функциональная схема логического анализатора.

Анализатор содержит группу формирователей 1 признака входного сигнала, группу измерителей 2 длительности сигнала высокого уровня, группу измерителей 3 длительности сигнала низкого уровня, блок 4 памяти, первый регистр 5, первую группу формирователей 6 импульсов, первую группу элементов И 7, шифратор 8, мультиплексор 9, коммутатор 10, формирователь 11 адреса блока памяти, первый 12 и второй 13 формирователи адреса начальных значений, первый элемент И

14, блок 15 выбора формирователя адреса, коммутатор 16, второй элемент И 17, демультиплексор 18, группу формирователей 19 длительности сигнала высокого уровня, группу формировате- i лей 20 длительности сигнала низкого уровня, вторую группу формирователей 21 импульсов, блока 22 отображения, второй регистр 23 и вторую группу элементов И 24.

Логический анализатор работает в двух режимах: регистрации и отображения.

В режиме регистрации последовательности двоичных сигналов с N выходов объекта контроля поступают через входы логического анализатора на со- ответстБую1дие N формирователей 1 признака входного сигнала, два выхода которых являются разрешакнцими для соответствующего измерителя 2 длительности сигнала высокого уровня и измеСП

о

00

3150

ригеля 3 длительности сигнала низкого уровня. Причем сигнал разрешения измерения длительности сигнала другого уровня свидетельствует о необходимое- ти записи уже сформировавшегося значения длительности сигнала предыдущего уровня в блок памяти. Поскольку несколько измерителей 2 и 3 могут одновременно закончить измерения, то для динамической записи в блок памяти сформированных длительностей уровней сигналов происходит последовательный опрос первым регистром 5 обоих выходов всех N формирователей 1 признака входных сигналов, длительность сигналов которых предварительно уменьшена соответствующими формирователями 6 импульсов первой группы до времени f цикла одного опроса первого регист- ра 5. Это время определяется минимальной длительностью входного сигнала, значение которого может зарегис - рировать устройство.

Первый регистр 5 обеспечивает по- следовательное наличие сигнала высокого уровня на всех выходах, тем самым разрешая прохождение сигналов с формирователей 6 импульсов первой группы за время C/2N через элементы И 7 первой группы на шифратор 8 единичного позиционного кода в двоичный, формирующий адрес соответствующего измерителя 2 или 3 длительности сигнала. По этому адресу мультиплексор 9 коммутирует выходы необходимого измерителя 2 или 3 длительности сигнала с соответствующими входами блока 4 памяти, и значение измерителя 2 или 3 совместно с его адресом записывается в блок памяти по адресу, скоммугиро- ванному вторым комкутатором 10 с фор- ь ирователя 11 адреса блока памяти или с первого формирователя 12 адреса начальных значений в режиме регистра- дни и с формирователя 11 адреса блока памяти или второго формирователя 13 адреса начальных значений в режиме отображения. Управляющим входом второго коммутатора 10 является выход первого элемента И 14, разрешающего поступление сигнала с блока 15 выбора формирователя адреса при наличии входного управляющего сигнала устройства Регистрация. В блоке 15 выбора формирователя адреса происходит анализ Сигналов, поступающих с пер- вой группы элементов И для выделения первых сигналов, поступающих на каж

, 5 0

5 30 с 0 .с

0

дый информационный вход логического анализатора. При отсутствии такого сигнала первый коммутатор 16 соединяет выходы элементов И 7 первой группы с формирователем 11 адреса блока памяти, а при наличии - с первым формирователем 12 адреса начальных значений. При этом при наличии сигнала высокого уровня на одном из выходов элементов первой группы И 7 происходит увеличение адреса в 11 и 12 на 1.

В режиме отображения при наличии управляющего сигнала Отображение, происходит последовательное изменение значения второго формирователя 13 адреса начальных значений с фиксированной частотой, с которой производится считывание слов из блока памяти. При (N+1)-M увеличении значения второго формирователя 13 адреса начальных значений этот сигнал поступает через второй элемент И 17 на второй управляющий вход второго коммутатора 10, который после этого подключает адресные входы блока памяти к выходам формирователя 11 адреса блока памяти. Считанные по сформированным адресам значения длительностей входных сигналоп поступают через демультиплексор 18 на соответствующий форГ Шрователь длительности сигнала: формирователь 19 длительности сигнала высокого уровня или формирователь 20 длительности сигнала низкого уровня, в которых при наличии разрешающего сигнала с выхода второго элемента И 17 происходит уменьшение записанных в них значений с фиксированной частотой до нуля. В течение этого времени формирователем 21 формируются сигналы необходимого уровня, поступающие на блок 22 отображения. Считывание из блока памяти следующего слова происходит при появлении сигнала равенства нулю на одном из формирователей длительности сигналы поступают на соответствующие формирователи 6 импульсов, в качестве которых могут быть одновибраторы. Поскольку несколько формирователей 19 и 20 длительности сигналов могут одновременно сформировать сигналы, свидетельствующие о необходимости считывания следующего слова из блока памяти, то для разнесения их во времени происходит последовательный опрос выходов формирователей 19 и 20

(длительности выходного сигнала вторы регистром 23, формирующим сигналы аналогично первом регистру 5 и разрешающим прохождение сигналов с выходов формирователей 19 и 20 длительности сигнала через элементы И 24 второй группы на формирователь Т1 адреса.

Таким образом, введенные отличительные признаки позволяют производить динамическую запись значений длительностей входных сигналов в бло памяти, что позволяет увеличить глубину регистрации логического анализатора.

Формула изобретения

Логический анализатор, содержащий блок памяти, формирователь адреса блока памяти, группу из N формирователей признака входного сигнала где N - число информационных входов анализатора, группу из N измерителей длительност« сигналов высокого уровня, группу из N измерителей длительности сигналов низкого уровня, мультиплексор, демультиплексор, группу из N формирователей длительности сигналов высокого уровня, группу из N формирователей длительности сигналов низкого уровня, группу из N формирователей уровня выходных сигналов и блок отображения, причем вход i-ro формирователя признака входного сигнала является i-M информационным входом анализатора (,N), первый и второй выходы i-ro формирователя признака входного сигнала подключены соответственно к входам i-ro измерителя длительности сигналов высокого уровня и i-ro измерителя сигналов низкого уровня, группы выходов кото- рык подключены к соответствующим группам входов мультиплексора, группа выходов которого подключена к первой группе информационных входов блока, памяти, первая и вторая группы выходов которого подключены соответственно к группе информационных входов и группе адресных входов демульти- плексора, группы информационных входов которого соединены с соответствующими группами информационных входов формирователей длительности сигналов высокого уровня и формирователей длительности сигналов низкого уровня, выходы которых соединены с

0

5

5

первыми и вторыми входами соответствующих формирователей уровня выходного сигнала, выходы которых подключены к соответствующим входам блока отображения, отличающийся тем, что, с целью повьппения глубины регистрации, анализатор содержит два 2Ы-разрядных регистра, две группы элементов И, шифратор, два коммутатора, блок выбора формирователя адреса, два формирователя адреса начальных значений, два элемента И и две группы формирователей импульсов, причем первый и второй входы i-ro формирователя импульсов первой группы соединены с первым и вторым выходами i-ro формирователя признака входного сигнала, первый и второй выходы i-ro 0 формирователя импульсов первой группы соединены соответственно с первыми входами (2i-l)-ro и 2i-ro элементов И первой группы, вторые входы которых соединены с соответствующими выходами первого регистра, выходы элементов Н первой группы соединены с группой информационных входов первого коммутатора, с группой входов блока выбора формирователи адреса и с группой входов шифратора, группа выходов которого подключена к группе адресных входов мультиплексора и к второй группе информационных входов блока памяти, вторая группа адресных входов которого соединена с группой выходов второго коммутатора, первая группа информационных входов которого соединена с группой выходов формирователя адреса блока памяти, вторая и третья группы информационных входов второго коммутатора подключены соответственно к группам выходов первого и второго формирователей адреса начальных значений, группа входов первого формирователя адреса начальных значений соединена с первой группой выходов первого коммутатора, вторая группа выходов которого подключена к первой группе информационных входов формирователя адреса блока памяти, управляющий вход первого коммутатора соединен с выходом блока выбора формирователя адреса и с первым входом первого элемента Н, второй вход которого является входом регистрации анализатора, выход первого элемента И соединен с первым управляющим входом второго коммутатора, второй управляющий вход которого соединен с входами

0

5

0

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Устройство для контроля дискретных сигналов | 1987 |

|

SU1499347A1 |

| Логический анализатор | 1989 |

|

SU1734093A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Вычислительное устройство для контроля параметров объекта | 1975 |

|

SU690498A1 |

| Логический анализатор | 1986 |

|

SU1381512A1 |

| ОПТИЧЕСКАЯ ИНФОРМАЦИОННО-ПОИСКОВАЯ СИСТЕМА С ГОЛОГРАФИЧЕСКИМ ТРЕХМЕРНЫМ НАКОПИТЕЛЕМ | 2007 |

|

RU2345413C1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2021 |

|

RU2768543C1 |

| Тестер контроля и диагностики электронных модулей | 1986 |

|

SU1396099A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для поиска неисправностей в цифровых устройствах. Цель - повышение глубины регистрации. Для достижения цели в анализатор введены два 2N - разрядных регистра, две группы элементов И, шифратор, два коммутатора, блок выбора формирователя адреса, два формирователя адреса начальных значений, два элемента И, две группы формирователей импульсов. Устройство позволяет производить динамическую запись значений длительностей входных сигналов в блок памяти, что позволяет увеличить глубину регистрации логического анализатора. 1 ил.

Регистрация

Составитель И.Сафронова Редактор В.Петраш Техред А.Кравчук Корректор Т.Малец

Заказ 5439/50

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Отображение

Подписное

| Вопросы радиоэлектроники | |||

| Сер | |||

| ЭВТ, 1981, вьш | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Заявка ФРГ № 3132984, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| . | |||

Авторы

Даты

1989-09-07—Публикация

1987-02-03—Подача