Изобретение относится к технике связи и может быть использовано в системах передачи данных.

Цель изобретения - повышение помехоустойчивости.

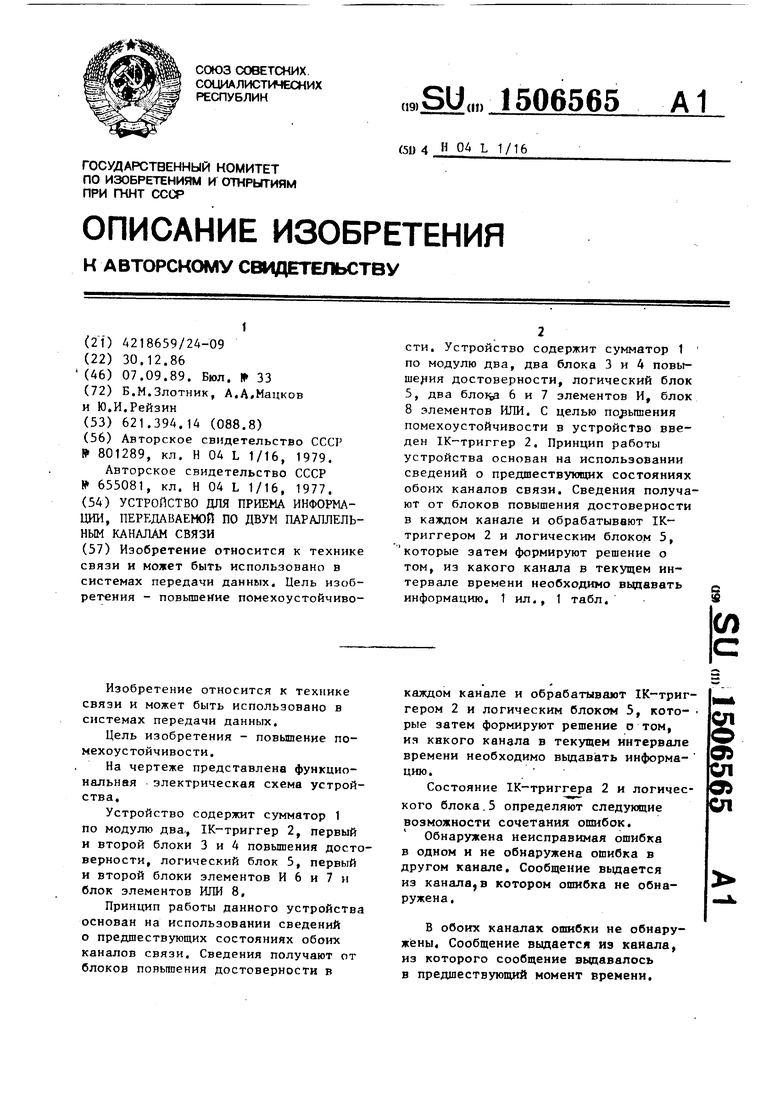

На чертеже представлена функциональная электрическая схема устройства.

Устройство содержит сумматор 1 по модулю два-, 1К-триггер 2, первый и второй блоки 3 и 4 повьшения достоверности, логический блок 5, первый и второй блоки элементов И 6 и 7 и блок элементов ИЛИ 8,

Принцип работы данного устройства основан на использовании сведений о предшествующих состояниях обоих каналов связи. Сведения получают от блоков повышения достоверности в

каждом канале и обрабатывают 1К-триг- гером 2 и логическим блоком 5, которые затем формируют решение о том, ия какого канала в текущем интервале времени необходимо выдавать информацию.

Состояние 1К-триггера 2 и логического блока.5 определяют следующие возможности сочетания ошибок.

Обнаружена неисправимая ошибка в одном и не обнаружена ошибка в другом канале. Сообщение выдается из канала,в котором ошибка не обнаружена.

В обоих каналах ошибки не обнаружены. Сообщение выдается из канала, из которого сообщение вьщавалось в предшествующий момент времени.

Од

сл

О)

сл

В обоих каналах обнаружены ошибки в одном канале исправимая, в другом канале неисправимая. Сообщение выдается из канала, в котором обнаружена исправимая ошибка.

В обоих каналах обнаружены исправимые ошибки: сообщение вьщается из канала, ия которого сообщение выдавалось в предшествующий момент времени

В одном канале обнаружена исправимая ошибка, в другом канале ошибка не обнаружена. Сообщение выдается из канала, я котором ошибка не обнаружена.

В обоих каналах обнаружены неисправимые ошибки. Сообщение выдается из канала, из которого сообщение выдавалось в предшествующий момент времени.

По сравнению с известными устройствами предлагаемое устройство уменьшает вероятность ошибки при наличии шестого сочетания ошибок, что позволяет обойтись без переспроса.

Устройство работает следующим образом.

Сигнал с первых управляющих выходов блоков повышения достоверности 3 и А а равен 1, когда в них обнаружена любая ошибка. В случае необнаружения ошибки сигналы а и а рравны О. Сигналы со вторых управляющих выходов блоков повьш1ения

достоверности 3 и 4 а-, а

13 25

равны

1 в случае обнаружения и исправления ошибки. Во всех остальных случаях сигналы а,, а.равны О. Сигнал Ср с выхода триггера 2 равен 1, если последней по времени зафиксирована ошибка во втором канале.

Таким образом, 1К-триггер 2 фиксирует номер канала, в котором во время приема предыдущей кодовой комбинации обнаружена ошибка с целью выдачи текущего сообщения из канала, в котором ранее и теперь ошибка не обнаружена. Сумматор 1 препятствует изменению состояния триггера 2 при одновременном отсутствии в обоих каналах обнаружения ошибок, либо в случае одновременного обнаружения в

каждом канале ошибок. Изменяет свое состояние триггер 2 при обнаружении ошибки только в одном канале. Тактирование триггера производится импульсами, поступающими на тактовый вход устройства.

5

0

5

О

5

0

5

0

5

Все сигналы, определяющие состояние каналов, поступают на входы логического блока 5, представляющего собой дешифратор, который может быть выполнен на основе постоянного запоминающего устройства (ПЗУ). Блоки 3 и 4 повышения достоверности также могут быть выполнены на основе ПЗУ.

Выходные сигналы Ь и b логического блока 5 управляют отпиранием одного из блоков элементов И 6 , (или 7), пропуская сообщение соответствующего канала через блок элементов ИЛИ 8 на выход устройства. Сигналы b, и Ь принимают значение, равное 1, в случае отпирания соответствующего

блока элементов И 6 (или 7),

I

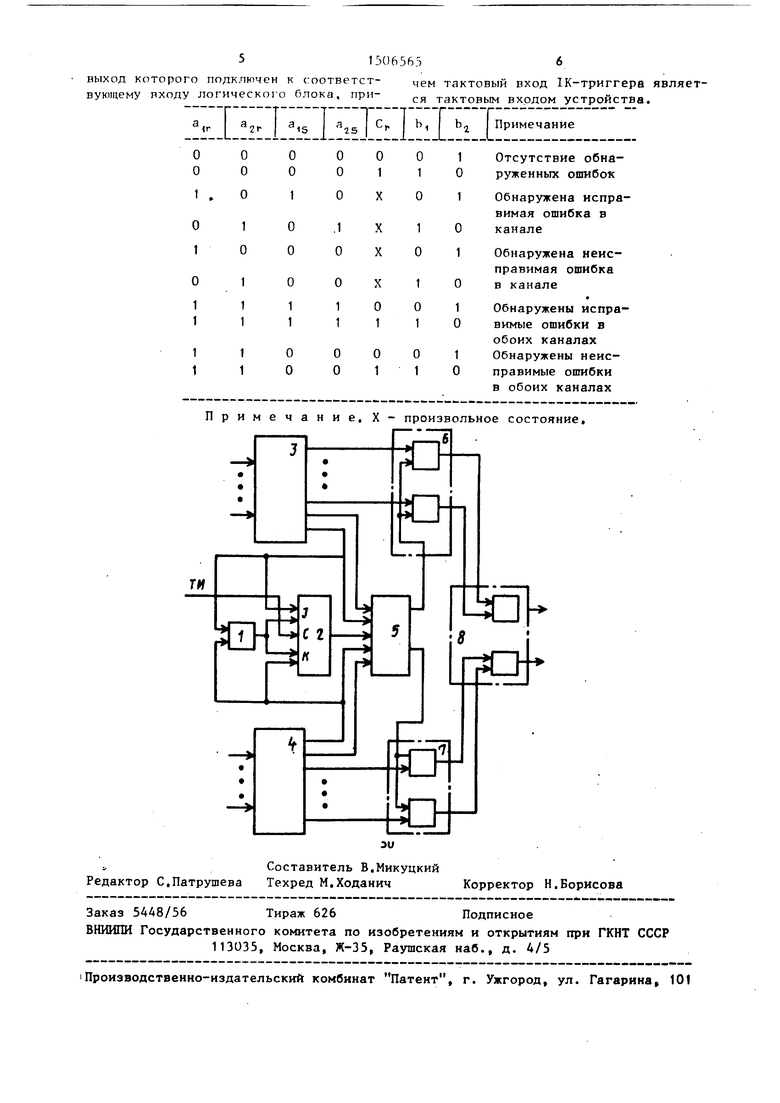

Алгоритм функционирования логической схемы 5 и всего устройства П1 иведен в таблице.

Таким образом, предлагаемое устройство обеспечивает повьш1гние помехоустойчивости при передаче информации без переспроса.

Формула изобретения

Устройство для приема информации, передаваемой по двум параллельным каналам связи, содержащее сумматор по модулю два, последовательно соединенные первый блок повьшгения достоверности и первый блок элементов И, блок элементов ИЛИ, к другим входам которого подключены выходы второго блока повышения достоверности .через второй блок элементов И, первый и второй управляющие выходы первого и второго блоков повышения достоверности подключены к соответствующим входам логического блока, первый и второй выходы которого подключены соответственно к управляющим входам первого и второго блоков элементов И, отличающееся тем, что, с целью повышения помехозащищенности,i введен ТК-триггер, при этом первый управляющий выход первого блока повышения достоверности подключен к первому 1-входу 1К-триггера и первому входу суг-1матора по модулю два, первый управляющий выход второго блока повышения достоверности подключен к первому К-входу 1К-триггера.и к второму входу сумматора по модулю два, выход которого подключен к объединенным вторым 1- и К-входам 1К-триггера,

515065656

выход которого полключен к соответст- цем тактовый вход 1К-триггера являетвующему яходу логического блока, прнся тактовым входом устройства.

I 2г I 15 I г5 I I г Примечание

г

ся тактовым входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1986 |

|

SU1387202A2 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Декодер линейного кода | 1986 |

|

SU1432786A1 |

| Запоминающее устройство | 1988 |

|

SU1531175A1 |

| Устройство для приема информации по двум параллельным каналам связи | 1979 |

|

SU873437A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Устройство для приема информации по двумпАРАллЕльНыМ КАНАлАМ СВязи B СиСТЕМЕ дляпЕРЕдАчи дАННыХ C РЕшАющЕй ОбРАТНОй СВязью | 1979 |

|

SU836806A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО:1 Т 5•..:' 'Уу | 1973 |

|

SU436388A1 |

Изобретение относится к технике связи и может быть использовано в системах передачи данных. Цель изобретения - повышение помехоустойчивости. Устройство содержит сумматор 1 по модулю два, два блока 3 и 4 повышения достоверности, логический блок 5, два блока 6 и 7 элементов И, блок ИЛИ 8 элементов. С целью повышения помехоустойчивости в устройство введен JK-триггер 2. Принцип работы устройства основан на использовании сведений о предшествующих состояниях обоих каналов связи. Сведения получают от блоков повышения достоверности в каждом канале и обрабатывают JK-триггером 2 и логическим блоком 5, которые затем формируют решение о том, из какого канала в текущем интервале времени необходимо выдавать информацию. 1 ил., 1 табл.

ОО0001 Отсутствие обнаОО0110 руженных ошибок

О10X0 1 Обнаружена исправимая ошибка в 1О.1 X 1 О канале

0О0X01 Обнаружена неисправимая ошибка 1ОО X1О в канале

Примечание. Х- произвольное состояние.

| Устройство фазирования по цик-лАМ | 1979 |

|

SU801289A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1977 |

|

SU655081A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-07—Публикация

1986-12-30—Подача