Изобретение относится к вычислительной технике и электронике и может быть использовано при построении устройств для считывания информации из накопителей запоминающих устройств в качестве элемента, осуществляющего предварительньй подзаряд шин данных.

Целью изобретения является расширение области применения за счет обеспечения возможности формирования сиг- налов предварительного заряда как с исходного нулевого уровня, так и с высокого уровня без предварительного обнуления подзаряжаемой шины.

го четвертый транзистор 4. В случае, если ди° Ugfi , что имеет место при 20 выполнении условия

1.

бс7

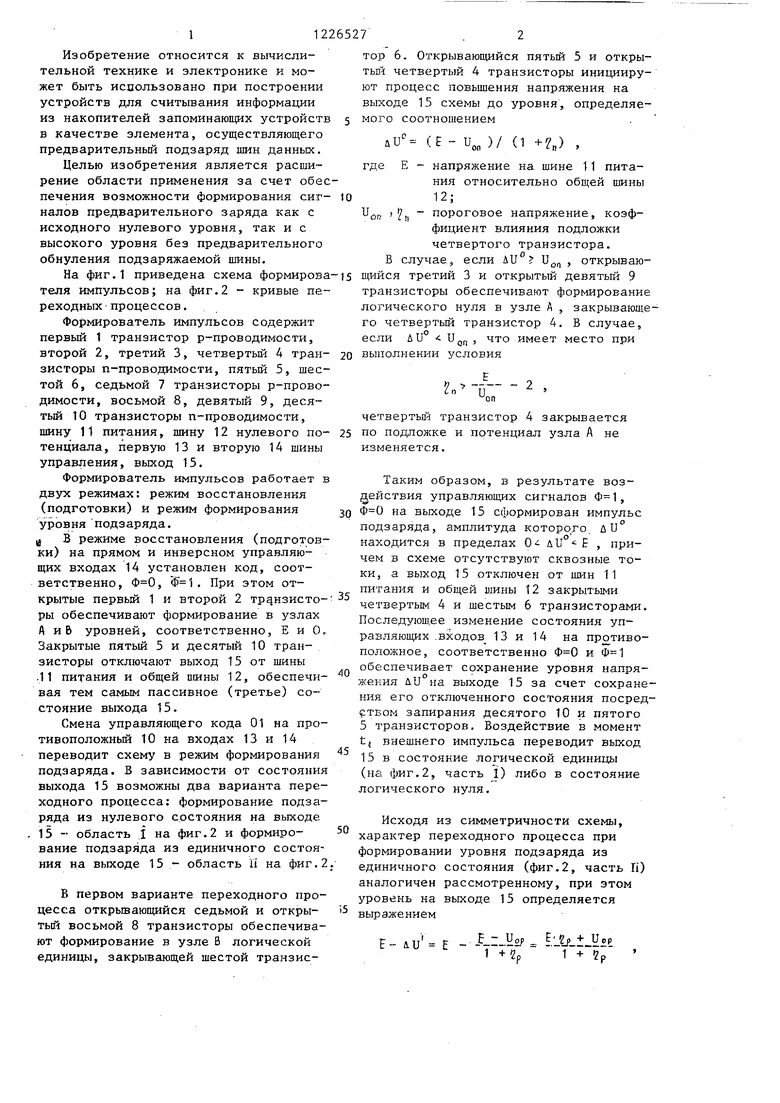

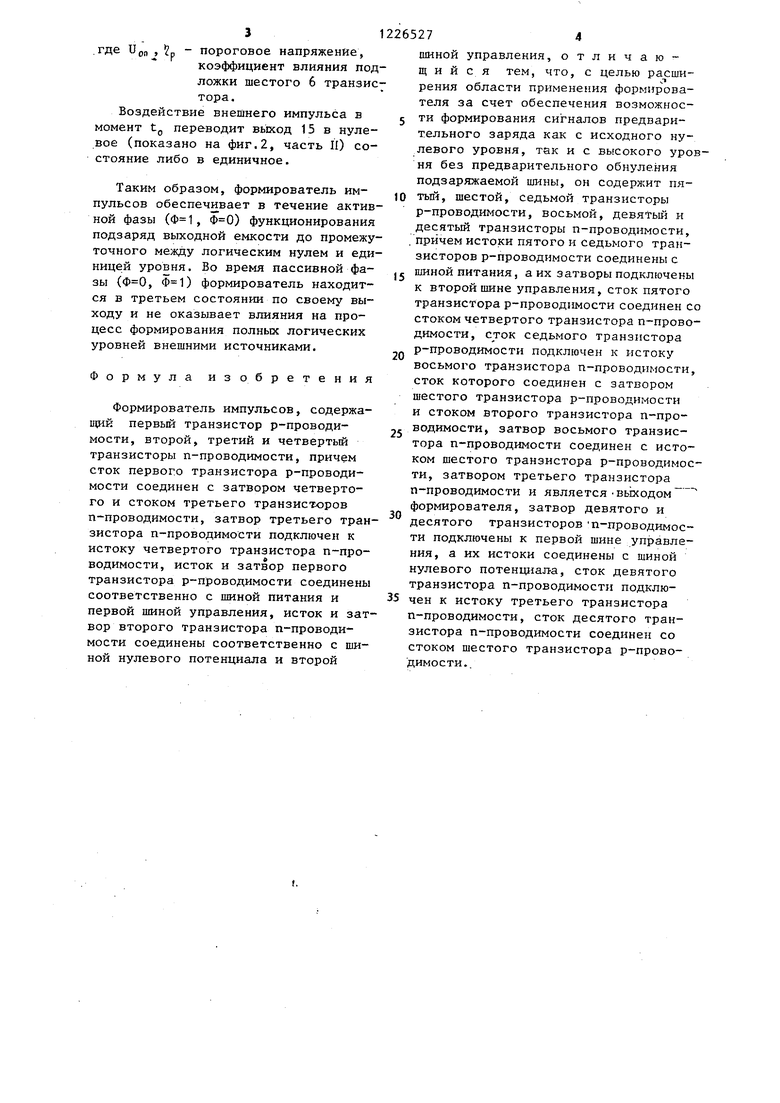

На фиг.1 приведена схема формирова-|5 щийся третий 3 и открытый девятый 9 теля импульсов; на фиг.2 - кривые пе- транзисторы обеспечивают формирование реходных-процессов. ,логического нуля в узле А , закрывающеФормирователь импульсов содержит первый 1 транзистор р-проводимости, второй 2, третий 3, четвертый 4 транзисторы п-проводимости, пятый 5, шестой 6, седьмой 7 транзисторы р-проводимости, восьмой 8, девятый 9, десятый 10 транзисторы п-проводимости, шину 11 питания, шину 12 нулевого потенциала, первую 13 и вторую 14 шины управления, выход 15.

Формирователь импульсов работает в двух режимах: режим восстановления (подготовки) и режим формирования уровня подзаряда.

В режиме восстановления (подготовки) на прямом и инверсном управляющих входах 14 установлен код, соответственно, , . При этом открытые первый 1 и второй 2 трднзисто- 35 ры обеспечивают формирование в узлах А иВ уровней, соответственно, Б и О, Закрытые пятый 5 и десятьш 10 транзисторы отключают выход 15 от шины .11 питания и общей пмны 12, обеспечивая тем самым пассивное (третье) состояние выхода 15.

Смена управляющего кода 01 на противоположный 10 на входах 13 и 14 переводит схему в режим формирования подзаряда. В зависимости от состояния выхода 15 возможны два варианта переходного процесса: формирование подзаряда из нулевого состояния на выходе 15 - область i на фиг.2 и формирование подзаряда из единичного состояния на выходе 15 - область а на фиг.2.

В первом варианте переходного процесса открьшающийся седьмой и откры- тьй восьмой 8 транзисторы обеспечивают формирование в узле В логической единицы, закрывающей шестой транзисчетвертья транзистор 4 закрывается 25 по подложке и потенциал узла А не изменяется.

Таким образом, в результате воздействия управляюш х сигналов , 30 на вь.1ходе 15 сформирован импульс подзаряда, амплитуда которого, ли находится Б пределах 0 Е , причем в схеме отсутствуют сквозные токи, а выход 15 отключен от шин 11 питания и общей шины 12 закрытыми четвертым: 4 и шестым 6 транзисторами. Последуюш,ее изменение состояния уп- равляюшзих .входов 13 и 14 на пр тиво- положное, соответственно и обеспечивает срхранение уровня напря- жек:ия uU на выходе 15 за счет сохранения: его отключенного состояния посредством запирания десятого 10 и пятого 5 транзисторов. Воздействие в момент

40

45

50

t внешнего импульса переводит выход 15 в состоян:ие логической единицы (на фиг.2, часть 1) либо в состояние логического нуля.

Исходя из симметричности схемы, характер переходного процесса при формировании уровня подзаряда из единичного состояния (фиг.2, часть П) аналогичен рассмотренному, при этом уровень на выходе 15 определяется выражение:м

F- iu Е - §.,

1 +2о

1 +

гр

тор 6. Открывающийся пятый 5 и открыться четвертый 4 транзисторы инициируют процесс повышения напряжения на выходе 15 схемы до уровня, определяемого соотношением

ди (Е UOH)/ о )

где Е - напряжение на шине 11 питания относительно обп1;ей шины I2j

UOR ji пороговое напряжение, коэффициент влияния подложки четвертого транзистора.

В случае, если

ли

, открываю1.

бс7

t внешнего импульса переводит выход 15 в состоян:ие логической единицы (на фиг.2, часть 1) либо в состояние логического нуля.

Исходя из симметричности схемы, характер переходного процесса при формировании уровня подзаряда из единичного состояния (фиг.2, часть П) аналогичен рассмотренному, при этом уровень на выходе 15 определяется выражение:м

F- iu Е - §.,

1 +2о

1 +

гр

3

.где Upn , 5р - пороговое напряжение,

коэффициент влияния подложки шестого 6 транзистора.

Воздействие внешнего импульса в момент tg переводит выход 15 в нулевое (показано на фиг, 2, часть II) состояние либо в единичное.

Таким образом, формирователь импульсов обеспечивает в течение активной фазы (, ) функционирования подзаряд выходной емкости до промежуточного между логическим нулем и единицей уровня. Во время пассивной фазы (, ) формирователь находится в третьем состоянии по своему выходу и не оказывает влияния на процесс формирования полных логических уровней внешними источниками.

Формула изобретения

Формирователь импульсов, содержа- 1щк первьй транзистор р-проводи- мости, второй, третий и четвертый транзисторы п-проводимости, причем сток первого транзистора р-проводи- мости соединен с затвором четвертого и стоком третьего транзисторов п-проводимости, затвор третьего тран зистора п-проводимости подключен к истоку четвертого транзистора п-проводимости, исток и затвор первого транзистора р-проводимости соединены соответственно с шиной питания и первой шиной управления, исток и зат вор второго транзистора п-проводимости соединены соответственно с шиной нулевого потенциала и второй

2265274

шиной управления, отличающийся тем, что, с целью расширения области применения формир ова- теля за счет обеспечения возможнос- 5 ти формирования сигналов предварительного заряда как с исходного нулевого уровня, так и с высокого уровня без предварительного обнуления подзаряжаемой шины, он содержит пя10 тьш, шестой, седьмой транзисторы р-проводимости, восьмой, девятый и десятый транзисторы п-проводимости, .причем истоки пятого и седьмого транзисторов р-проводимости соединены с

и шиной питания, а их затворы подключены к второй шине управления, сток пятого транзистора р-проводимости соединен со стоком четвертого транзистора п-проводимости, сток седьмого транзистора р-проводимости подключен к истоку восьмого транзистора п-проводимости, сток которого соединен с затвором шестого транзистора р-проводимости и стоком второго транзистора п-проводимости, затвор восьмого транзистора п-проводимости соединен с истоком шестого транзистора р-проводимости, затвором третьего транзистора п-проводимости и является вь1ходом формирователя, затвор девятого и десятого транзисторов п-проводимости подключены к первой шине управления, а их истоки соединены с шиной нулевого потенциаЛ а, сток девятого транзистора п-проводимости подклю35 чен к истоку третьего транзистора п-проводимости, сток десятого транзистора п-проводимости соединен со стоком шестого транзистора р-проводимости..

20

25

30

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов для блоков памяти | 1985 |

|

SU1278973A1 |

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Формирователь импульсов | 1983 |

|

SU1123056A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2016 |

|

RU2628152C1 |

| Формирователь импульсов | 1981 |

|

SU991507A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

Изобретение относится к области вычислительной техники и электроники и может быть использовано при построении устройств для считывания информации из накопителей запоминающих устройств в качестве элемента, осуществляющего предварительный подза- ряд шин данных. Целью изобретения является расширение области применения устройства за счет обеспечения возможности формирования сигналов предварительного заряда как с исходного нулевого,уровня, так и с высокого уровня без предварительного обнуления подзаряжаемой шины. Формирователь работает в двух режимах: режим восстановления (подготовки) и режим формирования уровня подзаряда. 2 ил. с SS сл с

| СПОСОБ СОЗДАНИЯ ГОМОЗИГОТНЫХ ЛИНИЙ РЖИ | 1992 |

|

RU2028044C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Формирователь импульсов | 1983 |

|

SU1123056A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-04-23—Публикация

1984-09-28—Подача