Изобретение относится к вычисли- тельной технике и может быть использовано в многопроцессорных системах для оперативного распределения задач между процессорами.

Цель изобретения - повьшейие быстродействия устройства.

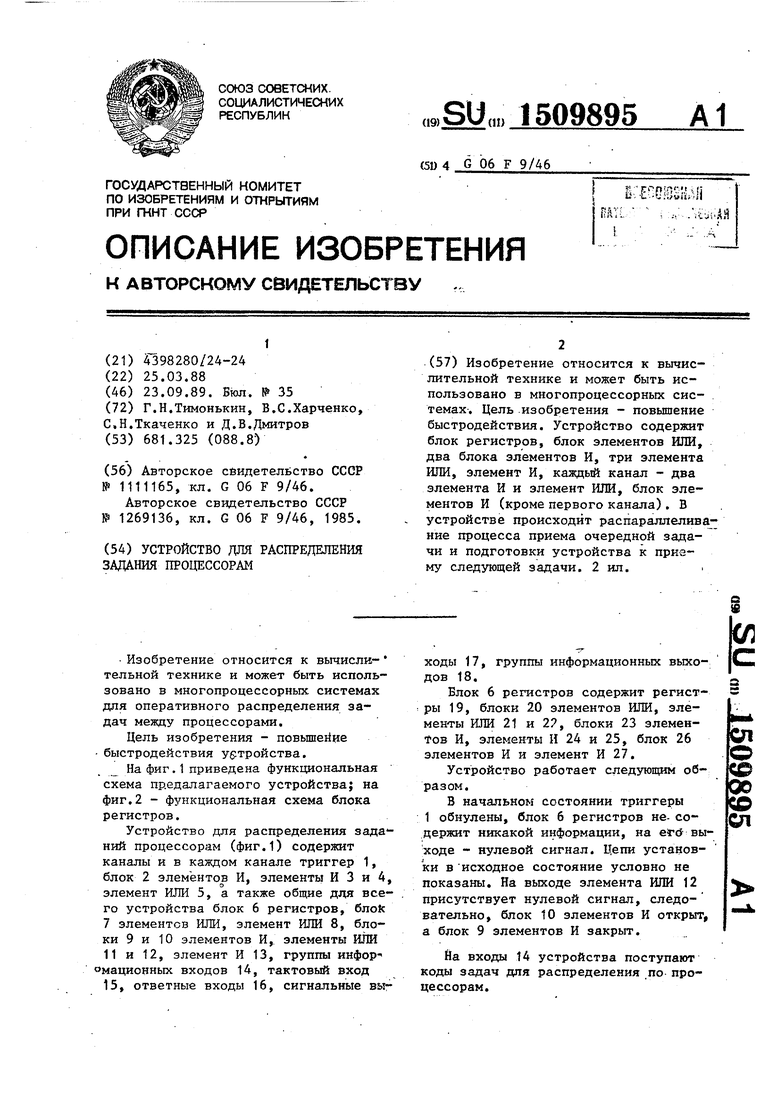

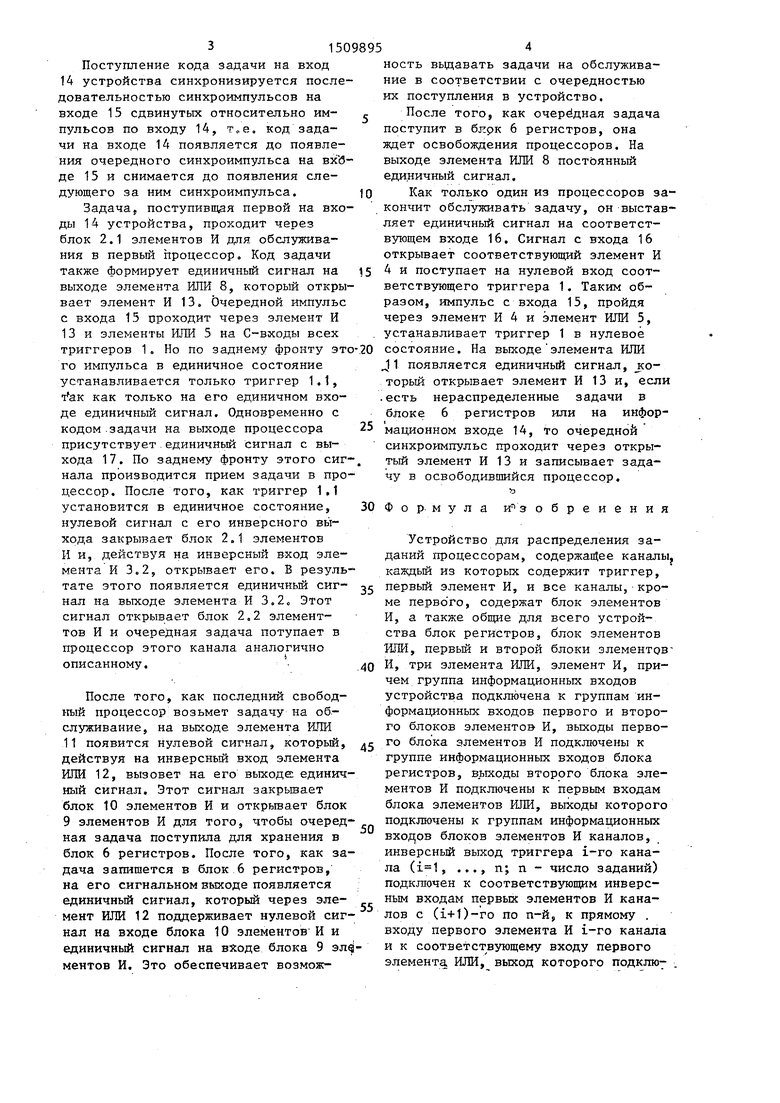

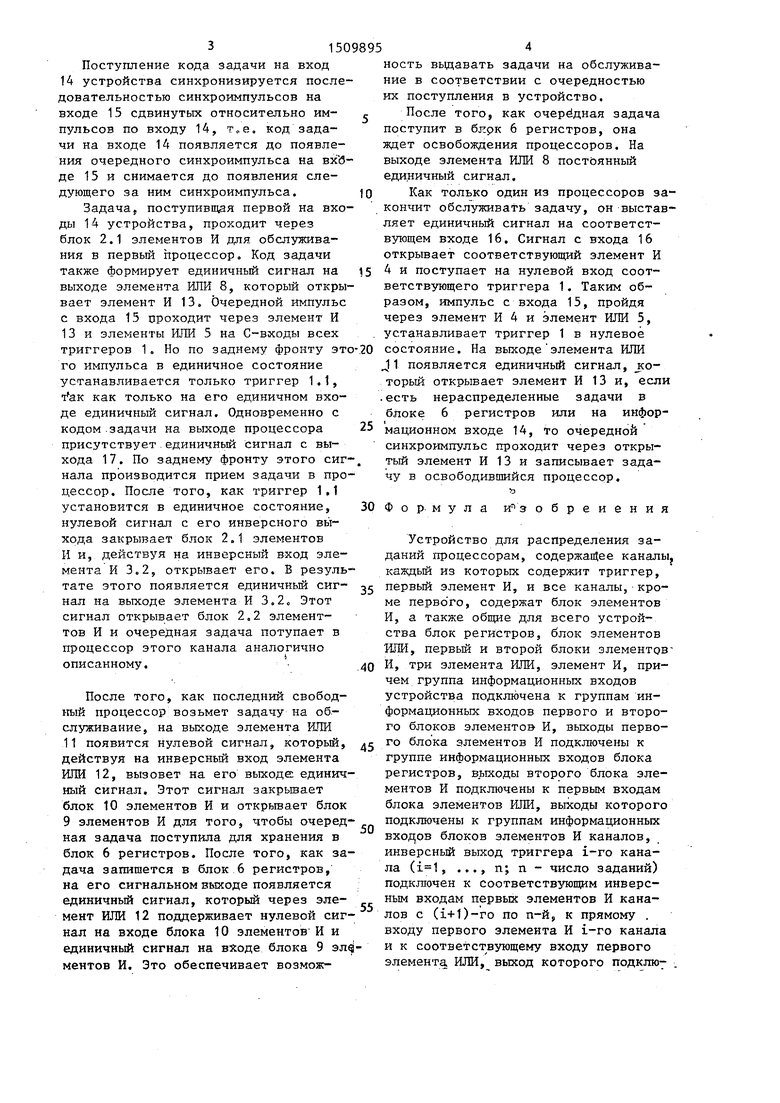

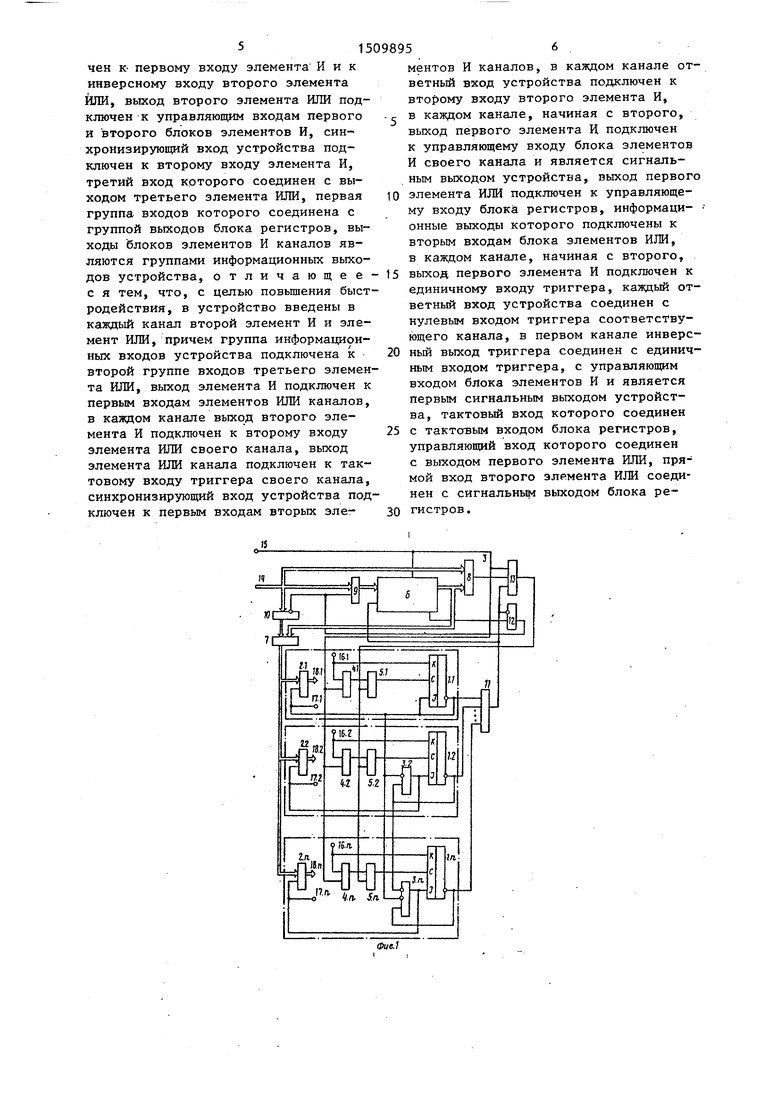

На фиг. 1 приведена функциональная схема пр.едалагаемого устройства; на фиг.2 - функциональная схема блока регистров.

Устройство для распределения зада ний процессорам (фиг.1) содержит каналы и в каждом канале триггер 1, блок 2 элементов И, элементы И 3 и 4, элемент ИЛИ 5, а также общие ддя всего устройства блок 6 регистров, блок 7 элементов ИЛИ, элемент ИЛИ 8, блоки 9 и 10 элементов И, элементы ИЛИ 11 и 12, элемент И 13, группы инфор «мационных входов 14, тактовый вход 15, ответные входы 16, сигнальные вьтходы 17, группы информационных выходов 18.

Блок 6 регистров содержит регист- ры 19, блоки 20 элементов ШШ, элементы ЯПИ 21 и 2, блоки 23 элементов И, элементы И 24 и 25, блок 26 элементов И и элемент И 27.

Устройство работает следующим образом.

В начальном состоянии триггеры 1 обнулены, блок 6 регистров не- содержит никакой информации, на егб выходе - нулевой сигнал. Цепи установки в исходное состояние условно не показаны. На выходе элемента ИЛИ 12 присутствует нулевой сигнал, следовательно, блок 10 элементов И открыт, а блок 9 элементов И закрыт.

На входы 14 устройства поступают коды задач дня распределения по процессорам.

О1

о

CD 00 СО СП

3150

Поступление кода задачи на вход 14 устройства синхронизируется последовательностью синхроимпульсов на входе 15 сдвинутых относительно им- пульсов по входу 14, т„е. код задачи на входе 14 появляется до появления очередного синхроимпульса на вх б- де 15 и снимается до появления следующего за ним синхроимпульса.

Задача, поступившая первой на входы 14 устройства, проходит через блок 2.1 элементов И для обслуживания в первый процессор. Код задачи также формирует единичньй сигнал на выходе элемента ИЛИ 8, который открывает элемент И 13. Очередной импульс с входа 15 проходит через элемент И 13 и элементы ИЛИ 5 на С-входы всех триггеров 1. Но по заднему фронту эт го импульса в единичное состояние устанавливается только триггер 1.1, как только на его единичном входе единичный сигнал. Одновременно с кодом .задачи на выходе процессора присутствует.единичный сигнал с выхода 17. По заднему фронту этого сиг нала производится прием задачи в процессор. После того, как триггер 1,1 установится в единичное состояние, нулевой сигнал с его инверсного выхода закрывает блок 2.1 элементов И и, действуя на инверсный вход элемента И 3.2, открывает его. В результате этого появляется единичньй сиг- нал на выходе элемента И 3.2 Этот сигнал открывает блок 2.2 элемент- тов И и очередная задача потупает в процессор этого канала аналогично

описанному.

После того, как последний свободный процессор возьмет задачу на об.- служивание, на выходе элемента ИЛИ 11 появится нулевой сигнал, который, действуя на инверсный вход элемента ИЛИ 12, вызовет на его выходе единичный сигнал. Этот сигнал закрьшает блок 10 элементов И и открьгеает блок 9 элементов И для того, чтобы очередная задача поступила для хранения в блок 6 регистров. После того, как задача запишется в блок 6 регистров, на его сигнальном выходе появляется единичный сигнал, который через эле- мент ИЛИ 12 поддерживает нулевой сигнал на входе блока 10 элементов И и единичный сигнал на входе блока 9 эл ментов И. Это обеспечивает возмож

с

5 0 5 0 5

0

5

0

ность выдавать задачи на обслуживание в соответствии с очередностью их поступления в устройство.

После того, как очерёдная задача поступит в бкрк 6 регистров, она ждет освобождения процессоров. На выходе элемента ИЛИ 8 постоянный единичный сигнал.

Как только один из процессоров закончит обслуживать задачу, он выставляет единичный сигнал на соответствующем входе 16. Сигнал с входа 16 открывает соответствующий элемент И 4 и поступает на нулевой вход соответствующего триггера 1. Таким образом, импульс с входа 15, пройдя через элемент И 4 и элемент ИЛИ 5, устанавливает триггер 1 в нулевое состояние. На выходе элемента Р1ЛИ J1 появляется единичный сигнал, ко- торый открывает элемент И 13 и, если есть нераспределенные задачи в блоке 6 регистров или на информационном входе 14, то очередной синхроимпульс проходит через откры- тый элемент И 13 и записывает задачу в освободившийся процессор. з

Формула и э обреиения

Устройство для распределения заданий процессорам, содержащее каналы, каждый из которых содержит триггер, первый элемент И, и все каналы,кроме перво го, содержат блок элементов И, а также общие для всего устройства блок регистров, блок элементов ИЛИ, первый и второй блоки элементов- И, три элемента ИЛИ, элемент И, причем группа информационных входов устройства подключена к группам информационных входов первого и второго блоков элементов И, выходы первого блока элементов И подключены к группе информационных входов блока регистров, в.ыходы второго блока элементов И подключены к первым входам блока элементов ШШ, выходы которого подключены к группам информационных входов блоков элементов И каналов, инверсный выход триггера i-ro канала (, ..., п; п - число заданий) подключен к соответствзтощим инверсным входам первых элементов И каналов с (i+1)-ro по п-й, к прямому . входу первого элемента И i-ro канала и к соответствующему входу первого элемента ИЛИ, выход которого подклю7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1990 |

|

SU1751760A1 |

| Многопроцессорная система | 1987 |

|

SU1494005A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1569831A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1277111A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524052A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1543404A1 |

| Многопроцессорная система | 1989 |

|

SU1735866A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1347081A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных системах. Цель изобретения - повышение быстродействия. Устройство содержит блок регистров, блок элементов ИЛИ, два блока элементов И, три элемента ИЛИ элемент И, каждый канал- два элемента И и элемент ИЛИ, блок элементов И (кроме первого канала). В устройстве происходит распараллеливание процесса приема очередной задачи и подготовки устройства к приему следующей задачи. 2 ил.

| Устройство для распределения заданий процессорам | 1983 |

|

SU1111165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1269136A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-23—Публикация

1988-03-25—Подача