(Л

СП

vj

о to

00

Фиг.1

15

Язоб|эе геиие относится к вычислительной техш1ке и йожет быть использовано в автоматизированных системах программного логического управления те ;ноло1 нческимн процессами,

Целью изобретения является повыше- Гие быстродействия устройства,

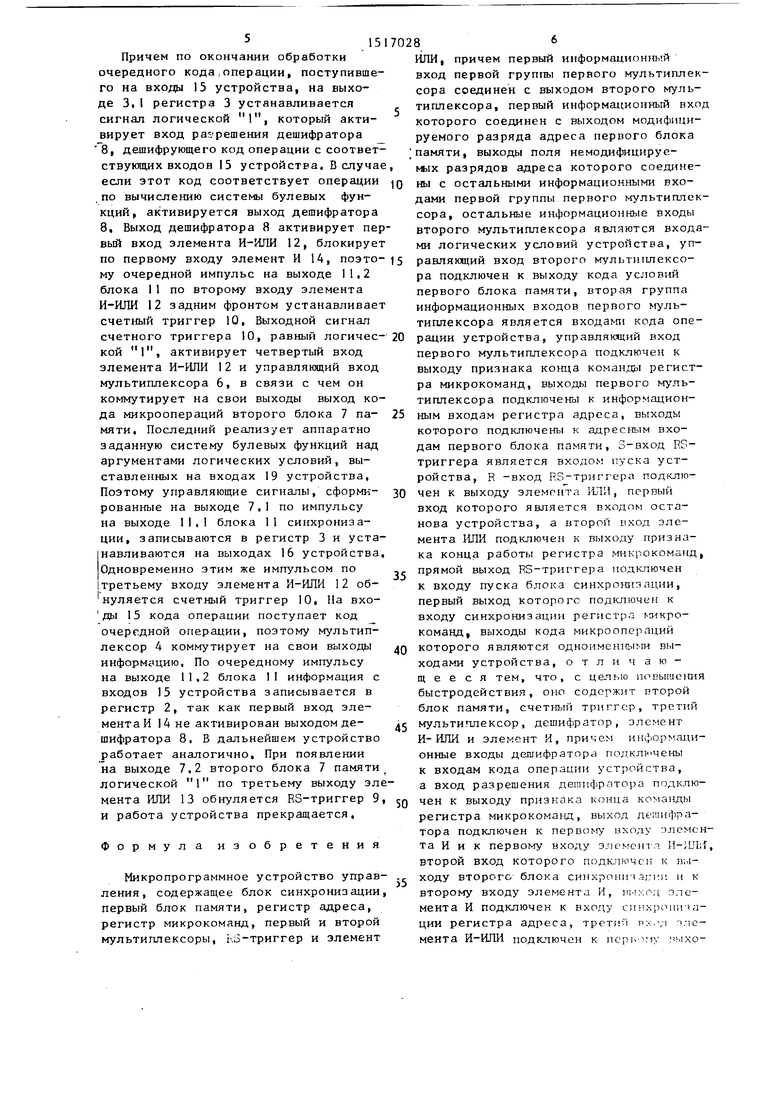

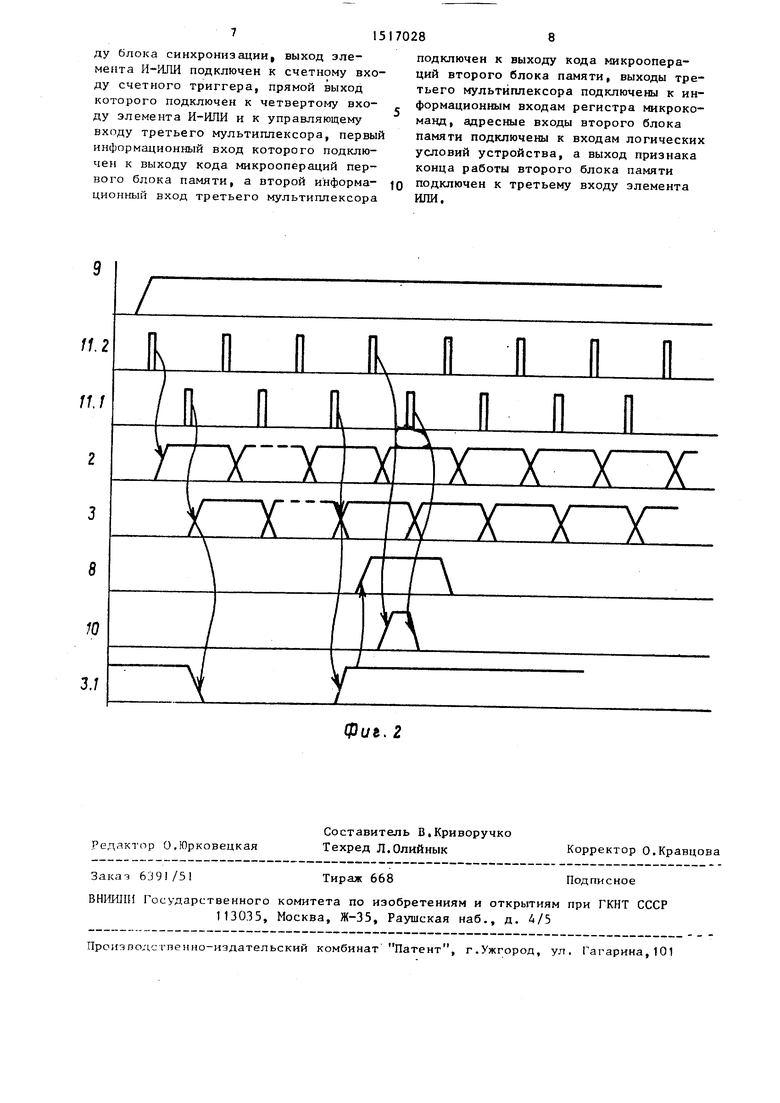

Па фиг. представлена функциональная схема №1кропрограммного устройст- Q ва управлсн ;я; на фиг, 2 - временная диаграмма работы устройства,

Микропрограммное устройство управления содсрет1т первый блок 1 памяти, имеютнй выход 1,1 кода адреса, старший разряд 1,1,1 кода и адреса, выход 1,2 кода условия и выход 1,3 кода микрооперсЩиГ), регистр 2 адреса, регисгр 3 микрокоманд, имеющий выходы признаков конца команды 3,1 и конца работы 3,2, с первого но третий мульти шексоры 4-6, второй блок 7 памяти, имеющий выход 7,1 кода микроопе- рацпГ и выход 7.2 признака конца работы, дешифратор 8, RS-триггер 9,25 счетпз триггер 10, блок 11 синхронизации, имеющи выходы 11,1 и 11,2 iicpjiOr o и второго режимов синхрониза- ци, элемент Ш1И 12 элемент ИЛИ 13,

И 14, 13ХОДЫ

15 /ход1:1 16 М11крсо11ераций, вход 17 нус- ка, вход 18 останова и входы 9 логических у ел о в и и ,

икpoпpoгpa мнoe устройство управ- лепяя работает сгтедующим образом.

На входы 15 устройства подается код оперании, а па вход 17 пуска - им20

ступающего на мультиплексор 5, При наличии (гулевой информации на выходе 1,2 fyл ьтиш eкcop 5 коммутирует на свой выход информацию с выхода 1,1,1 первого блока I памяти и происходит безусловное формирование адреса следующей ячейки памяти независимо от логических условий на входах 19, Па выходе 1,3 первого блока 1 памяти устанавливается информация микроопераций, поступающая на мультиплексор 6, которая и коммутируется на его выходы, так как счетный триггер 10, уп- равляюшд1й его входами, обнулен. Информация микроопераций записывается в регистр 3 по заднему фронту импульса на выходе 11,1 блока И сннхронизации. Таким образом, на выходах 16 устройства устанавливается информация микроопераций, а на выход 3,1 регистра 3 подается логическая 1, По следующе- Nfy импульсу на выходе 11,2 блока 1 1 синхронизации в регистр 2 с выходов мультиплексора 4 записывается адрес очередной ячейкн первого блока 1 памяти, С первого блока 1 памяти вновь считывается информация об адресе следующей ячейки памяти (выход 1,1), пуска, по которому устанавливается в

15 кода операции,5д де логических условий (выход 1,2) и

микрооперациях (выход 1,3), В зависимости от логических условий, кода логических условий выход 1,1 в конкатенации с выходом мультиплексора 5 фор шруют адрес следующей ячейки памяти. Так же по импульсу на выходе 11,1 блока 11 очередная информация микроопераций записывается в регистр 3 и устанавливается на выходах 16 ус35

RS-триггер 9, Выходной сиг5

Q

5

0

ступающего на мультиплексор 5, При наличии (гулевой информации на выходе 1,2 fyл ьтиш eкcop 5 коммутирует на свой выход информацию с выхода 1,1,1 первого блока I памяти и происходит безусловное формирование адреса следующей ячейки памяти независимо от логических условий на входах 19, Па выходе 1,3 первого блока 1 памяти устанавливается информация микроопераций, поступающая на мультиплексор 6, которая и коммутируется на его выходы, так как счетный триггер 10, уп- равляюшд1й его входами, обнулен. Информация микроопераций записывается в регистр 3 по заднему фронту импульса на выходе 11,1 блока И сннхронизации. Таким образом, на выходах 16 устройства устанавливается информация микроопераций, а на выход 3,1 регистра 3 подается логическая 1, По следующе- Nfy импульсу на выходе 11,2 блока 1 1 синхронизации в регистр 2 с выходов мультиплексора 4 записывается адрес очередной ячейкн первого блока 1 памяти, С первого блока 1 памяти вновь считывается информация об адресе следующей ячейки памяти (выход 1,1), ко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах програмного логического управления технологическими процессами. Цель изобретения - повышение быстродействия. Устройство содержит первый блок памяти 1, регистры адреса 2 и микрокоманд 3, с первого по третий мультикомпрессоры 4, 5, 6, второй блок памяти 7, дешифратор 8, RS - триггер 9, счетный триггер 10, блок синхронизации 11, элемент И-ИЛИ 12, элемент ИЛИ 13 и элемент И 14. 2 ил.

пап триггера 9 запускает блок 11 сии- JQ тройства. Далее устройство работает

хроплзации, который начинает генерировать две неперекрывающиеся последовательности импульсов на выходах 11,1 и 11,2, В .исходном положении все регистры и триггеры общ-лены, (цепи не но- казлмы), поэтому информация с выходов мультитвксора 4 записывается в регистр 2 по заднему фронту импульса li. j ;.;1,1ходе 11,2 блока 11, так как ак- Т ;Епрова: первый (инверсный) вход эле ме}ггл И 14, Выходные сигначы регистра 2 адресуют первый блок 1 памяти, и на егс в) устанавливается информация: Ы в:, 1,1 - адрес следующей ячей-ки памяти, старший разряд 1,1,1 выхс1да , 1 используется для безуслов- ног фирм;1рования адреса следующей :;лмяти, на выходе 1,2 устанав- ли ло-г-с ; код логического условия, но

аналогично до тех пор, пока на выходе 3,1 регистра 3 не появится логический О, свидетельствующий о заверщении команды. Тогда в регистр 2 будет записан адрес очередной команды с входов 15 кода операции.

Далее устройство работает аналогично до появления на выходе 3,2 регистра 3 логической I, свидетельствующей об окончании работы. Это приводит к сбросу RS-триггера 9 по вто- входу элемента ИЛИ 13, В связи с этим останавливается блок 1I син- хро шзации и работа устройства завершается, RS-триггер 9 может быть также обнулен сигналом на входе 18 останова по первому входу элемента ИЛИ 13,

15

Причем по окончании обработки очередного кода,операции, поступившего на входы 15 устройства, на выходе 3. 1 регистра 3 устанавливается сигнал логической 1, который акти- вирует вход разрешения дешифратора 8, дешифрующего код операции с соответ ствукядих входов 15 устройства. В случае если этот код соответствует операции по вычислению системы булевых функций, активируется выход дешифратора 8, Выход дешифратора 8 активирует первый вход элемента И-ИЛИ 12, блокирует по первому входу элемент И 14, поэтому очередной импульс на выходе 11.2 блока 11 по второму входу элемента И-ИЛИ 12 задним фронтом устанавливает счетный триггер 10, Выходной сигнал счетного триггера 10, равный логической 1, активирует четвертый вход элемента И-ИЛИ 12 и управляющий вход мультиплексора 6, в связи с чем он коммутирует на свои выходы выход кода микроопераций второго блока 7 памяти. Последний реализует аппаратно заданную систему булевых функций над аргументами логических условий, выставленных на входах 19 устройства, Поэтому управляющие сигналы, сформированные на выходе 7.1 по импульсу на выходе 11,1 блока 11 синхронизации, записываются в регистр 3 и устанавливаются на выходах 16 устройства. Одновременно этим же импульсом по третьему входу элемента И-ИЛИ 12 об- нуляется счетный триггер 10, Па вхо- ды 15 кода операции поступает код очередной операции, поэтому мультиплексор 4 коммутирует на свои выходы информацию, По очередному импульсу на выходе 11,2 блока II информация с входов 15 устройства записывается в регистр 2, так как первый вход элемента И 14 не активирован выходом дешифратора 81 В дальнейшем устройство работает аналогично. При появлении на выходе 7,2 второго блока 7 памяти логической 1 по третьему выходу элемента ИЛИ 13 обнуляется RS-триггер 9, и работа устройства прекращается.

Формула изобретения

Микропрограммное устройство управления, содержащее блок синхронизации, первый блок памяти, регистр адреса, регистр микрокоманд, первый и второй мультиплексоры, Ь.З-триггер и элемент

86

ИЛИ, причем первый информационн11 Й вход первой группы первого мультиплексора соединен с выходом второго fyль- типлексора, первый информационный вход которого соединен с выходом модифицируемого разряда адреса первого блока памяти, выходы поля немодифицируекых разрядов адреса которого соединены с остальными информационными входами первой группы первого мультиплексора, остальные информационные входы второго мультиплексора являются входами логических условий устройства, управляющий вход второго мультиплексора подключен к выходу кода условий первого блока памяти, вторая группа информационных входов первого типлексора является входаьш кода операции устройства, управляющий вход первого мультиплексора подключе) к выходу признака ко1ща команды регистра микрокоманд, выходы первого мультиплексора подключены к информационным входам регистра адреса, выходы которого подключены к адресным входам первого блока памяти, 3-вход RS- триггера является вxoдo пуска устройства, R -вход Р.З-триггера подключен к выходу элемента 1ПИ, первыр вход которого является входом останова устройства, а второй вход элемента ИЛИ подключен к выходу признака конца работы регистра микрокоманд, прямой выход RS-триггера подключен к входу пуска блока синхроштгзации, первый выход которого подключен к входу синхронизации регистра NMKPO- команд, выходы кода микроопераций

которого являются одноименными выходами устройства, о т л и c а ю - щ е е с я тем, что, с целью повышения быстродействия, оно содержит пторой блок памяти, счетный триггер, третий

мультиплексор, дешифратор, элемент И-ИЛИ и элемент И, причем информационные входы дешифратора по;з,кл)| Чены к входам кода операции устройства, а вход разрешения дегаифратора подключей к выходу признака конца команды регистра микрокоманд, выход дешифратора подключен к nepDONry входу элемента И и к первому входу sjicMetna Ji-iUlif, второй вход которого подключен к пыходу второго блока синхроничаиии и к второму входу элемента И, пь.о;( элемента И подключен к вхоцу синхронича- ции регистра адреса, третий PX.-/I э.-гс- мента И-ИЛИ подключен к периомл- пыхо

ду блока синхронизацииI выход элемента И-ИЛИ подключен к счетному входу счетного триггера, прямой выход которого подключен к четвертому входу элемента И-ИЛИ и к управляющему входу третьего мультиплексора, первый информационный вход которого подключен к выходу кода микроопераций первого блока памяти, а второй информационный вход третьего мультиплексора

1

)

I

Редактор О.Юрковецкая

Составитель В.Криворучко Техред Л.Олийнык

Заказ 6391/51

Тираж 668

ВНИШ1И Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. Д/5

подключен к выходу кода микроопераций второго блока памяти, выходы третьего мультиплексора подключены к информационным входам регистра микрокоманд, адресные входы второго блока памяти подключены к входам логических условий устройства, а выход признака конца работы второго блока памяти подключен к третьему входу элемента ШШ.

фуг. 2

Корректор О.Кравцова

Подписное

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Майоров С.А., Новиков Г.И | |||

| Структура электронных вычислительных машин,-Л.: Машиностроение, 1979, с | |||

| Мяльно-трепальный станок | 1921 |

|

SU314A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1989-10-23—Публикация

1988-03-01—Подача