о

х

10

15

20

25

31522385

Изобретение относится к импульсной технике и может 6bitb использовано в различных областях вычислительной техники, системах управления и контроля, где требуется генерирование импульсных сигналов (кодовых посылок или периодических сигналов) с программируемой длительностью импульсов, периодом и фа ЗОЙ о

Цель изобретения - расширение диапазона регулирования параметров (периода. Фазы, длительности импульса) формируемой импульсной последовательности за счет уменьшения минимальных значений этих параметров„

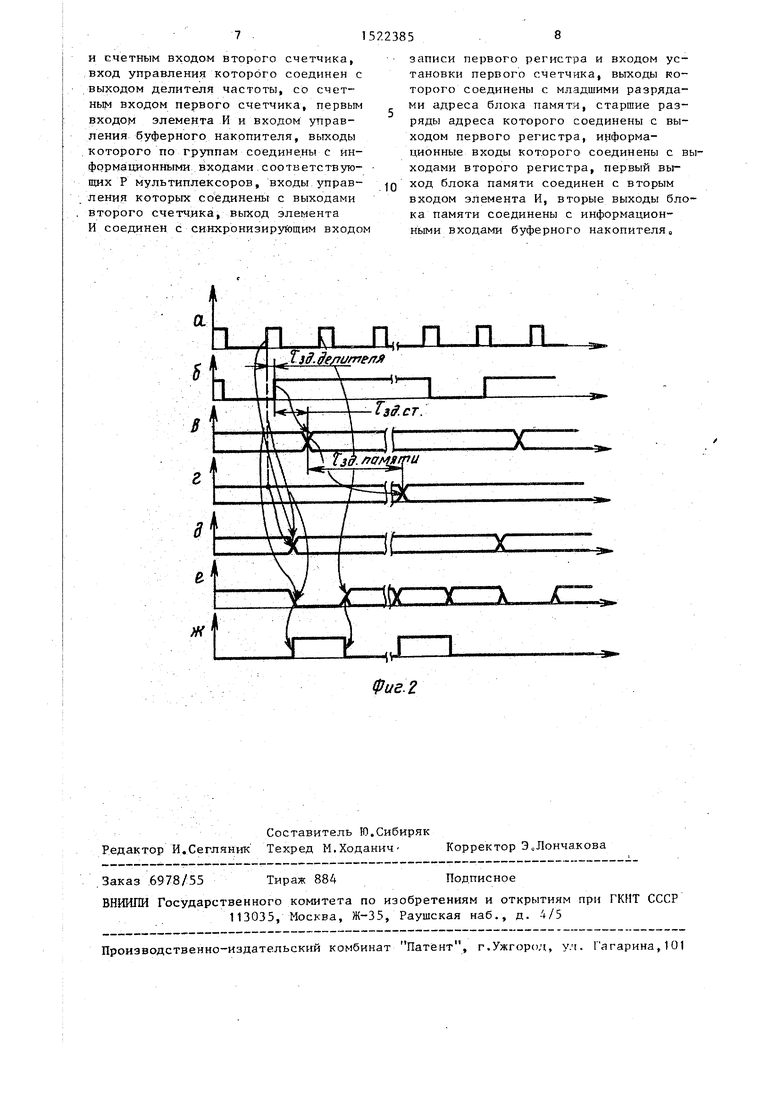

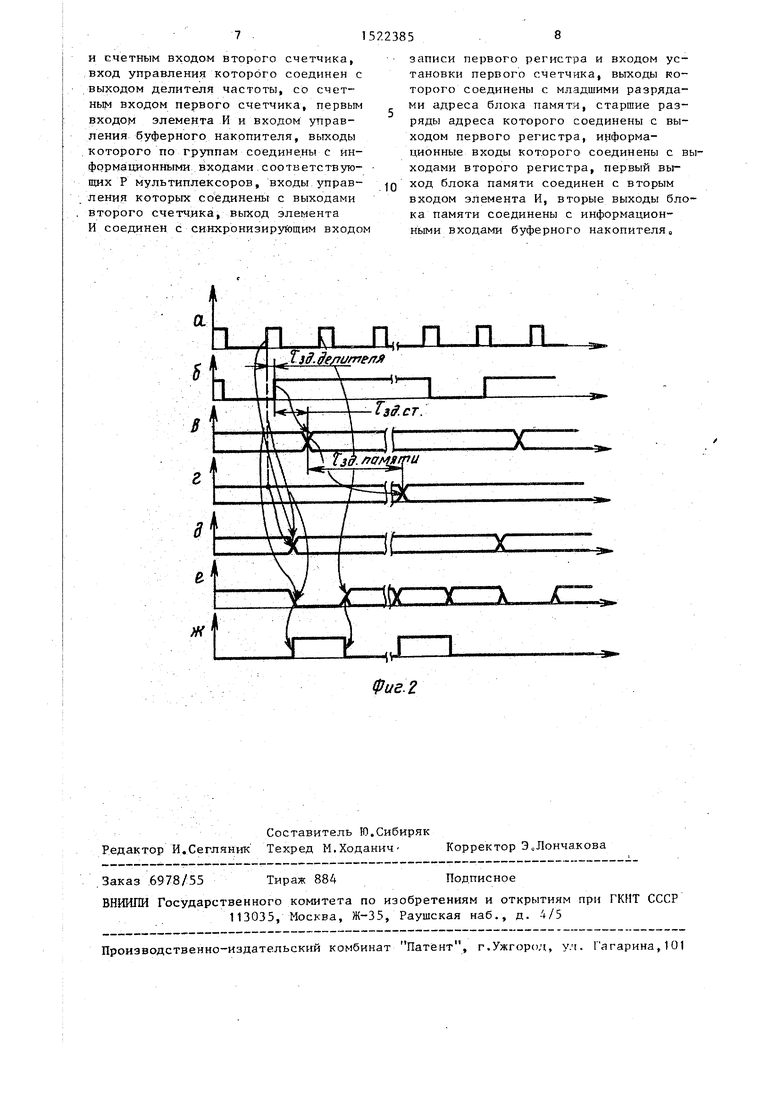

На фиг.1 представлена функциональная схема программируемого генератора импульсных последовательностей на фиг.2 - временная диаграмма, поясняющая работу устройства,

Программируемьш генератор импульс- нь.гх последовательностей содержит заающий генератор 1, делитель 2 час- оты, элемент ИЗ, счетчики 4 и 5, лок 6 памяти, буфернь:й накопитель 7, мультиплексоры 8-1,,,,,З-Р, регис т- ы 9 и 10.

Выход задающего генератора 1 сое-- инен с входом делителя 2 частоты, счетным входом счетчика 5 и с синхонизирующим входом буферного накопи- теля 7, Выход делителя 2 частоты, соеинен с входом управления буферного накопителя 7, счетным входом счетчика 4, входом управления сч.етчика 5 и первым входом элемента И 3, второй вход которого соединен с первым выходом блоа 6 памяти. Выход элемента ИЗ соеинен с синхронизирующим входом записи егистра 9 и входом обнуления счетчика 4, выходы которого соединены с млад-, ими разрядами адресу блока 6 памяти, старшие разряды адреса которого соеинены с выходами регистра 9, инфорационные входы которого соединены с выходами регистра 10. Вторые выходы блока 6 памяти соединены с информационными входами буферного накопителя 7, выходы которого соединены с информационными входами мультиплексоров 8-1,,.,8-Р, Входы управления мультиплексоров 8,1,.,.,8.Р соединены с вы ходами счетчика 15. Выходы мультиплексоров являются выходами устройства,

Делитель 2 частоты предназначен для формирования импульсов длительностью, равной периоду тактовой частоты (Ттакт) задающего генератора 1,

30

35

45

50

55

и то

л ны то ля хо

т л ч н с чи ин к од ва об

ны ду

ся во на мя

ни н на п ся вх р па бл ся бу О но де пл та на бу вы че

сы им да ра

0

5

0

5

0

5

5

0

5

и частотой , кратной тактовой частоте f (m - коэффициЕ .нт деления).

Счетчик 5 предназначен для управления мультиплексорами 8-1 , .... ,8-Р. Счетчик 5 осуществляет последовательный счет импульсов задающего генератора 1, а по сигналу с выхода делителя 2 частоты устанавливается в исходное нулевое состояние.

Для того, чтобы на выходах мультиплексоров 8-1, о.-. ,8-Р не происходило просечек сигнала, необходимо, чтобы запись информации в буферный накопитель 7 происходила синхронно с установкой в нулевое состояние счетчика 5, причем задержка появления информации на выходах буферного накопителя 7 и счетчика 5 должна быть одинаковой Чтобы выполнить это требование целесообразно использовать для обоих блоков одну элементную базу.

Программируемый генератор импульсных последовательностей работает следующим образом.

Перед началом работы производит-- ся программирование блока 6 памяти, регистра 10, устанавливаются в нулевое состояние счетчик 4 и буферный накопитель 7, производится запись информации выбранной области блока 6 памяти в регистр 9,из регистра J0.

Таким образом, в исходном состоянии на выходах счетчика 4 установлен нулевой код, на выходах регистра 9 находится код области памяти блока 6 памяти, из которой будет производится считывание информации. На адресных входах блока 6 памяти установлен адрес нулевой ячейки выбранной области памяти, в результате чего на выходах блока 6 памяти имеется код, хранящийся в этой ячейке памятио На выходах буферного накопителя 7 - логический О, Счетчик.5 находится в произвольном состоянии, его выходной код, воздействуя на входы управления мультиплексоров 8-1,,,ф,8-Р, вызывает коммутацию выходов буферного накопителя 7 на выходы устройства. Но поскольку буферный накопитель 7 обнулен, то на выходах устройства также сигнал логического нуля о

После запуска задающего генератора 1, вырабатывающего тактовые импульсы (фиг,2,а), счетчик 5 начинает счет импульсов, В результате на его выходах, а следовательно, и на входах управления мультиплексоров 8-1,,,,,8-Р

последовательно меняется код. Это приводит к тому, что на выходы мультиплексоров 8-),..,8-Р последовательно поступает информация с входов этих мультиплексоров. Однако, на выходах мультиплексоров 8-1,...,8-Р по-прежнему сохраняется сигнал логического О, поскольку буферный накопитель 7, сое- диненный своими выходами с информа- ционными входами мультиплексоров 8-1,о..,8-Р, обнулен. Это будет продолжаться до тех пор, пока на выходе делителя 2 частоты не появится им

56

выходах мультиплексоров 8-1,,..В-Р, т.е. шаг регулирования параметров выходного сигнала стал равньгм Т./т период частоты сигнала на выходе делителя 2 частоты).

С приходом очередного импульса с выхода делителя 2 частоты прсизойдет переключение в следующее состояние счетчика 4, а фронтом ближайшего импульса тактовой частоты - запись очередной информации в буферный накопитель 7 и установка в ноль счетчика 5. Далее процедура, описанная выше, пов

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1476533A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

Изобретение относится к импульсной технике и может быть использовано в вычислительной технике, системах управления и контроля. Цель изобретения - расширение диапазона регулирования параметров (периода, фазы, длительности импульса) формируемых импульсных последовательностей за счет уменьшения минимальных значений этих параметров - достигается введением мультиплексоров 8, время переключения которых меньше, чем время выборки информации из блока 6 памяти. Формирование импульсных последовательностей осуществляется за счет преобразования параллельного кода, хранящегося в буферном накопителе 7 и переписанного из блока 6 памяти, в последовательный код с помощью мультиплексоров 8, адреса управления для которых формируются счетчиком 5. Период смены информации в блоке 6 памяти задается делителем 2 частоты. Генератор также содержит задающий генератор 1, элемент И 3, счетчик 4, регистры 9, 10. 2 ил.

пульс, равный периоду частоты задающе-(5торится.

го генератора 1 и задержанный относи- Сигналом об окончании одного периотельно фронта тактового импульса нада кодовых посылок служит появление

время задержки делителя 2 частотылогической на первом вых,оде блока

ЗЛ.Дедителр (фиг.2,6). Этот импульс6 памяти, который открывает по перпереключит с задержкой 1 г ,счетчик20вому входу элемента И 3 и первым же 4 в следующее состояние (фиг.2,в)

(тем самым подготовит адрес следуюц1ей ячейки памяти из которой будет считываться информация, через время

импульсом с выхода делителя 2 частоты происходит обнуление счетчика 4 и запись в регистр 9 информации из регистра 10. Этот же импульс разрешает 25 запись в буферные накопитель 7 информации с последней ячейки выбранной области памяти блока 6 памяти и об- -нуление счетчика 5, т.е. осуществляется последний цикл вывода информации из выбранной области памяти.

5Д. nawjiT и

эта информация-появится

на выходах блока 6 памяти ( Фиг.2,г)) и, воздействуя на входы управления буферного накопителя 7 ;и счетчика 5, разрешит фронтом ближайшего тактового импульса одновременно записать в буферньй накопитель 7 инфор мацию, находящуюся на его информационных входах (фиг,2, е) В результате одновременно с выходов буферного накопителя 7 на информационные входы мультиплексоров 8-1,..о,8-Р поступит код, хранящийся в нулевой ячейке выбранной области , памяти, а на входы управления мультиплексоров 8-1,...,8-Р - код нулевого состояния счетчика 5. После этого счетчик 5 начнет счет импульсов тактовой частоты.:

Поскольку делитель 2 частоты осуществляет деление частоты задающего генератора 1 на т, то за период между двумя импульсами на выходе делителя 2 частоты на счетный вход счетчика 5 поступает m импульсов тактовой частоты, В результате за этот пе30

импульсом с выхода делителя 2 частоты происходит обнуление счетчика 4 и запись в регистр 9 информации из регистра 10. Этот же импульс разрешает 25 запись в буферные накопитель 7 информации с последней ячейки выбранной области памяти блока 6 памяти и об- -нуление счетчика 5, т.е. осуществляется последний цикл вывода информации из выбранной области памяти.

К моменту прихода следующего импульса с выхода делителя 2 частоты на выходах блока 6,памяти устанавливается информация, соответствующая адресу новой области памяти, есл информация в регистре 10 изменилась, и повторяется вывод информации из старой области памяти, если информация в регистре 10 не изменялась Соответственно в первом случае на выходах- генератора начнется формирование но- . вых кодовых посылок и повторится вывод старых - во втором.

35

40

д5 Формул а изобретения

Программируемый генератор импульсных последовательностей, содержащий задающий генератор, элемент И, первый счетчик, блок памяти, буферный нако- .рнод счетчик 5 будет принимать после- 50 г итель, отличающийся довательно состояние с О до т-1, что, тем, что, с целью расширения диапа- в свою очередь, приведет к тому, что зона регулирования параметров форми- на выходы мультиплексоров 8тI,,.,,8-Р руемой импульсной последовательное-.

тй, в него введены делитель частоты, Р мультиплексоров, второй счетчик, первый второй регистры, причем выход задающего генератора соединен с входом делителя частоты, синхронибудут последовательно коммутироваться сигналы с 1-го по т-й его информа- гс

ционных входов (фиг.2, диагр.ж). Значит за один период смень информации на выходах буферного накопителя 7 происходит m раз смена информации на

зирующим входом буферного накопителя

вому входу элемента И 3 и первым же

импульсом с выхода делителя 2 частоты происходит обнуление счетчика 4 и запись в регистр 9 информации из регистра 10. Этот же импульс разрешает запись в буферные накопитель 7 информации с последней ячейки выбранной области памяти блока 6 памяти и об- нуление счетчика 5, т.е. осуществляется последний цикл вывода информации из выбранной области памяти.

К моменту прихода следующего импульса с выхода делителя 2 частоты на выходах блока 6,памяти устанавливается информация, соответствующая адресу новой области памяти, есл информация в регистре 10 изменилась, и повторяется вывод информации из старой области памяти, если информация в регистре 10 не изменялась Соответственно в первом случае на выходах- генератора начнется формирование но- . вых кодовых посылок и повторится вывод старых - во втором.

зирующим входом буферного накопителя

и счетным входом второго счетчика, вход управления которого соединен с выходом делителя частоты, со счетным входом первого счетчика, первым входом элемента И и входом управления буферного накопителя, выходы которого по группам соединены с информационными входами соответствую- щих Р мультиплексоров, входы управления которых соединены с выходами второго счетчика, выход элемента И соединен с синхронизирующим входом

«U

записи первого регистра и входом установки первого счетчика, выходы которого соединены с младшими разрядами адреса блока памяти, старшие разряды адреса которого соединены с выходом первого регистра, и 1форма- ционные входы которого соединены с выходами второго регистра, первый вьг- ход блока памяти соединен с вторым входом элемента И, вторые выходы блока памяти соединены с информационными входами буферного накопителя

Фиг2

| Многоканальный программируемый генератор импульсов | 1981 |

|

SU1054894A1 |

Авторы

Даты

1989-11-15—Публикация

1987-06-12—Подача