(Л

с

Изобретение относится к вычисли тельной технике и. может быть использовано при построении арифметических устройств, работающих в двоичной зна- коразрядной системе счисления.

Цель изобретения - упрощение преобразователя,

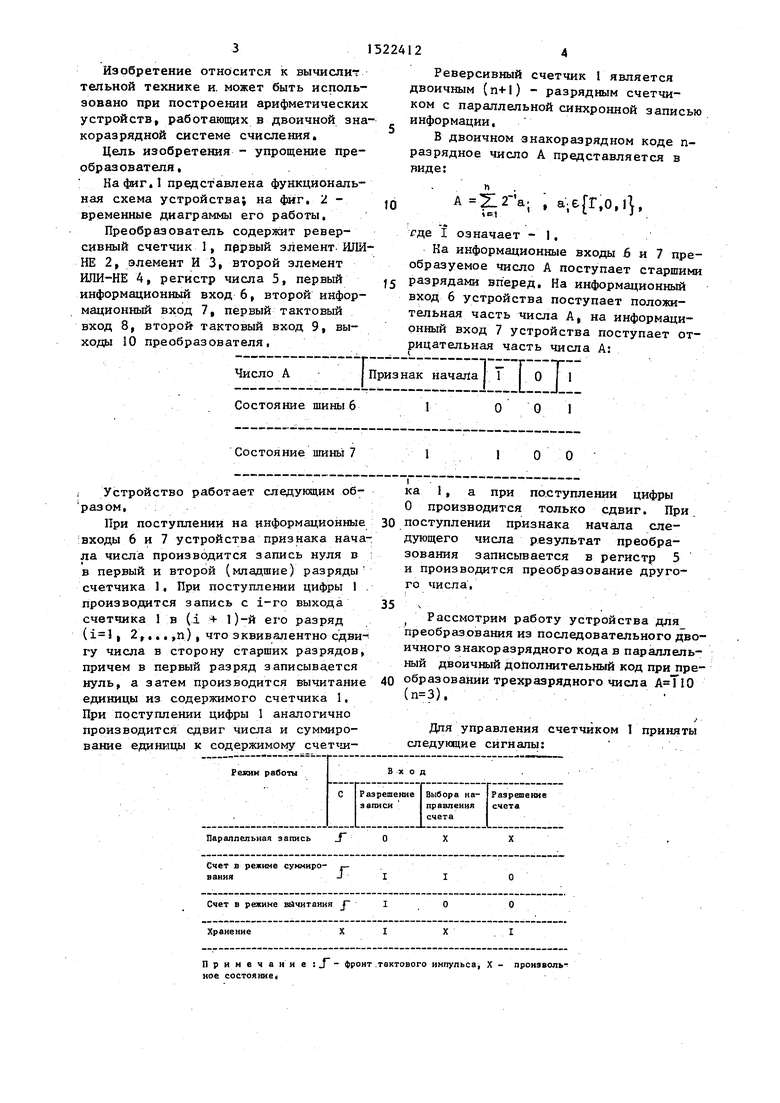

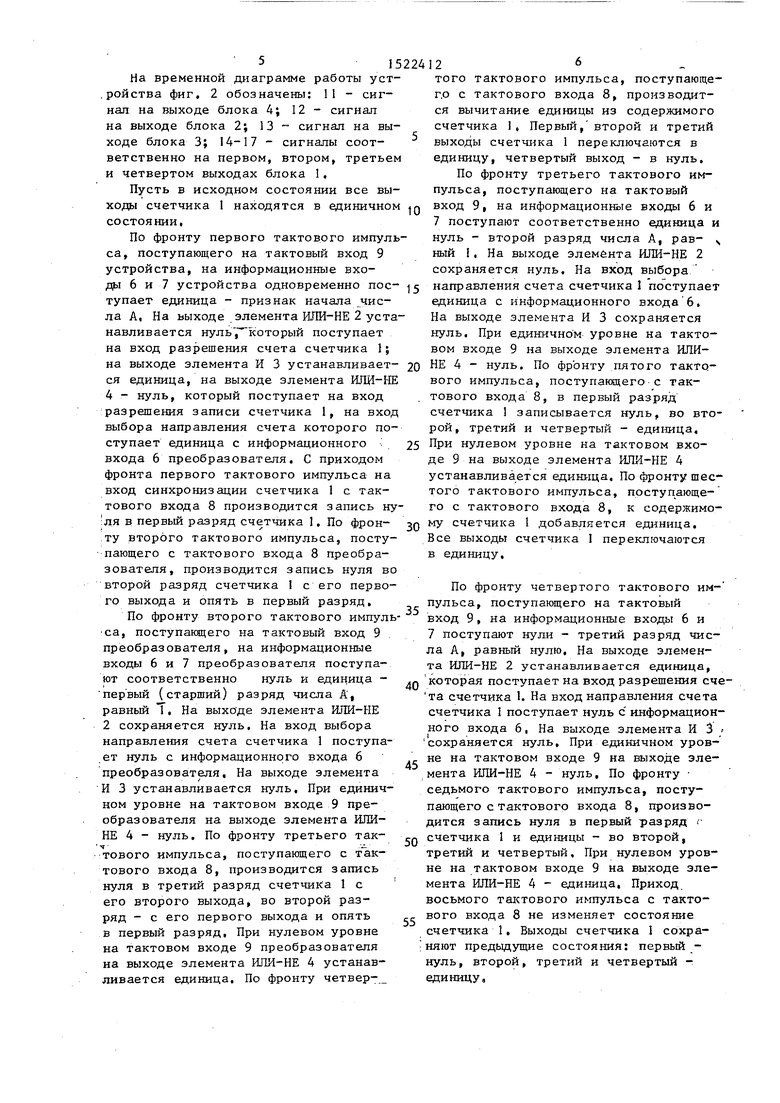

: На фиг.I представлена функциональная схема устройства; на фиг. 2. - временные диаграммы его работы.

Преобразователь содержит реверсивный счетчик I, первый элемент. ШШ- НЕ 2, элемент И 3, второй элемент ИЛИ-НЕ 4, регистр числа 5, первый информационный вход 6, второй информационный вход 7, первый тактовый вход 8, второй тактовый вход 9, выКа информационные входы образуемое число А поступа }5 разрядами вперед. На инфор вход 6 устройства поступае тельная часть числа А, на онный вход 7 устройства по

ходы 10 преобразователя,рицательная часть числа А:

Число А (Признак начала I 1 I О I

О I

1

Состояние шины 6

1

О

Реверсивный счетчик I является двоичным (п+1) - разрядным счетчиком с параллельной синхронной записью информации.

В двоичном знакоразрядном коде п- разрядное число А представляется в Риде:

10

ie1

,o,i,

где I означает - 1,

Ка информационные входы 6 и 7 преобразуемое число А поступает старшими разрядами вперед. На информационный вход 6 устройства поступает положительная часть числа А, на информационный вход 7 устройства поступает отрицательная часть числа А:

1

О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования последовательного кода в параллельный код | 1988 |

|

SU1501030A1 |

| Преобразователь кодов | 1986 |

|

SU1438008A1 |

| Преобразователь число-импульсного кода в параллельный двоичный код | 1984 |

|

SU1182685A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501276A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Динамический шифратор позиционного кода | 1988 |

|

SU1545328A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ЗНАКОРАЗРЯДНОГО КОДА В ДОПОЛНИТЕЛЬНЫЙ ДВОИЧНЫЙ КОД | 1990 |

|

RU2022337C1 |

| Преобразователь последовательного знакоразрядного кода в дополнительный двоичный код | 1983 |

|

SU1113796A1 |

| Преобразователь угол-код | 1987 |

|

SU1619398A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств, работающих в знакоразрядной системе счисления. Целью изобретения является упрощение преобразователя. Поставленная цель достигается за счет того, что в преобразователь, содержащий элемент И 3 и регистр числа 5, введены реверсивный счетчик 1 и элементы ИЛИ-НЕ 2, 4. 2 ил.

Состояние шинь 7

Устройство работает следующим об- разом, :

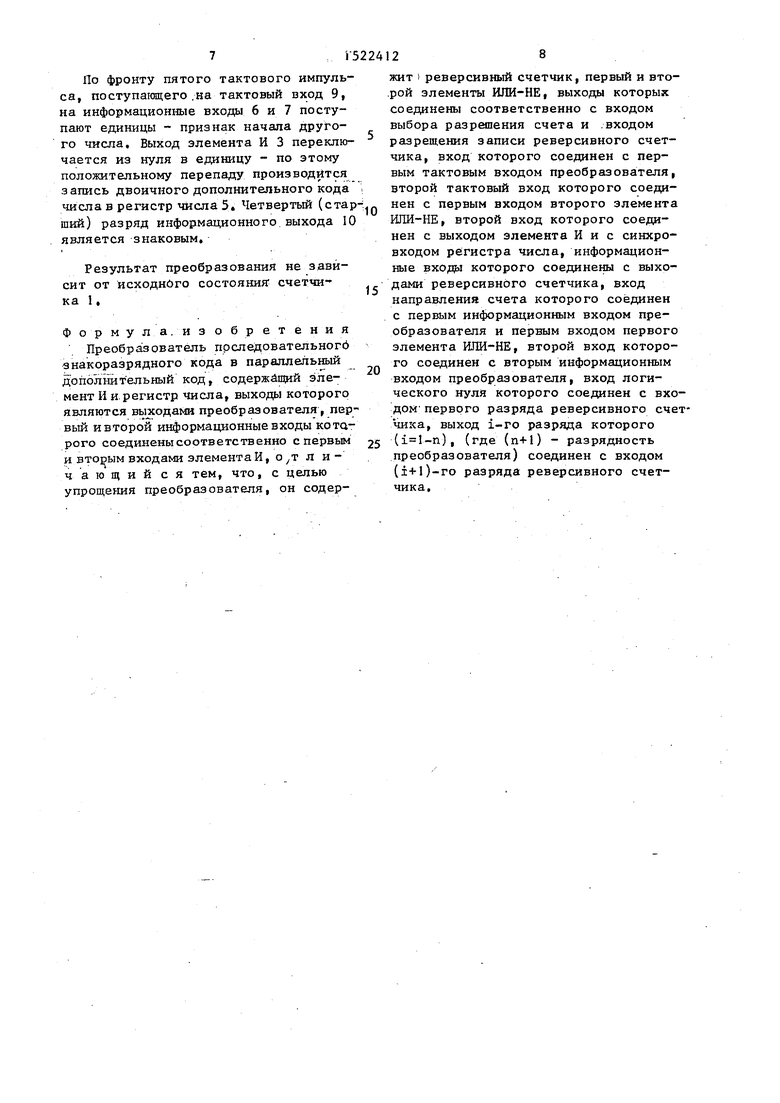

При поступлении на информационные ;входы 6 и 7 устройства признака начала числа производится запись нуля в в первый и второй (младшие) разряды счетчика 1. При поступлении цифры 1 производится запись с i-ro выхода счетчика 1 в (1 + 1)-й его разряд (, 2 .., ,п) , что эквивалентно сдвигу числа в сторону старших разрядов, причем в первый разряд записывается нуль, а затем производится вычитание единицы из содержимого счетчика 1, При поступлении цифры 1 аналогично производится сдвиг числа и суммирование единицы к содержимому счетчиСчет в режиме вйчитания

ХранениеXIX

Примечание фронт .тактового иипупьоа, X - проиэволь-: ное состояние

1

1

О О

ка 1 , а при поступлении цифры О производится только сдвиг. При поступлении признака начала следующего числа результат преобразования записывается в регистр 5 и производится преобразование другого числа,

ч . . Рассмотрим работу устройства для преобразования из последовательного двоичного знакоразрядного кода в параллельный двоичный дополнительный код при преобразовании трехразрядного числа (),..

/

Для управления счетчиком 1 приняты следующие сигналы: .

515

На временной диаграмме работы уст- .ройства фиг, 2 обозначены: 11 - CHI- нал на выходе блока 4; 12 - сигнал на выходе блока 2; 13 сигнал на выходе блока 3; 14-17 - сигналы соответственно на первом, втором, третьем и четвертом выходах блока 1.

Пусть в исходном состоянии все выходы счетчика 1 находятся в единичном состоянии.

По фронту первого тактового импульса, поступающего на тактовый вход 9 устройства, на информационные входы 6 и 7 устройства одновременно пос- тупает единица - признак начала .числа А, На выходе элемента ИЛИ-НЕ 2 устанавливается нуль , который поступает на вход разрешения счета счетчика 1; на выходе элемента И 3 устанавливает- ся единица, на выходе элемента ИОД-НЕ 4 - нуль, который поступает на вход разрешения записи счетчика 1, на вход выбора направления счета которого поступает единица с информационного входа 6 преобразователя, С приходом фронта первого тактового импульса на вход синхронизации счетчика 1 с тактового входа 8 производится запись ну ля в первый разряд счетчика 1, По фрон- ту второго тактового импульса, поступающего с тактового входа 8 преобразователя, производится запись нуля во второй разряд счетчика 1 с его первого выхода и опять в первый разряд.

По фронту второго тактового импуль са, поступаклцего на тактовый вход 9 преобразователя, на информационные входы 6 и 7 преобразователя поступают соответственно нуль и единица - первый (старший) разряд числа А , равный 1, На выходе элемента ИЛИ-НЕ 2 сохраняется нуль. На вход выбора направления счета счетчика 1 поступает нуль с информационного входа 6 преобразователя. На выходе элемента И 3 устанавливается нуль. При единичном уровне на тактовом входе 9 преобразователя на выходе элемента ИЛИ

НЕ 4 - нуль. По фронту третьего такiTOBoro импульса, поступающего с тактового входа 8, производится запись нуля в третий разряд счетчика 1 с его второго выхода, во второй разряд - с его первого выхода и опять в первый разряд. При нулевом уровне на тактовом входе 9 преобразователя на выходе элемента Ш1И-НЕ 4 устанавливается единица. По фронту четвер-

д

520 25 зо

5

0

5

0

с

126

того тактового импульса, поступающего с тактового входа 8, производится вычитание единицы из содержимого счетчика I, Первый, второй и третий выходы счетчика 1 переключаются в единицу, четвертый выход - в нуль.

По фронту третьего тактового импульса, поступающего на тактовый вход 9, на информационные входы 6 и 7 поступают соответственно единица и нуль - второй разряд числа А, рав- ный I, На выходе элемента ИЛИ-НЕ 2 сохраняется нуль. На вход выбора направления счета счетчика 1 поступает единица с информационного входа 6, На выходе элемента И 3 сохраняется нуль. При единичном уровне на тактовом входе 9 на выходе элемента ИЛИ- НЕ 4 - нуль. По фронту пятого тактового импульса, поступакщегос тактового входа 8, в первый разряд счетчика 1 записывается нуль, во второй, третий и четвертый - единица. При нулевом уровне на тактовом входе 9 на выходе элемента Ш1И-НЕ 4 устанавливается единица. По фронту шестого тактового импульса, поступающего с тактового входа 8, к содержимому счетчика 1 добавляется единица. Все выходы счетчика 1 переключаются в единицу.

По фронту четвертого тактового им- пульса, поступакщего на тактовый вход 9, на информационные входы 6 и 7 поступают нули - третий разряд числа А, равный нулю. На выходе элемента ИЛИ-НЕ 2 устанавливается единица, которая поступает на вход разрешения сче- та счетчика 1. На вход направления счета счетчика 1 поступает нуль с информационного входа 6, На выходе элемента И 3 сохраняется нуль. При единичном уровне на тактовом входе 9 на выходе элемента ИЛИ-НЕ 4 - нуль. По фронту седьмого тактового импульса, поступающего с тактового входа 8, производится запись нуля в первый разряд счетчика 1 и единицы - во второй, третий и четвертый. При нулевом уровне на тактовом входе 9 на выходе элемента ИЛИ-НЕ 4 - единица. Приход, восьмого тактового импульса с тактового входа 8 не изменяет состояние счетчика 1, Выходы счетчика 1 сохраняют предыдущие состояния: первый - нуль, второй, третий и четвертый - единицу.

По фронту пятого тактового импульса, поступающего .на тактовый вход 9, на информационные входы 6 и 7 поступают единицы - признак начала другого числа. Выход элемента И 3 переключается из нуля в единицу - по этому положительному перепаду производится запись двоичного дополнительного кода , числа в регистр числа 5. Четвертый (старший) разряд информационного.выхода 10 является знаковым.

Результат преобразования не зависит от исходного СОСТОЯНИЯ счетчика 1,

Формула, из обр ет ения Преобразователь прследовательногб знакоразрядного кода в параллельный дополнит ельный код, содержащий элемент И и регистр числа, выходы которого являются выходами преобразователя, первый и второй информационные в ходы кота- рого соединены соответственно с первым и вторым входами элементам, л и- чающий с я тем, что, с целью упрощения преобразователя, он содер

5

25

жит ) реверсивный счетчик, первый и вто- .рой элементы ИЛИ-НЕ, выходы которых соединены соответственно с входом выбора разрешения счета и .входом разрещения записи реверсивного счетчика, вход которого соединен с первым тактовым входом преобразователя, второй тактовый вход которого соединен с первым входом второго элемента ИПИ-НЕ, второй вход которого соединен с выходом элемента И и с синхро- входом регистра числа, информационные входы которого соединены с выходами реверсивного счетчика, вход направления счета которого соединен с первым информационным входом преобразователя и первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с вторым информационным входом преобразователя, вход логического нуля которого соединен с входом первого разряда реверсивного счетчика, выход i-го разряда которого ), (где (п+1) - разрядность преобразователя) соединен с входом (i+O-ro разряда реверсивного счетчика.

8

12345578

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь последовательногодВОичНОгО КВАзиКАНОНичЕСКОгО МОдифи-циРОВАННОгО КОдА B пАРАллЕльНыйКАНОНичЕСКий КОд | 1979 |

|

SU842785A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-15—Публикация

1988-02-19—Подача