fff

CAD

150

Изобретение спчктсится к нычисли- телыю технике и может исгю.чь.човать- ся при nocTpoeiniH арифметических устройств для преобрачсшяния пос. гедсша- тел1,ного двоичного зплкоратряджмч) хода в параллельный двспичный дополнительный код.

Целью изобретения является упрощение устройства.

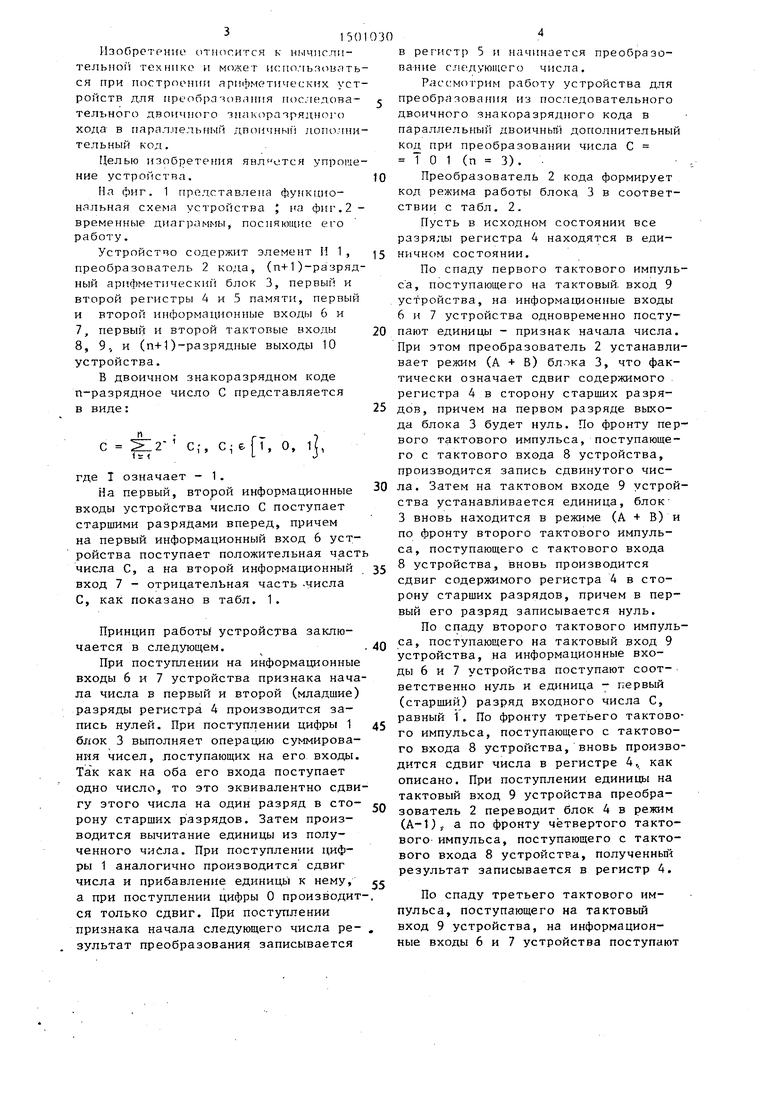

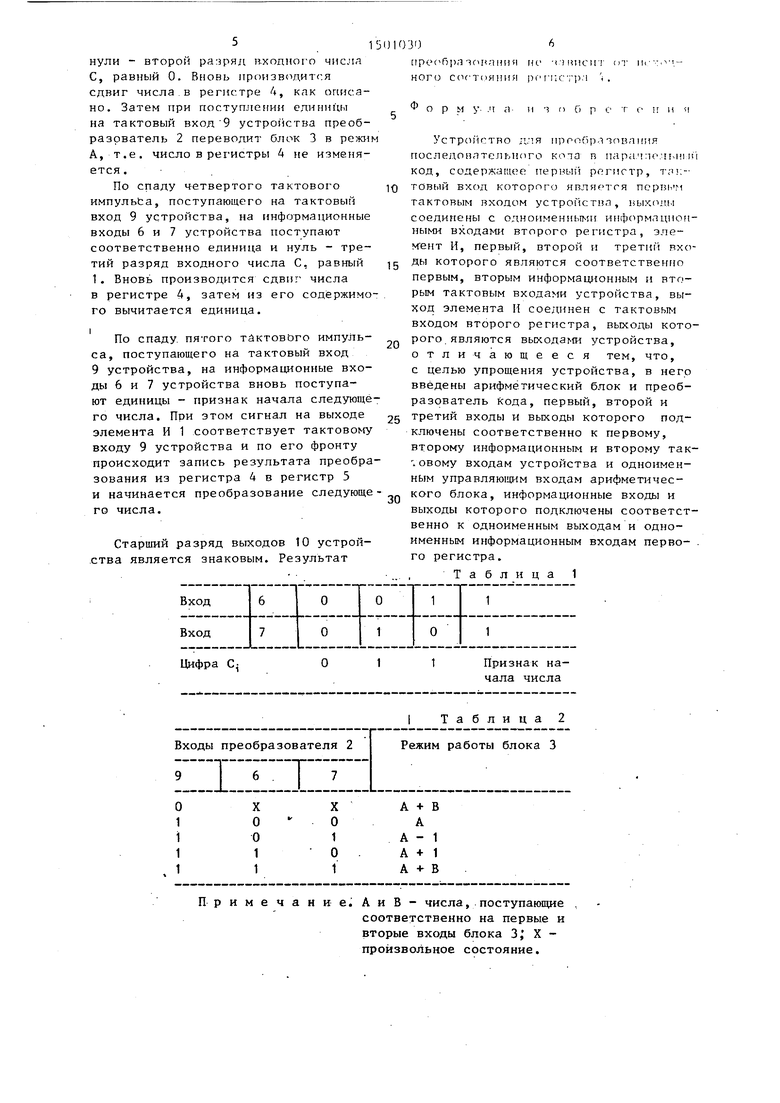

На фиг. 1 представлена функщю- нальная схема устройства ; на фиг.2- временные диаграммы посняющие его работу.

Устройство содержит элемент I 1 , преобразователь 2 кода, (п+1)-разряд- ный арифметически блок 3, первый и второй регистры 4 и 5 памяти, первый и второй информационные входы 6 и

7,первый н второй тактовые входы

8,9., и (п+1)разрядные выходы 10 устройства.

В двоичном знакоразрядном коде п-разрядное число С представляется в виде:

С

(t

С;, С е

Т. о, 1,

где I означает - 1.

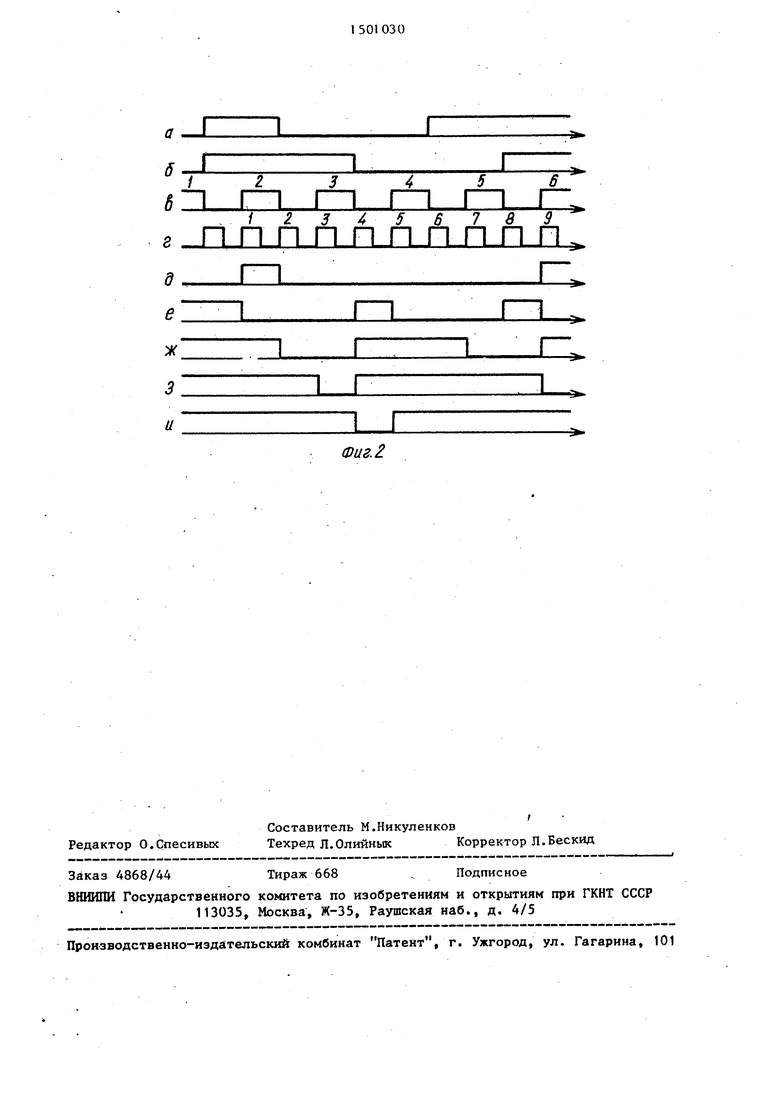

На первый, второй информационные входы устройства число С поступает старшими разрядами вперед, причем на первый информационный вход 6 устройства поступает положительная част числа С, а на второй информационный вход 7 - отрицательная часть -числа С, как показано в табл. 1.

Принцип работь устройства заключается в следующем.

При поступлении на информационные входы 6 и 7 устройства признака начала числа в первый и второй (младшие) разряды регистра 4 производится запись нулей. При поступлении цифры 1 блок 3 выполняет операцию суммирования чисел, поступающих на его входы. Та к как на оба его входа поступает одно число, то это эквивалентно сдвигу этого числа на один разряд в сторону старших разрядов. Затем производится вычитание единицы из полученного числа. При поступлении цифры 1 аналогично производится сдвиг числа и прибавление единицы к нему, а при поступлении цифры О производится только сдвиг. При поступлении признака начала следующего числа ре- зультат преобразования записывается

30

в регистр 5 и начинается преобразование с.пе-дующего числа.

Рлссмотрим работу устройства для преобразования из последовательного двоичного знакоразрядного кода в параллельный двоичньш дополнительный код при преобразовании числа С 1 О 1 (п 3). .

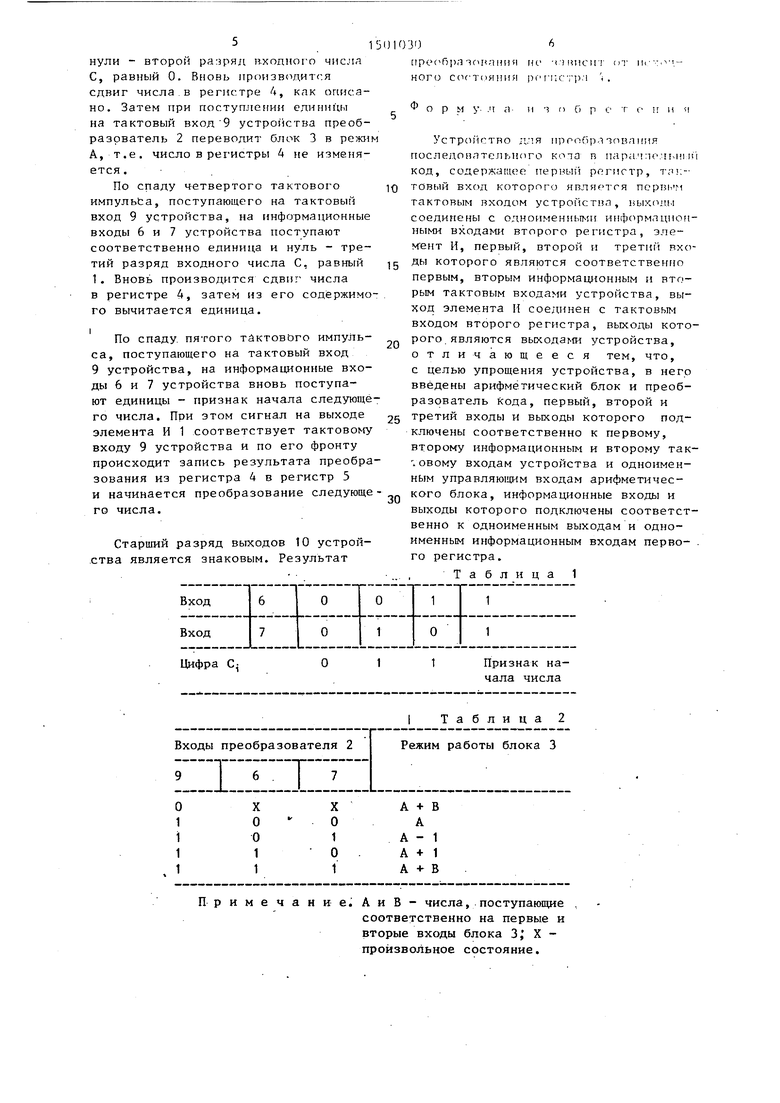

0 Преобразователь 2 кода формирует код режима работы блока 3 в соответствии с табл. 2.

Пусть в исходном состоянии все разряды регистра 4 находятся в еди5 ничном состоянии.

По спаду первого тактового импульса, поступающего на тактовый, вход 9 устройства, на информационные входы 6 и 7 устройства одновременно посту-

0 пают единицы - признак начала числа. При этом преобразователь 2 устанавливает режим (А + Б) блока 3, что фактически означает сдвиг содержимого регистра 4 в сторону старших разря5 дов, причем на первом разряде выхода блока 3 будет нуль. По фронту первого тактового импульса, поступающего с тактового входа 8 устройства, производится запись сдвинутого чис0 ла. Затем на тактовом входе 9 устройства устанавливается единица, блок 3 вновь находится в режиме (А + В) и по фронту второго тактового импульса, поступающего с тактового входа

5 устройства, вновь производится сдвиг содержимого регистра 4 в сторону старших разрядов, причем в первый его разряд записывается нуль.

По спаду второго тактового импульд са, поступающего на тактовый вход 9 устройства, на информационные входы 6 и 7 устройства поступают соответственно нуль и единица - первый (старший) разряд входного числа С, равный i. По фронту третьего тактового импульса, поступающего с тактового входа 8 устройства, вновь производится сдвиг числа в регистре 4,, как описано. При поступлении единицы на тактовый вход 9 устройства преобра0 зователь 2 переводит блок 4 в режим (А-1),. а по фронту четвертого тактового импульса, поступающего с тактового входа 8 устройства, полученньш результат записывается в регистр 4.

5

По спаду третьего тактового импульса, поступающего на тактовый вход 9 устройства, на информационные входы 6 и 7 устройства поступают

5

нули - второй ра:зряд и.ходног о числа С, равный 0. Вновь производится сдвиг числа.в регистре 4, как описано. Затем при поступлении единиц на тактовый вход 9 устройства преобразователь 2 переводит блок 3 в режи А, т.е. число в регистры 4 не изменяется. .

По спаду четвертого тактового импульЬа, поступающего на тактовый вход 9 устройства, на информационные входы 6 и 7 устройства поступают соответственно единица и нуль - третий разряд входного числа С. равный 1. Вновь производится сдвиг- числа в регистре 4, затем из его содержимого вычитается единица.

По спаду, пятого тактового импуЛь- са, поступающего на тактовый вход 9 устройства, на информационные входы 6 и 7 устройства вновь поступают единицы - признак начала следующего числа. При этом сигнал на выходе элемента И 1 соответствует TaKTOBONty входу 9 устройства и по его фронту происходит запись результата преобразования из регистра 4 в регистр 5 и начинается преобразование следующего числа.

Старший разряд выходов 10 устройства является знаковым. Результат

м

1 lit) 1030

|реоГ)1))иия гн- ччппспт

НОГО состояния )1Г Г-ПСТ). i

Ф

о р м

ч т п Г) р

т о и и ч

Устр(111стгю для прробр.повлиия последонятсл -Л пго кота п гтаралпол n l код, содержащей гтерньи регистр, т.-м;-- товый вход которого является псрпь м тактовым входом устройстоп, ныхолы соединены с oлнoимeнн 1 и информационными входами второго регистра, эле- м ент И, первый, второй и третий входы которого являются соответственно первым, вторым информационным м вторым тактовым входами устройства, выход элемента И соединен с тактовым входом второго регистра, выходы которого являются выходами устройства, отличающееся тем, что, с целью упрощения устройства, в негр введены арифметический блок и преобразователь кода, первый, второй и третий входы и выходы которого подключены соответственно к первому, второму информационным и второму тактовому входам устройства и одноименным управляю1и;им входам арифметического блока, информационные входы и выходы которого подключены соответственно к одноименным выходам и одноименным информационным входам парно- . го регистра.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного знакоразрядного кода в параллельный дополнительный код | 1988 |

|

SU1522412A1 |

| Преобразователь последовательного знакоразрядного кода в дополнительный двоичный код | 1983 |

|

SU1113796A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ЗНАКОРАЗРЯДНОГО КОДА В ДОПОЛНИТЕЛЬНЫЙ ДВОИЧНЫЙ КОД | 1990 |

|

RU2022337C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| Устройство для преобразования дополнительного двоичного кода в знакоразрядный | 1987 |

|

SU1496004A1 |

| Преобразователь кодов | 1987 |

|

SU1527715A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

Изобретение относится к вычислительной технике и может использоваться для преобразования последовательного двоичного знакоразрядного кода в параллельной двоичный дополнительный код. Цель изобретения - упрощение устройства. Устройство содержит элемент И 1, преобразователь 2 кода, арифметический блок 3, регистры 4, 5 памяти, информационные входы 6, 7, тактовые входы 8, 9 и выходы 10. 2 ил., 2 табл.

Примечание. АиВ- числа, поступаюпще

соответственно на первые и вторые входы блока 3, X - произвольное состояние.

Фиг. 2.

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь последовательногодВОичНОгО КВАзиКАНОНичЕСКОгО МОдифи-циРОВАННОгО КОдА B пАРАллЕльНыйКАНОНичЕСКий КОд | 1979 |

|

SU842785A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-23—Подача