Iff

сл to о сл сд

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке систем контроля программного обеспечения.

Цель изобретения - повышение достоверности контроля устройства.

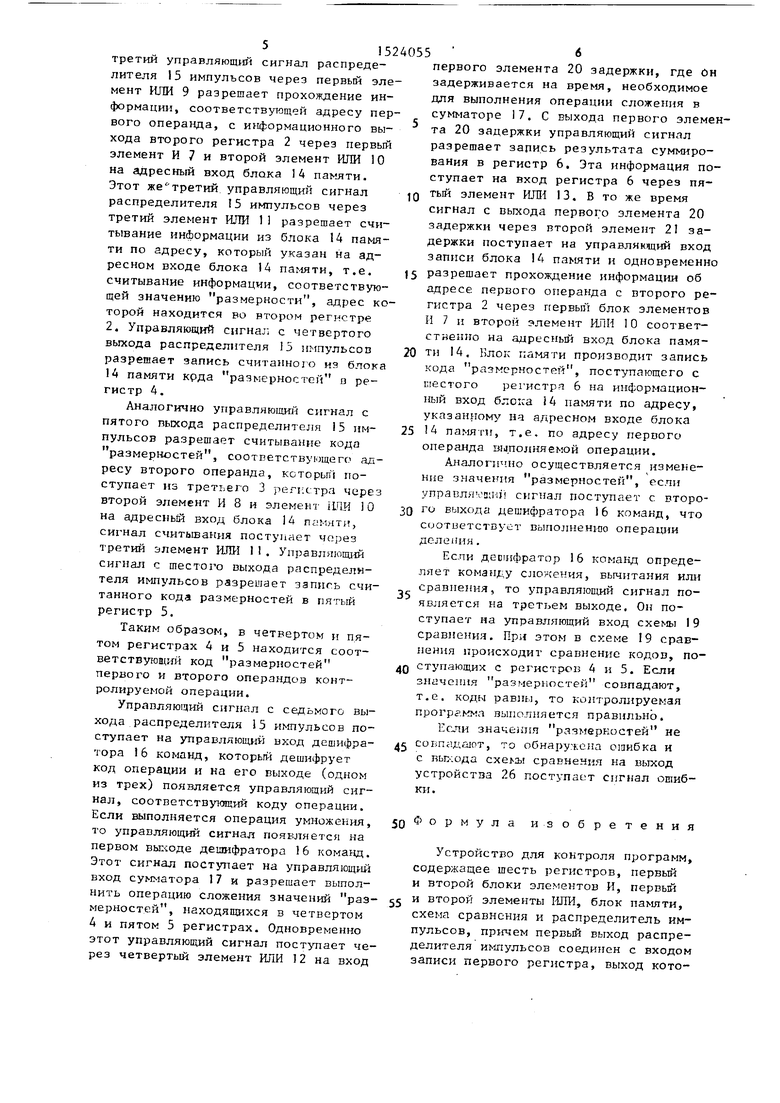

На чертеже изображено предлагаемое устройство.

Контроль правильности выполнения программы, основаннь1Й на проверке правильности ее информационных и управляющих связей между объектами программы в процессе выполнения, поясняется примером.

Пусть вьшолняется оператор присваивания

(Е+Т)/В.

Для корректно написанной программы в контексте данного оператора должны выполняться следующие соотношения между физичecкн ш размерностями величин (Р, А, С, Е, Т, В):

Cp A c3 Ali:c3; ,

Р (Е-ЬТ) /Б El Bj т В ; ,

где УС сризическая размернос ь объ

екта X.

Проверка правильности выполняемых соотношений по их размерностям и составляет сущность локализации ошибок при выполнении прогр гмшл. Значения размерностей определяются разработчиком или на этапе трансляции программы и пррдстазшяются числам. При проверке у1 нтывается, что для операций сложения, нычиташш, сравнения размерности операндов должны быт oдинaкoвы D, т.е. последовательность управляющих и информационных связей между объектами програмъ. выполняется правильно. Поэтому, при вы11олнен|-г ЭТ1ГХ операций для контроля правильности вьшолнения програмгш необходимо сравнивать значения размерностей соответствующих операвдов. Если значения размерностей совпадают, то программа выполняется правильно, есл не совпадают, то произошло нарушение по упрайляющим связям программы (для выполнения вовлечен какой-либо фрагмент программы из другого участка программы) или нарушение по информа ционным связям программы (для вьтол- нения операции выбран не тот объект программы). В процессе вьшолнения программы размерности внутренних

объектов программы (переменных) могут изменяться при вьтолнении операций сложения и деления. Поэтому при умножении и делении размерности операндов складываются и вычитаются соответственно .

Устройство для контроля хода программ содержит шесть регистров 1-6,

первый и второй блоки элементов И 7 и 8, первый - третий элементы ИЛИ 9-11, два блока элементов ИЛИ 12 и 13, блок 14 памяти, распределитель 15 импульсов, дешифратор 16 команд,

сумматор 17, блок 18 вычитания, схе- Miii 19 сравнения, первый и второй элементы задержки 20 и 21, тактовьй вход 22, ггервый, второй,третий информационные входы устройства 23-25,

Выход 26 ошибки устройства.

Дешифратор команд 16 имеет три В1):;ода. Первый выход соответствует «-дешифрации команды умножения, второй - деления, третий - сложения,

вычитания и сравнения.

Устройство работает следующим образом.

Перед началом работы устройства в память заносится информация, соот- петствующая выполняемой программе. Она представляет собой участок памяти контролируемой программы, в котором по адресам сходных, промежуточных и выходных объектов (переменных) программы занесены соответствующие значения размерностей, остальные ячейки памяти обнулены. Значения размерностей представлены в виде чисел, которые по соответствую- пшм правилам указываются разработчиком програьп-м или определяются автоматически с помощью специального транслятора. При готовности устрой- ства к работе на вход распределителя 15 импульсов начинают поступать сит налы с тактового входа 22 о том, что процессор подготовил к выполнению очередную команду, при этом на информационные входы устройства 23- 25 поступают.соответственно код операции, адреса первого и второго операндов. С первого, второго и третьего выходов распределителя 15 импульсов вьщаются последовательно управ

ляющие сигналы, разрешаю1цие запись информации с входов 24, 25 и .3 в первый 4, второй 3 и третий 2 регистры соответственно. Одновременно

51524055

третий управляющий сигнал распреде- первого элемента 20 задержки, где йн

лителя 15 импульсов через первый эле- задерживается на время, необходимое

для выполнения операции сложения в сумматоре 17. С выхода первого элемента 20 задержки управляющий сигнал разрешает варись результата суммиромент ИЛИ 9 разрешает прохождение информации, соответствующей адресу первого операнда, с информационного выхода второго регистра 2 через первый элемент И 7 и второй элемент ИЛИ 10 на адресный вход блока 14 . Этот же третий управляющий сигнал распределителя 5 иьтульсов через третий элемент ИЛИ 11 разрешает считывание информации из блока 14 памяти по адресу, который указан на адресном входе блока 14 памяти, т.е. считывание информации, соответствующей значению размерности, адрес которой находится во BTopoi-i регистре 2. Управляющий сигнал с четвертого выхода распределителя 15 импульсов разрешает запись считанного из блока 14 памяти крда размерностей а регистр 4.

Аналогично управляющий сигнал с пятого выхода распределителя 15 импульсов разрешает считывание кода размерностей, соответствующего адресу второго операнда, которьп поступает из третьего 3 регг.стра через второй элемент И 8 и элемент 1ШИ 10 на адресиьм вход блока 14 памяти, сигнал считывания поступает через третий элемент ИЛИ 11. Управляющий сигнал с шестого выхода распределителя импульсов разрешает запись считанного кода размерностей в пятый регистр 5.

Таким образом, в четвертом и пятом регистрах 4 и 5 находится соот- BeTCTByromirii код размерностей первого и второго операндов контролируемой операции.

Управляющий сигнал с сед.ьмого выхода , распределителя 15 импульсов по10

вания в регистр 6. Эта информация поступает на вход регистра 6 через пятый элемент ИЛИ 13. В то же время сигнал с выхода первого элемента 20 задержки через второй элемент 21 задержки поступает иа управляющий вход записи блока 14 памяти и одновременно

15 разрешает прохождение информации об адресе первого операнда с второго регистра 2 через первьш блок элементов И 7 и второй элемент ИЛИ 10 соответственно на адресный вход блока памя20 ти 14. Блок памяти производит запись кода размерностей, поступающего с KiecToro регистра 6 на информационный вход бло1са 14 памяти по адресу, указанному на адресном входе блока

25 4 памяти, т.е. по адресу первого операнда выполняемой операции.

Аналогично осуществляется измене- Hiie значения размерностей, если управля оз; сигнал поступает с второ30 го выхода дешифратора 16 команд, что соответствует выполненио операции деления.

Если дешифратор 16 команд определяет команду сложения, вычитания или сравнения, то управляющий сигнал появляется на третьем выходе. Он поступает на управляющий вход схемы I9 сравнения. При этом в схеме 19 сравнения происходит сравнение кодов, по40 ступающих с регистрО2з 4 и 5. Если значения размерностей совпадают, т.е. коды равны, то контролируемая nporpaMt.a выполняется правильно. Если значения размерностей не

0

вания в регистр 6. Эта информация поступает на вход регистра 6 через пятый элемент ИЛИ 13. В то же время сигнал с выхода первого элемента 20 задержки через второй элемент 21 задержки поступает иа управляющий вход записи блока 14 памяти и одновременно

5 разрешает прохождение информации об адресе первого операнда с второго регистра 2 через первьш блок элементов И 7 и второй элемент ИЛИ 10 соответственно на адресный вход блока памя0 ти 14. Блок памяти производит запись кода размерностей, поступающего с KiecToro регистра 6 на информационный вход бло1са 14 памяти по адресу, указанному на адресном входе блока

5 4 памяти, т.е. по адресу первого операнда выполняемой операции.

Аналогично осуществляется измене- Hiie значения размерностей, если управля оз; сигнал поступает с второ0 го выхода дешифратора 16 команд, что соответствует выполненио операции деления.

Если дешифратор 16 команд определяет команду сложения, вычитания или сравнения, то управляющий сигнал появляется на третьем выходе. Он поступает на управляющий вход схемы I9 сравнения. При этом в схеме 19 сравнения происходит сравнение кодов, по0 ступающих с регистрО2з 4 и 5. Если значения размерностей совпадают, т.е. коды равны, то контролируемая nporpaMt.a выполняется правильно. Если значения размерностей не

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для группового управления лифтами | 1982 |

|

SU1089024A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1233149A1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке систем контроля программного обеспечения. Устройство содержит регистры 1 - 6, блоки 7 и 8 элементов И, элементы ИЛИ 9 - 13, блок 19 сравнения, блок 14 памяти, дешифратор 16 команд, распределитель 15 импульсов, сумматор 17, блок 18 вычитания, элементы 20 и 21 задержки. Изобретение позволяет повысить достоверность контроля программ за счет контроля правильности выполнения программы по управляющим и информационным связям. Правильность выполнения программы определяется на основании контроля "размерностей" операндов контролируемой операции, которые задаются разработчиком программы или определяются на этапе трансляции. "размерности" представляются числами. При проверке учитывается, что для операций сложения, вычитания и сравнения "размерности" операндов должны быть одинаковыми, т.е. последовательность управляющих и информационных связей между объектами программы выполняется правильно. 1 ил.

ступает на управляющий вход дешифра- дЗ совпадщот, то обнаружена ошибка и

тора 16 команд, который дешифрует код операции и на его выходе (одном из трех) появляется управляющий сигнал, соответствующий коду операции, Если выполняется операция умножения, то управляющий сигнал появляется на первом вы: соде дешифратора 16 команд. Этот сигнал поступает на управляющий вход сумматора 17 и разрешает выполнить операцию сложения значений размерностей, находящихся в четвертом 4 и пятом 5 регистрах. Одновременно этот управляющий сигнал поступает через четвертый элемент ИЛИ 12 на вход

50

с вьп-:ода схем сравнения на выход устройства 26 поступает сигнал оши ки.

Формула изобретени

Устройство для контроля програм содержащее шесть регистров, первый и второй блоки элементов И, первьй ее и второй элементы 1-ШИ, блок памяти схема сравнения и распределитель и пульсов, пр1гчем первьй выход распр делителя импульсов соединен с вход записи первого регистра, выход кот

50

с вьп-:ода схем сравнения на выход устройства 26 поступает сигнал ошибки.

Формула изобретения

Устройство для контроля программ, содержащее шесть регистров, первый и второй блоки элементов И, первьй и второй элементы 1-ШИ, блок памяти, схема сравнения и распределитель импульсов, пр1гчем первьй выход распределителя импульсов соединен с входом записи первого регистра, выход кото

рого соединен с первым входом первого элемента И, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены третий элемент ИЛИ и два блока элементов ИЛИ, дешифратор команд, сумматор, блок вычитания, первый и второй элементы задержки, причем входы адреса первого и второго операндов и кода операции устройства соединены с информационными входами соответственно первого, второго и третьего регистров, вход синхронизации устройства соединен с тактовым входом распределителя импульсов, второй выхо которого соединен с входом записи третьего регистра, выход которого соединен с входом д егаифратора команд, третий выход распределителя импульсов соединен с входом записи второго регистра, с первым входом первого элемента ИЛИ, выход которого соединен с вторым входом первого блока элементов И, выход которого соединен с первым входом первого блока элементов ИЛИ, третий, четвертый, пятый, шестой и седьмой выходы распределителя импульсов соединены соответственно с первым входом вторюго элемента ИЛИ, с входом записи четвертого регистра, с вторьм входом второго элемента ИЛИ, с входом записи пятого регистра и с тактовым входом дептфра- тора команд, первый, второй и третий выходы которого соединены соответственно с первьи входом третьего элемента ИЛИ, с вторым входом третьего элемента ИЛИ и с тактовым входом схемы сравнения, пятьй выход распреде-

5 п

0

5

0

5

лителя импульсов соединен с управляющим входом второго блока элементов И, выход которого соединен с вторым входом первого блока элементов ИЛИ, выход которого соединен с адресным входом блока памяти, выход второго регистра соединен с информационным : входом второго блока элементов И, выход второго элемента ИЛИ соединен с входом чтения блока памяти, информационный выход которого соединен с ин- формацио нными входами четвертого и пятого регистров, выход третьего элемента ИЛИ соединен через первый элемент задержки с входом записи шестого регистраjC вторым входом первого элемента ИЛИ и через второй элемент задержки с входом записи блока памяти, выход четвертого регистра соединен с входом первого операнда сумматора, с входом первого операнда блока вычитания и с первым входом схемы сравнения, выход которой является выходом ошибки устройства, выход пятого регистра соединен с вторым входом схемы сравнения, с входом второго операнда блока вычита иия и с входом второго операнда суьдаатора, выход которого соединен с первым входом второго блока элементов ИЛИ, первый и второй выходы дешифратора команд соединены с тахтовьш входом сумматора и с тактовый входом блока вычитания, выход которого соедцниен с вторым входом второго блока элементов ШШ, выход которого соединен с ин- формационньм входом шестого регистра, выход которого соединен с информаци онным входом блока памяти.

| Устройство для контроля программ и микропрограмм | 1983 |

|

SU1176334A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля хода программ | 1979 |

|

SU983712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-23—Публикация

1988-03-09—Подача