Изобретение относится к вычислительной технике и предназначено для построения специализированных вычислительных средств.

Цель изобретения - уменьшение аппаратных затрат./

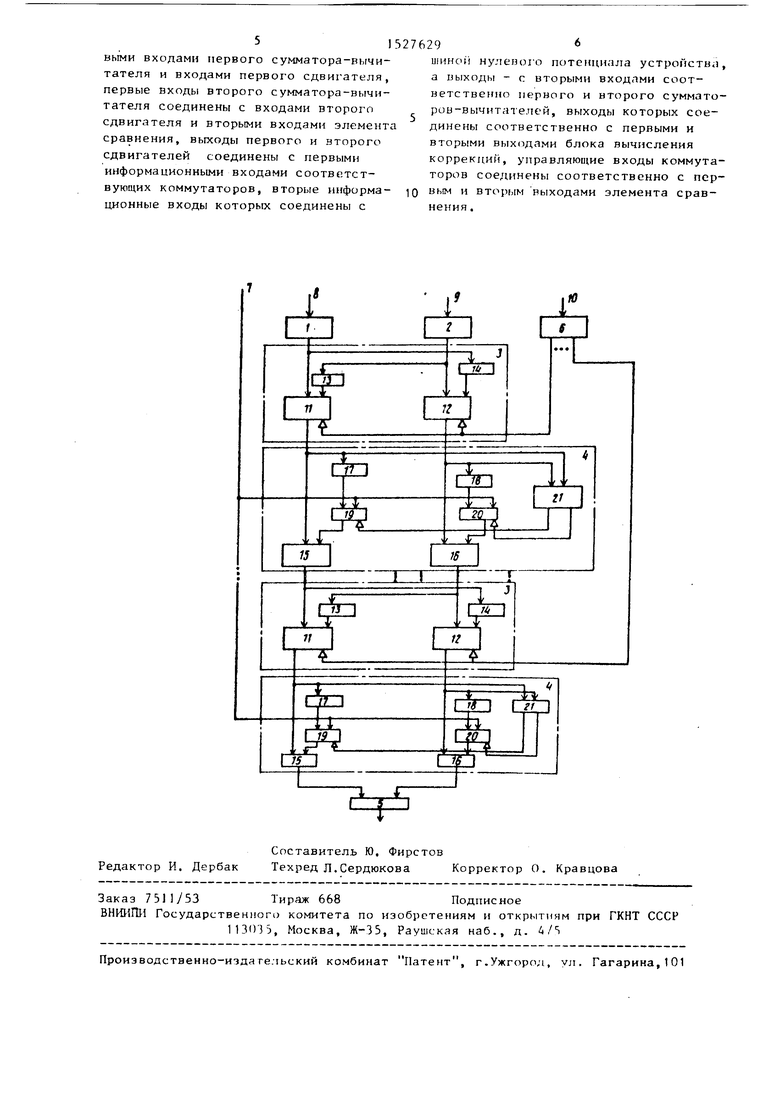

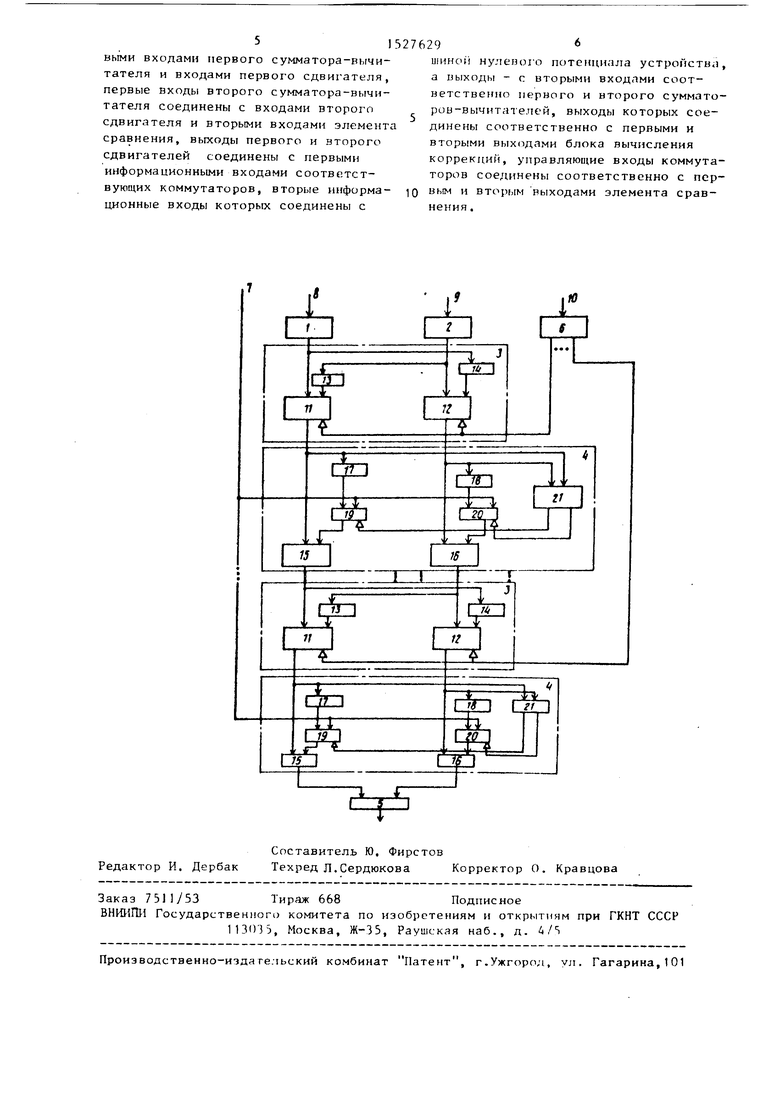

На чертеже представлена структур- 1ная схема устройства.

Устройство содержит первый 1 и второй 2 регистры, блоки вычисления итераций 3 и коррекций 4, сумматор- накопитель 5, блок 6 постоянной памяти, общую шину 7, входы множимого 8 и множителя 9, входы 10 значений угла поворота. Число блоков 3 и 4 определяется необходимым числом итераций для получения заданной точности вычислений.

Блок вычисления итераций содержит сумматоры-вычитатели 11 и 12 и сдви- гатели 13 и 14.

Блок вычисления коррекции содержит сумматоры-вычитатели 15 и J6, сдви- гатели 17 и 18, коммутаторы J9 и 20 и элемент 21 сравнения.

Устройство работает следующим образом.

В регистры и 2 заносятся числа, соответствующие модулям перемножаемых векторов.

Операция осуществляется в соответствии с алгоритмом Волдера.

Для умножения вектора с координатами (а,, Ь) на вектор с координатами (а, Ь) в начале определяется

О1

ю

05

ю

3

угол б arctg(,2.). Затем выполняе операция Поворот вектора х(а, Ь

Значения тангенса угла поворота вычисляются заранее и подаются на в блока 6 постоянной памяти. В регистры 1 и 2 записываются значения модулей (длин) векторов х и у. При это каждый блок вычисления итераций осуществляет над входными данными one- рацию

х; , ; ,+ ;х;2- ,

где f; i1, а , 1, ..., n-1 - нмер блока, соответствующий номеру итерации.

Коэффициенты ; являются значенями функции, указывающей угол поворота вектора, вычисляются заранее и хранятся в блоке 6 постоянной памят

Блоки 4 вычисления коррекций осуществляют коррекцию изменения длины вектора результата, происходящую пр вычислении согласно указанному итерционному алгоритму. Блоки вычислени коррекций осуществляют операцию деления в итерационной форме.

Каждый блок 4 выполняет операцию

л о - х,4, х; -G;x; 2 . ;

у;., yi.-G;y.;2- ,

где Х;И у ; - значения данных на входе блока

0при x t у ,

1при х у.; ,

На первые входы сумматоров-вычита телей 11 и 12 поступают коды чисел и регистров 1 и 2, а на вторые входы сумматоров-вычитателей через сдвига- тели 14 и 13 - коды чисел с выходов регистров 1 и 2, сдвинутые на один разряд вправо.

Настройка сумматоров-вычитателей 11, 2 на проведение операций суммирования или вычитания осуществляется сигналами с выхода блока 6 постоянной памяти. Значение управляющего сигнала определяется кодом значения угла поворота, поступающим на адресные входы блока 6 по шине 10. Остальные блоки вьгчис:1ения итераций функционируют аналогично. В каждом блоке вычисления итераций 3 осуществляется в соответствии с приведенным алгоритмом одна итерация поворота вектора. Данные с выходов сумматоров вычитателей 11 и 12 поступают на выходы блока 3 и на входы первого блока 4 коррекции, н проияиодит ся анулиронание деформации иектора

при повороте вектора в первой ите- рации.

Данные х , у с выходов сумматоров 11 и 12 поступают соответственно на первые выходы сумматоров-вычитателей 15 и 16, а также на входы сдвигателей 17 и 18, осуществляющих сдвиг на один разряд влево (умножение на ). На первые входы коммутаторов 19 и 20 поступают величины х 2 и у . , на иторые входы- нулевой потенциал с шины 7. Управление коммутаторами 19 и 20 осуществляется по значению сигнала или 1 на выходе блока 21 сравнения, вырабатываемого при сравнении величин ( I

X ; И у. ,

Результаты с выхода последнего блока вычисления Коррекций суммируются в сумматоре-накопителе 5.

Формула изобретения

5

5

0

5

0

5

Устройство для вычисления сумм произведений, содержащее сумматор- накопитель, блоки вычисления итераций, блоки вычислений коррекций, блок постоянной памяти, первый и Q второй регистры, информационные входы которых соединены coofBeTCTBeH- но с входами .множимого и множителя устройства, выходы регистров соединены с соответствующими входами первого блока вычисления итераций, выходы каждого блока вычисления итераций соединены с входами соответствующего блока вычисления коррекций, выходы цоследнего блока вычисления коррекций соединены с входами сумматора-накопителя, выходы каждого блока вычисления коррекций соединены с входами последующего блока вычисления итерап,ий, управляющие входы которых соединены с выходами блока постоянной памяти, входы которого соединены с входами значений угла поворота устройства, каждый блок вычисления коррекций содержит первый и второй сумматоры-вычитатели, первые входы которых соединены с соответствующими выходами соответствующего блока вычисления итераций, отличающееся тем, что, с целью уменьшения аппаратных затрат, каждый блок вычисления коррекций содержит первый и В1орой сднигатели, первый и второй Коммутаторы, элемент сравнения, ггер- ние входы которого соединены с первыми входами первого сумматора-вычи- тателя и входами первого сдвигателя, первые входы второго сумматора-вычн- тателя соединены с входами второго сдвигателя и вторыми входами элемент сравнения, выходы первого и второго сдвигателей соединены с первыми информационными входами соответствующих коммутаторов, вторые информационные входы которых соединены с

шинсч нулевого потенциала устройства, а выходы - с вторыми входами соответственно первого и второго суммато- ров-вычитателей, выходы которых соединены соответственно с первыми и вторыми выходами блока вычисления коррекций, управляющие входы коммутаторов соединены соответственно с первым и вторым выходами элемента сравнения .

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1476462A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Вычислительное устройство для поворота вектора | 1979 |

|

SU857979A1 |

| Устройство для извлечения квадратного корня и его обратной величины | 1988 |

|

SU1545218A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для поворота вектора с коррекцией | 1980 |

|

SU951299A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Цифровой вычислитель обратного гиперболического тангенса | 1978 |

|

SU698002A1 |

Изобретение относится к вычислительной технике и предназначено для построения специализированных вычислительных средств. Цель изобретения - сокращение аппаратных затрат. Для достижения поставленной цели устройство содержит соединенные последовательно блоки вычисления итераций и вычисления коррекций. Уменьшение аппаратных затрат достигается за счет многосекционного построения блока вычисления коррекции, осуществляющего итерационную операцию деления путем последовательных приближений. 1 ил.

| Andreus М | |||

| et al | |||

| А pipelined computer architecture for unified elementary function evalnation computer.-Elect | |||

| Eng., 1978, V | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кран машиниста для автоматических тормозов с сжатым воздухом | 1921 |

|

SU194A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-07—Публикация

1987-11-30—Подача