Изобретение относится к- вычислительной технике и может найти применение при разработке устройств с встроенным контролем.

Цель изобретения - повышение быстродействия.

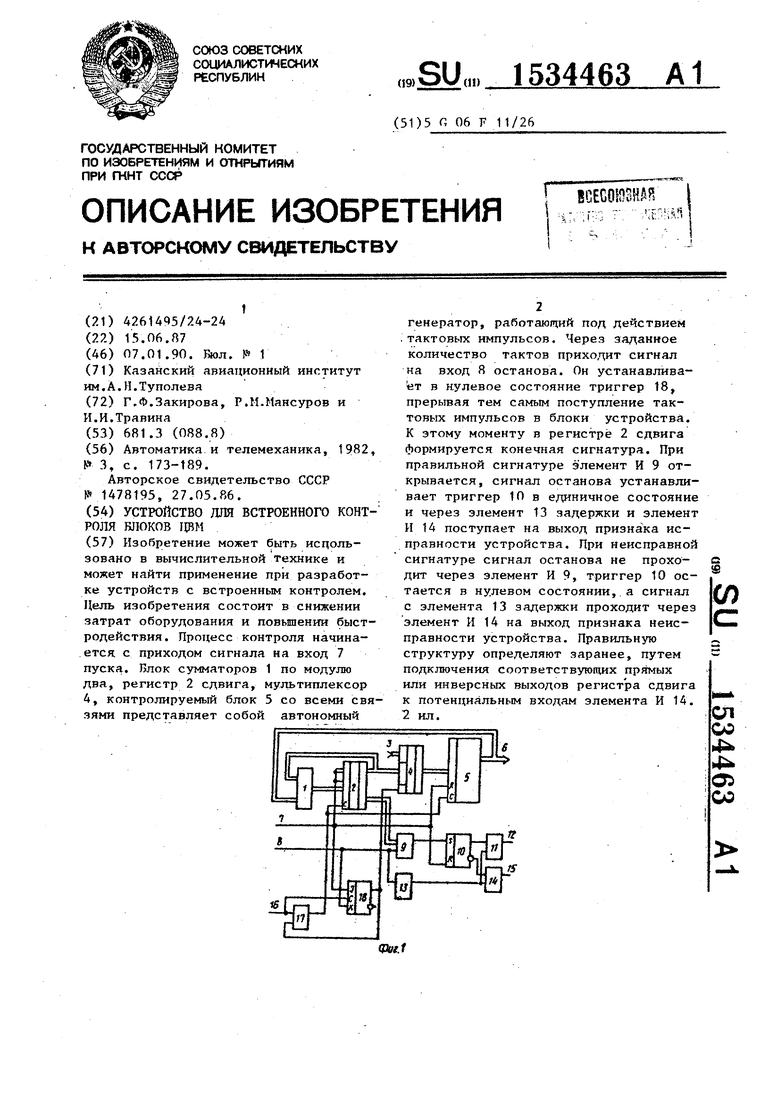

На фиг.1 представлена функциональная схема устройства, на фиг.2 - временная диаграмма работы устройства для случая исправного контролируемого

блока.

Устройство содержит блок 1 сумматоров по модулю два, регистр 2 сдвига, группу входов 3 рабочего воздействия, мультиплексор 4, контролируемый блок 5, группу тестовых входов 6 устройства, вход 7 пуска, вход 8 останова, элемент И 9., триггер Ю, элемент И 11 выход 12 признака исправности уст- ройства, элемент 13 задержки, элемент И 14, выход 15 признака неисправности устройства, тактовый вход 16, элемент И 17 и триггер 18.

Устройства работает в двух режи- мах: рабочем и контрольном.

До тех пор, пока с входа 7 не поступит сигнал начала контроля, устройство находится в рабочем режиме, т.е. контролируемый блок 5 с помощью муль- типлексора 4 через группу входов 3 и группу входов 6 устройства подключен к вычислительной машине, элементом которой он является.

Контрольный режим реализуется следукмчим образом. На вход 7 приходит сигнал начала контроля. Этот сигнал устанавливает регистр 2 и контролируемый блок 5 в начальное состояние, триггер 18 в единичное состояние и триггер 10 в нулевое состояние. Единичный сигнал с выхода триггера 18 поступает на управляющий вход мультиплексора 4, вследствие чего контролируемый блок 5 отключается от вычисли- тельной машины и подключается к устройству контроля. Одновременно единичный сигнал триггера 18 открывает элемент И 17, вследствие чего импульсы с тактового входа 16 начинают посту

пать на синхровходы контролируемого блока 5 и регистра 2,инициируя их работу.

Регистр 2, блок 1, мультиплексор 4, контролируемый блок 5 вместе с указанными связями представляют собой авто номный генератор, работающий под действием тактовых импульсов. Двоичные числа, порождаемые этим автономным

- Ь

JQ

5, 20

25

Q

... д35

, 50

Ь5

генератором с первой группы разрядных выходов регистра 2, образованной пря- мыми выходами разрядов, поступают на первую группу входов блока 1 и на вторую группу входов мультиплексора 4, с входов которого поступают на входы контролируемого блока 5. Реакции контролируемого блока 5 в виде двоичных чисел поступают на вторую группу входов блока 1, учавствуя тем самым в формировании очередного тестового числа в регистре 2. Таким образом, регистр 1 представляет собой сигнатурный анализатор, сжимающий выходную информацию контролируемого блока 5. Через заданное количество тактов приходит сигнал на вход 8. Он устанавливает триггер 18 в нулевое состояние, прерывая тем самым поступление тактовых импульсов в блоки устройства, и приходит на вход элемента И 9. К этому моменту в регистре 2 сформирована конечная сигнатура. При правильной сигнатуре в регистре 2 элемент И 9 открыт и сигнал с входа 8 устанавливает триггер 10 в единичное состояние. Через некоторое время, определяемое элементом 13, этот же сигнал проходит через элемент И 11 и поступает на выход 12 признака исправности устройства.

При неправильной сигнатуре сигнал с входа 8 не проходит через элемент И 9, триггер 10 остается в нулевом состоянии, и сигнал с выхода элемента 13 проходит через открытый элемент И 14 на выход 15 признака неисправ- ности устройства. Правильная сигнатура определяется заранее, например, путем моделирования. Поэтому вторая группа разрядных выходов регистра 2, подключенная к группе входов элемента И 9, формируется следующим образом: на соответствующий вход элемента И 9 подается прямой выход соответствующего разряда регистра 2, если в данном разряде ожидается единичный бит сигнатуры, и наоборот, к входу элемента И 9 подключен инверсный выход соответствующего разряда, если в данном разряде ожидается нулевой бит сигнатуры. Таким образом, при правильной конечной сигнатуре на группу входов элемента И 9 будут поданы разрешающие единичные потенциалы.

51

Формула изобретения Угтройстно дня встроенного контроля блоков ЦВМ, содержащее блок сумматоров по модулю два, регистр гдпига, мультиплексор, первый элемент И, первый триггер, отличающееся тем, что, с целью повышения быстродей ствия, в него введены второй, третий и четвертый элементы И. второй триггер, элемент задержки, причем информационные выходы мультиплексора соеди йены с выходами устройства для подклю чения к входам контролируемого блока ЦВМ, первая группа информационных входов мультиплексора соединена с группой входов рабочего воздействия устройства, первая группа разрядных выходов регистра сдвига соединена с первой группой входов блока сумматоров по модулю два и с второй группой информационных входов мультиплексора( вторая группа входов блока сумматоров по модулю два соединена с группой тестовых входов устройства, выходы блока сумматоров по модулю два соединены с информационными входами регистра сдвига, вторая группа разрядных выходов которого соединена с (п-1) входами первого элемента И

4636

(п - число входов/выходов контролируемого блока), п-й вход которого соединен с входом останова устройства, входом элемента задержки и входом сброса первого триггера, выход которого соединен с управляющим входом мультиплексора и первым входом второго элемента И, выход которого

соединен с синхровходом регистра сдвига и выходом устройства для подключения к синхровходу контролируемого блока ЦВМ, выход первого элемента И соединен с входом установки второго

триггера, первый и инверсный выходы которого соединены с первыми входами третьего и четвертого элементов И соответственно, выход элемента задержки соединен с вторыми входами третьего и четвертого элементов И, выходы которых соединены с выходами признаков исправности и неисправности устройства соответственно, вход пуска устройства соединен с входами сброса регистра сдвига, первого и второго триггеров и выходом начала работы устройства, тактовый вход которого соединен с вторым входом второго элемента И и тактовым входом первого

триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля логических блоков | 1991 |

|

SU1833879A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1411750A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

Изобретение может быть использовано в вычислительной технике и может найти примененение при разработке устройств со встроенным контролем. Цель изобретения состоит в снижении затрат оборудования и повышении быстродействия. Процесс контроля начинается с приходом сигнала на вход 7 пуска. Блок сумматоров 1 по модулю два, регистр 2 сдвига, мультиплексор 4, контролируемый блок 5 со всеми связями представляют собой автономный генератор, работающий под действием тактовых импульсов. Через заданное количество тактов приходит сигнал на вход 8 останова. Он устанавливает в нулевое состояние триггер 18, прерывая тем самым поступление тактовых импульсов в блоки устройства. К этому момнету в регистре 2 сдвига формируется конечная сигнатура. При правильной сигнатуре элемент И 9 открывается, сигнал останова устанавливает триггер 10 в единичное состояние и через элемент 18 задержки и элемент И 14 поступает на выход признака исправности устройства. При неисправной сигнатуре сигнал останова не проходит через элемент И 9, триггер 10 остается в нулевом состоянии, а сигнал с элемента 13 задержки проходит через элемент И 14 на выход признака неисправности устройства. Правильную сигнатуру определяют заранее путем подключения соответствующих прямых или инверсных выходов регистра 5 сдвига к потенциальным входам элемента И 14. 2 ил.

| Автоматика и телемеханика, 1982, Р 3, с | |||

| Джино-прядильная машина | 1922 |

|

SU173A1 |

| Антенный коммутатор | 1985 |

|

SU1478195A1 |

Авторы

Даты

1990-01-07—Публикация

1987-06-15—Подача