5 С

6

:

//7

э 3130

ИзоГфетение относится к автоматике , информационно-измерительной и вычислительной технике и может быть использовано при преобразовании кода с основанием 2 в дпоич- ный код, а также при вычислении ряда элементарных функциу.

Цель изобретения - расширение класса решаемых задач за счет обеспечения преобразования кодов с основанием 2 в двоичный код.

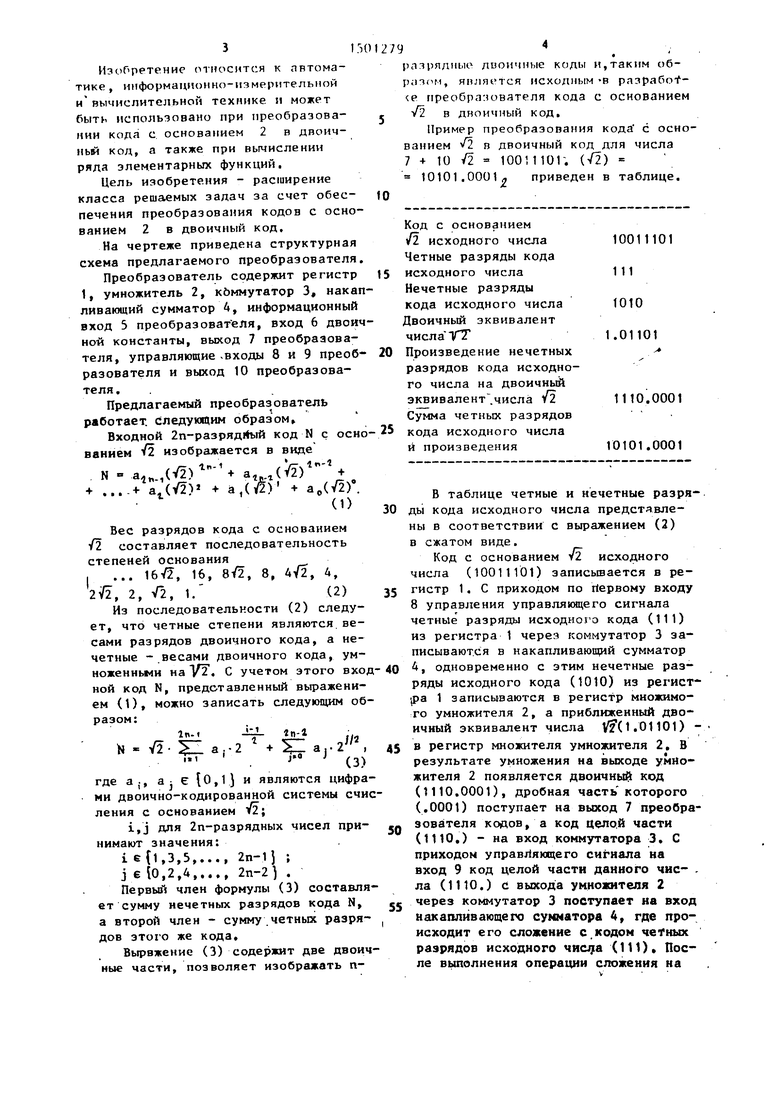

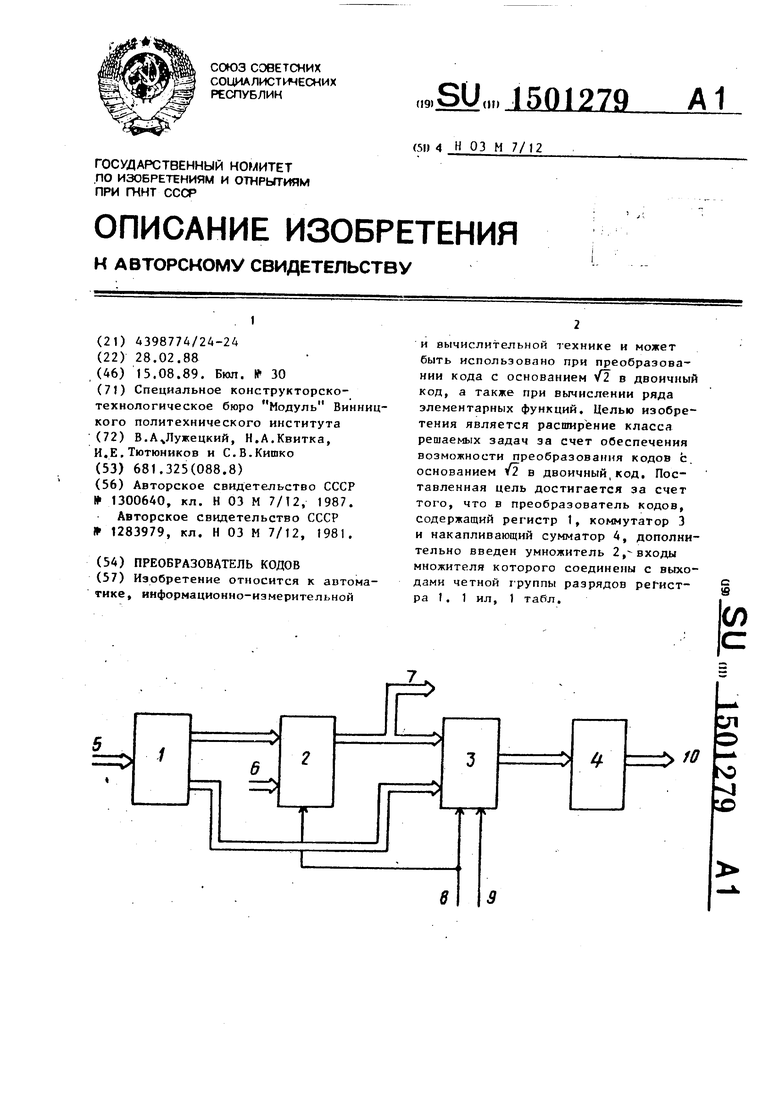

На чертеже приведена структурная схема предлагаемого преобразователя. Преобразователь содержит регистр 1, умножитель 2, кЬммутатор 3, накапливающий сумматор 4, информационный вход 5 преобразоват еля, вход 6 двоичной константы, выход 7 преобразователя, управляющие -входы 8 и 9 преобразователя и выход 10 преобразователя.

Предлагаемый преобразователь работает, следующим образом.

Входной 2п-разряд11ый код N с основанием (т. изображается в виде

.

рпзрядмые диоичмые коды и,таким образом, япляется исходным -в paapatiof- е преобраповятеля кода с основанием -/28 дноичный код.

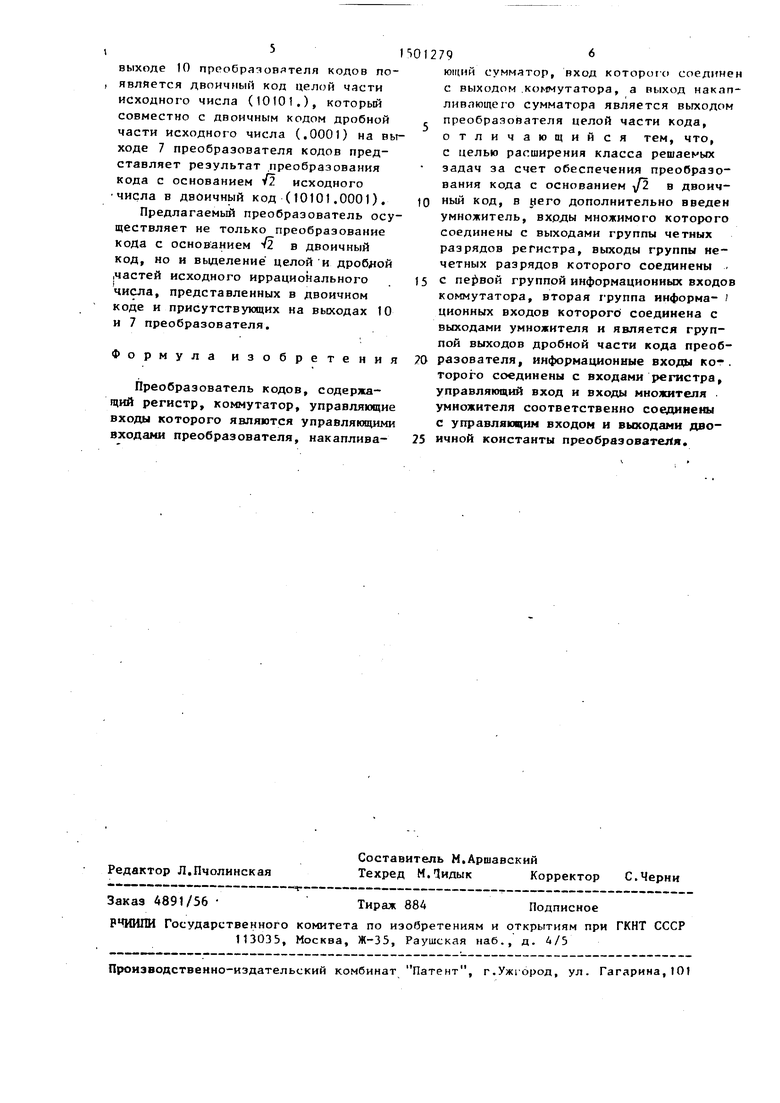

Пример преобразования кода с основанием /2 в двоичный код для числа 7 + 10 /2 10011101. (/2)

10101.0001

приведен в таблице.

Код с основанием

/2 исходного числа 10011101 Четные разряды кода исходного числа111

Нечетные разряды кода исходного числа 1010 Двоичный эквивалент числа ТТ1.01101

Произведение нечетных разрядов кода исходного числа на двоичный эквивалент .числа /2 1110.0001 Сумма четных разрядов кода исходного числа и произведения10101,0001

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1989 |

|

SU1762410A1 |

| Преобразователь кодов | 1988 |

|

SU1529458A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Устройство для аналого-цифрового преобразователя | 1988 |

|

SU1594687A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

Изобретение относится к автоматике информационно-измерительной и вычислительной технике и может быть использовано при преобразовании кода с основанием √2 в двоичный код, а также при вычислении ряда элементарных функций. Целью изобретения является расширение класса решаемых задач за счет обеспечения возможности преобразования кодов с основанием √2 в двоичный код. Поставленная цель достигается за счет того, что в преобразователь кодов, содержащий регистр 1, коммутатор 3 и накапливающий сумматор 4, дополнительно введен умножитель 2, входы множителя которого соединены с выходами четной группы разрядов регистра 1. 1 ил., 1 табл.

ln-7

a,..,(V2),..,(V2)-%, + ajV2) а,() a(V2).

(О

Вес разрядов кода с основанием /2 составляет последовательность степеней основания , ... , 16, , 8, 4/2, 4,

, 2, V2, 1. (2)

Из последовательности (2) следует, что четные степени являются весами разрядов двоичного кода, а нечетные - весами двоичного кода, ум- ноженньми на V2 , С учетом этого вход ной код N, представленный вьфажени- ем (О, можно записать следующим образом:

In., iiL «n-i N « -/2- а,.-2 + : а,.2,

г« J (3)

где aj, а: е t0,lj и являются цифрами двоично-кодированной системы счисления с основанием i2i

i,j для 2п-разрядных чисел принимают значения:

i e{l,3,5,..., 2n-lJ ;

j 6 to,2,4,..., 2n-2 .

Первый член формулы (3) составляет сумму нечетных разрядов кода N, а второй член - сумму четных разря- дов зтого же кода.

Выражение (3) содержит две двоичные части, позволяет изображать п

35

40

50

В таблице четные и нечетные разря- 30 ды кода исходного числа представлены в соответствии с выражением (2) в сжатом виде.

Код с основанием у2 исходного числа (10011101) записьшается в регистр 1. С приходом по rtepBOMy входу 8 управления управляющего сигнала четные разряды исходного кода (111) из регистра 1 через коммутатор 3 записываются в накапливающий сумматор 4, одновременно с этим нечетные разряды исходного кода (1010) из регист- (ра 1 записываются в регистр миожимо- го умножителя 2, а приближенный двоичный эквивалент числа (1,01101) - 45 в регистр множителя умножителя 2, В результате умножения на выходе умножителя 2 появляется двоичный код (1110.0001), дробная часть которого (,0001) поступает на выход 7 преобразователя кодов, а код цело.й части (1110,) - на вход коммутатора 3, С приходом управляющего сигнала на вход 9 код целой части данного чис- , ла (1110.) с выхода умножителя 2 ее через коммутатор 3 поступает на вход накаплйваюцехч) сумматора 4, где происходит его сложение с.кодом четных разрядов исходного (111), После выполнения операции сложения на

5

выходе 10 преобрагчонятеля кодов появляется двоичный код целой части исходного числа (10101,), который совместно с двоичным кодом дробной части исходного числа (.0001) на выходе 7 преобразователя кодов представляет результат .преобразования кода с основанием /2 исходного числа в двоичный код (10101.0001).

Предлагаемый преобразователь осуществляет не только преобразование кода с основанием V2 в двоичный код, но и выделение целой и дроблой .частей исходного иррационального числа, представленных в двоичном коде и присутствующих на выходах 10 и 7 преобразователя.

Формула изобретения

Преобразователь кодов, содержащий регистр, коммутатор, управляющие входы которого являются управляющими входами преобразователя, накаплива-

79

Ю1ЦНЙ сумматор, вход которог-о соедине с выходом .коммутатора, а выход накапливающего сумматора является выходом преобразователя целой части кода, отличающийся тем, что, с целью расширения класса решаемых задач за счет обеспечения преобразования кода с основанием Jl в двоичный код, в него дополнительно введен умножитель, входы множимого которого соединены с выходами группы четных разрядов регистра, выходы группы нечетных разрядов которого соединены . с первой группой информационных входов коммутатора, вторая группа информа- ционных входов которого соединена с выходами умножителя и является группой выходов дробной части кода преобразователя, информационные входы ко- . торого соединены с входами регистра, управляющий вход и входы множителя умножителя соответственно соединены с управляющим входом и выходами двоичной константы преобразователя.

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-28—Подача