сд

00 Фь

1

t

Jib

Изобретение относится к электротехнике и может быть использовано в Промышленных и тяговых электроприводах.

Цель изобретения - повышение точности регулирования.

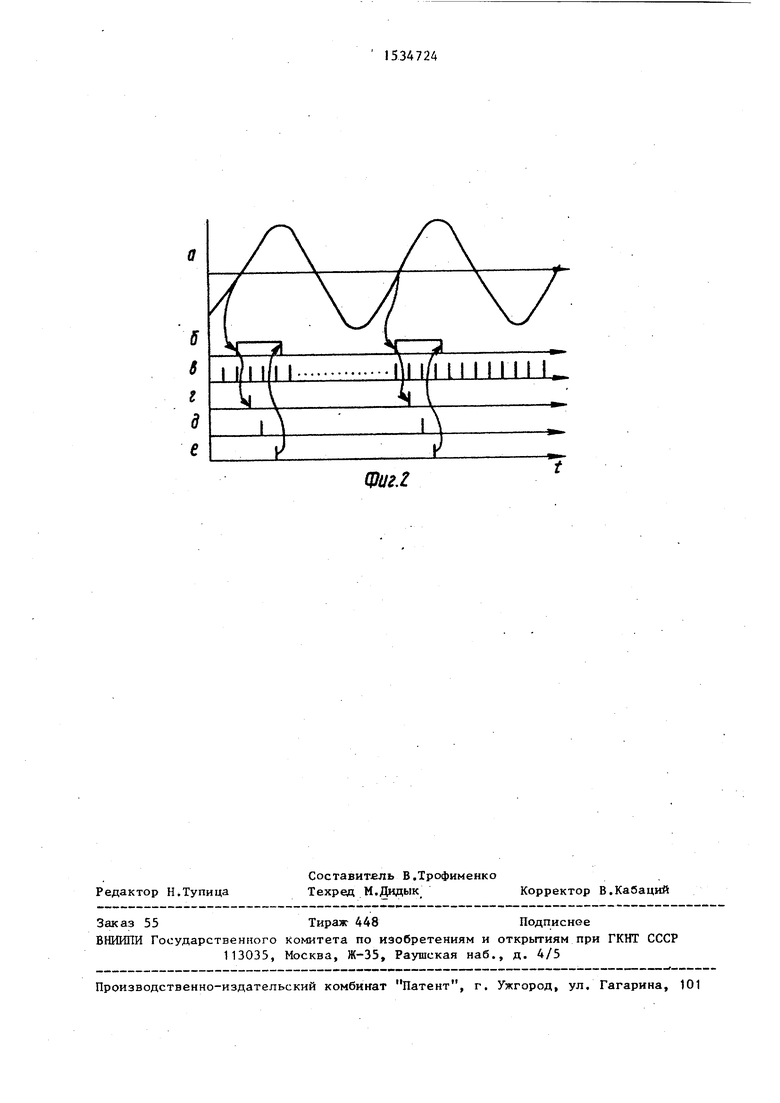

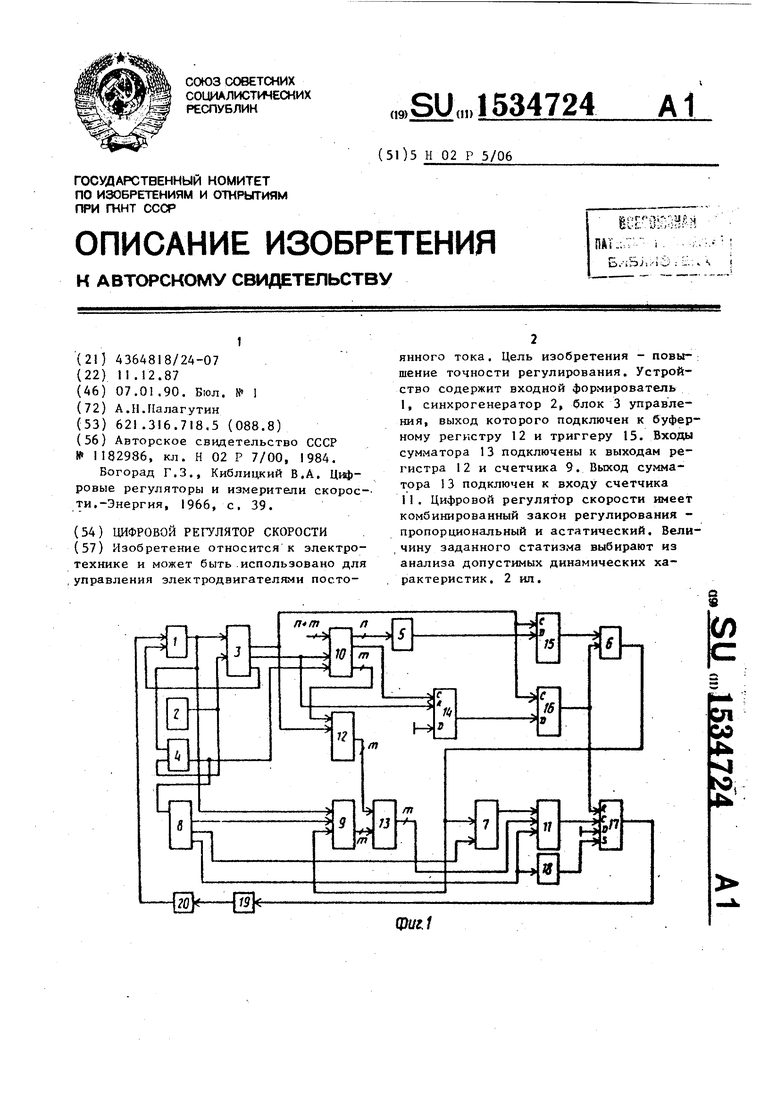

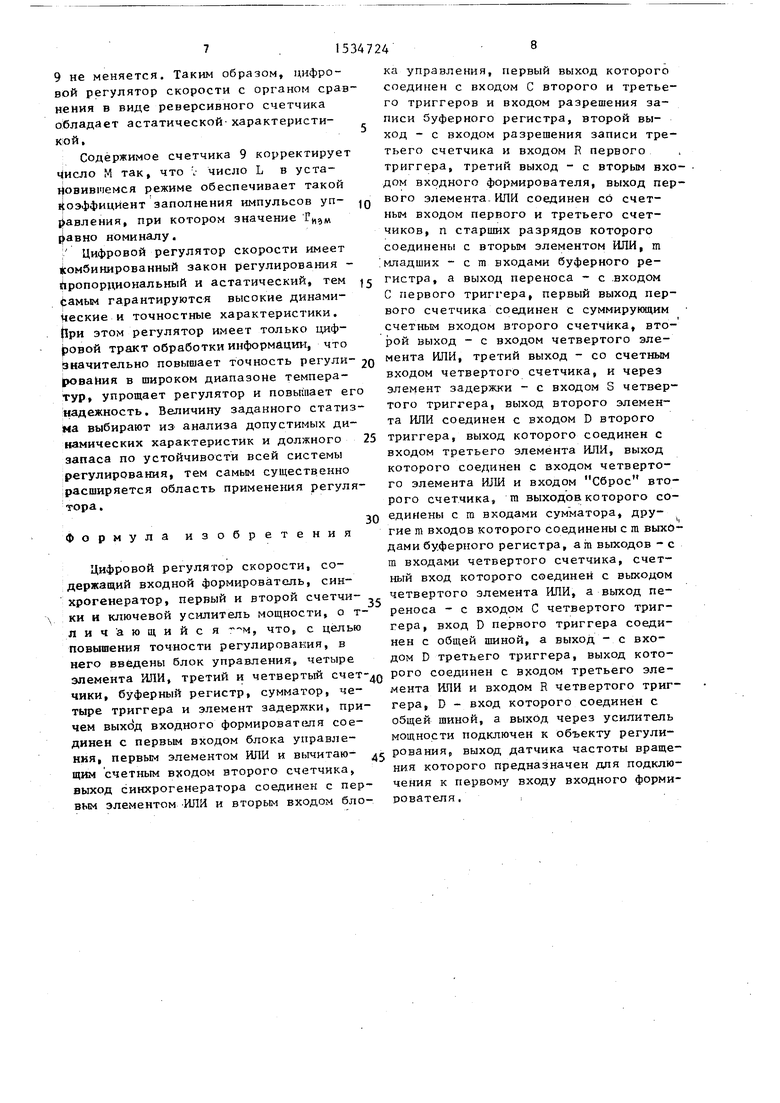

На фиг. 1 приведена схема цифрового регулятора скорости; на фиг. 2 - временная диаграмма работы регулятора.

Цифровой регулятор скорости содержит входной формирователь синхро- генератор 2 блок 3 управления, первый 4, второй 5, третий 6 и четвертый 7 элементы ИЛИ, первый 8S второй 9, третий 10 и четвертый 11 счетчики, буферный регистр 12, сумматор 13, первый 14, второй 15, третий 16 и четвертый 17 триггеры и элемент 18 задержки. При этом выход входного формирователя 1 соединен с первым входом блока 3 управления, первым элементом ИЛИ 4 и вычитающим счетным входом второго счетчика 9. Выход iсинхрогенератора 2 соединен с первым элементом ИЛИ 4 и вторым входом блока 3 управления, первый выход которого соединен с входом С второго 1 5 и третьего 16 триггеров и входом разрешения записи буферного регистра 12, второй выход - с входом разрешения записи третьего счетчика 10 и входом R первого триггера 14, третий выход - с вторым входом входного формирователя 1. Выход первого элемента ИЛИ 4 соединен :о счетчьми входами первого счетчика 8 и третьего счетчика 10, п старших разрядов которого соединены с вторым элементом ИЛИ 5, m младших -с m входами буферього регистра 12, а выход переноса - с входом С первого триггера 14. Первый выход первого счетчика 8 соединен с суммирующим счетным входом второго счетчика 9, второй выход - с входом четвертого элемента ИЛИ 7, третий выход со счетным входом четвертого счетчика 11 и через элемент 18 задержки с входом S четвертого триггера 17. Выход второго элемента ИЛИ 5 соединен с входом второго триггера 15, выход которого соединен с входом третьего элемента ЩИ 6, выход которого соединен с входом четвертого элемента ИЛИ 7 и вхо дом Сброс второго счетчика 9, m выхо дов которого соединены с m входами сумма тора 13, другие m входов которого соединены cm выходами буферного регистра 12,

-

,

10

15

20

25

30

35

40

45

50

55

a m выходов с m входами четвертого счетчика 11, счетный вход которого соединен с выходом четвертого элемента ИЛИ, а выход переноса - с входом С четвертого триггера 17. Вход D первого триггера 14 соединен с общей шиной питания, а выход - с входом D третьего триггера 16, выход которого соединен с входом третьего элемента ИЛИ 6 и входом R четвертого триггера 17, D-вход которого соединен с общей шиной, а выход через усилитель 19 мощности соединен с объектом 20 регулирования.

Регулятор работает следующим образом.

На входной формирователь 1 поступает сигнал с датчика оборотов объекта 20 регулирования, в частности это может быть переменное напряжение с выхода генератора переменного тока (фиг. 2а), насаженного на вал двигателя постоянного тока, скорость вращения которого регулирует предлагаемый регулятор. Это возможно потому, что частота переменного напряжения генератора однозначно связана со скоростью вращения двигателя. Входной формирователь 1 формирует прямоугольные импульсы (фиг. 26)с периодом входного сигнала и длительностью, определяемой импульсом с третьего выхода блока 3 управления (фиг. 2е). По ним блок 3 управления вырабатывает три управляющих импульса. Импульсы с выхода входного формирователя 1 блокируют работу первого 8 и третьего 10 счетчиков. В чх отсутствие содержимое третьего счетчика 10 декремен- гируется с частотой синхрогенератора

2 (фиг. 2в), а первый счетчик 8 рабоi

тает в режиме делителя частоты. Цикл

измерения длительности периода входного сигнала начинается с записи в третий счетчик 10 по импульсу (Фиг. 2д) с второго выхода блока 3 управления числа К, код которого задается на n+m параллельных входах счетчика 10

к т„/ге -i- ьи/тс,

где Г - номинальное значение периода регулируемой частоты; U Г - допустимое отклонение регулируемого периода от номина-( ла или статизм регулирования;Гс - период синхрогенератора.

Так как содержимое счетчика 10 декрементируется между импульсами, следующими с выхода входного формирователя 1, период следования равен пе- g риоду входного сигнала, то на момент перезаписи во втором счетчике 9 находится число з где Киг,м

а лъ текущее измеренное значение регулируемого периода. Ю

В пределах заданного статизма регулирования число М может принимать знаЧеНИЯ 06M 2iP/Tc .

Таким образом число М определяет отклонение регулируемого периода от номинала.

15

В том случае, если ТИ}М велико и вышло из заданного статизма, т.е. на выходе переноса счетчика 10 появляется импульс, устанавливающий первый триггер 14 в единицу. Сб раЪы- вается этот триггер по импульсу с второго выхода блока 3 управления (фиг. 2д).

Если значение мало, т.е. MS 52АТ/ТС, то на выходе второго элемента ИЛИ 5, на момент появления импульс (фиг. 2г) на первом выходе блока 3 управления - единица, которая переписывается во второй триггер 15, как и содержимое первого триггера 14 в третий триггер 16 по импульсу (фиг. 2г) с первого выхода блока 3 управления.

Таким образом, единица на выходе третьего элемента ИЛИ 6 свидетельству ет о выходе Ти,м из заданного статизма.

Число М по импульсу (фиг. 2г) записывается в буферный регистр 12, и в том случае, если Тизм находится в пределах статизма, число М складывается с содержимым второго счетчика 9 на сумматоре 13. Результаты осложне-- ния - число L записывается в четвер - тый счетчик 11 по импульсу с третьего выхода первого счетчика 8, работающего в режиме делителя частоты. Частота F.y следования этого импульса определяет частоту переключений усилителя 19 мощности и выбирается разработчи- ком на этапе проектирования. Причем , где Р - целое число, a FC 1 /Гс .

Четвертый счетчик I1 декрементиру- . ется импульсами с второго выхода первого счетчика 8 с частотой F, причем 2 AI

F К

g

5

0

5

0

Счетчик 11 декрементируется лишь в том случае, если находится в пределах заданного статизма регулирования и на выходе третьего элемента ИЛИ 6 - нол ь.

В этом случае импульс на выходе переноса четвертого счетчика 11 появится через время С L/F.

В начале каждого периода частоты Fa четвертый триггер 17 через элемент 18 задержки устанавливается по входу S в единицу и через время сбрасывается в ноль по входу С импульсом, приходящим с выхода переноса счетчика 11 . Таким образом, на выходе четвертого триггера 17 формируется последовательность широтно-модулированных импульсов управления с длительностью, определяемой величиной отклонения регулируемого периода от номинала, и частотой, задаваемой на этапе проектирования. Эти импульсы через усилитель 19 мощности подаются на объект 20 регулирования .

Если значение Ти%м велико и , четвертый триггер 17 сбрасывается в .ноль по входу R.

Если значение

Тц5М мало и М

2&Т

5

0

g

0

5

то триггер 17 устанавливается в единицу по входу S и так как счетчик 1I заблокирован до конца регулируемого периода по тактовому входу, он не сбрасывается по входу С в ноль, тем самым обеспечивается изменение коэффициента заполнения от нуля до единицы. Описанное выше относится к пропорциональному каналу регулирования скорости.

На суммирующий счетный вход второго счетчика 9 поступают импульсы с первого .выхода первого счетчика 8, частота следования которых равна номинальному значению регулируемой частоты: FH 1/Гн, на вычитающий счетный вход второго счетчика 9 поступают импульсы с частотой FM}M 1/Ги%м Если Т„,м находится в пределах заданного статизма, то счетчик 9 не блокируется по входу Сброс и при этом содержимое этого счетчика возрастает при и уменьшается при nP44eM M° жет быть как отрицательным числом, т.е. старший разряд равен единице, так и положительным - старший разряд равен нулю, В случае выполнения равенства содержимое счетчика

9 не меняется. Таким образом, цифровой регулятор скорости с органом сравнения в виде реверсивного счетчика обладает астатической характеристикой.

Содержимое счетчика 9 корректирует Цисло М так, что ь число L в уста- овившемся режиме обеспечивает такой Коэффициент заполнения импульсов уп- J Давления, при котором значение РМ9М равно номиналу.

Цифровой регулятор скорости имеет Комбинированный закон регулирования - йропордиональный и астатический, тем Самым гарантируются высокие динамические и точностные характеристики. Йри этом регулятор имеет только цифровой тракт обработки информации, что Значительно повышает точность регули- 2 рования в широком диапазоне температур упрощает регулятор и повышает его надежность. Величину заданного статиз- ма выбирают из анализа допустимых динамических характеристик и должного 2 запаса по устойчивости всей системы регулирования, тем самым существенно расширяется область применения регулятора.

3 Формула изобретения

Цифровой регулятор скорости, содержащий входной формирователь, син- хрогенератор, первый и второй счетчи- , ки и ключевой усилитель мощности, о т- личающийся - Ч, что, с целью повышения точности регулирования, в него введены блок управления, четыре элемента ИЛИ, третий и четвертый счет-д чики, буферный регистр, сумматор, четыре триггера и элемент задержки, причем выход входного формирователя соединен с первым входом блока управления, первым элементом ИЛИ и вычитаю- щим счетным входом второго счетчика, выход синхрогенератора соединен с первым элементом ИЛИ и вторым входом блока управления, первый выход которого соединен с входом С второго и третьего триггеров и входом разрешения записи буферного регистра, второй выход - с входом разрешения записи третьего счетчика и входом R первого триггера, третий выход - с вторым входом входного формирователя, выход первого элемента ИЛИ соединен со счетным входом первого и третьего счетчиков, п старших разрядов которого соединены с вторым элементом ИЛИ, m младших - с m входами буферного регистра, а выход переноса - с входом С первого триггера, первый выход первого счетчика соединен с суммирующим счетным входом второго счетчика, второй выход - с входом четвертого элемента ИЛИ, третий выход - со счетным входом четвертого счетчика, и через элемент задержки - с входом S четвертого триггера, выход второго элемента ИЛИ соединен с входом D второго триггера, выход которого соединен с входом третьего элемента ИЛИ, выход которого соединен с входом четвертого элемента ИЛИ и входом Сброс второго счетчика, m выходов которого соединены с m входами сумматора, другие m входов которого соединены с га выходами буферного регистра, am выходов - с m входами четвертого счетчика, счетный вход которого соединен с выходом четвертого элемента ИЛИ, а выход переноса - с входом С четвертого триггера, вход D первого триггера соединен с общей шиной, а выход - с входом D третьего триггера, выход которого соединен с входом третьего элемента ИЛИ и входом R четвертого трш- гера, D - вход которого соединен с общей шиной, а выход через усилитель мощности подключен к объекту регулирования, выход датчика частоты вращения которого предназначен для подключения к первому входу входного формирователя .

б 6

г д е

Hrf

I I I I I I II L

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой регулятор частоты | 1987 |

|

SU1524027A1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Адаптивная цифровая система управления электроприводом | 1985 |

|

SU1315938A1 |

| Измеритель временных интервалов | 1988 |

|

SU1672411A1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

Изобретение относится к электротехнике и может быть использовано для управления электродвигателями постоянного тока. Цель изобретения - повышение точности регулирования. Устройство содержит входной формирователь 1, синхрогенератор 2, блок 3 управления, выход которого подключен к буферному регистру 12 и триггеру 15. Входы сумматора 13 подключены к выходам регистра 12 и счетчика 9. Выход сумматора 13 подключен к входу счетчика 11. Цифровой регулятор скорости имеет комбинированный закон регулирования - пропорциональный и астатический. Величину заданного статизма выбирают из анализа допустимых динамических характеристик. 2 ил.

Щцг2

| Авторское свидетельство СССР № 1182986, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вогорад Г.З., Киблицкий В.А | |||

| Цифровые регуляторы и измерители скорое- ти.-Энергия, 1966, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

Авторы

Даты

1990-01-07—Публикация

1987-12-11—Подача