bi

4Ь

J

00

Изобретение относится к вычисли™ тельной технике и технике связи и ножет быть использовано в системах передачи аналоговых (речевых) сигналов.

Цель изобретения - повышение точности кодирования.

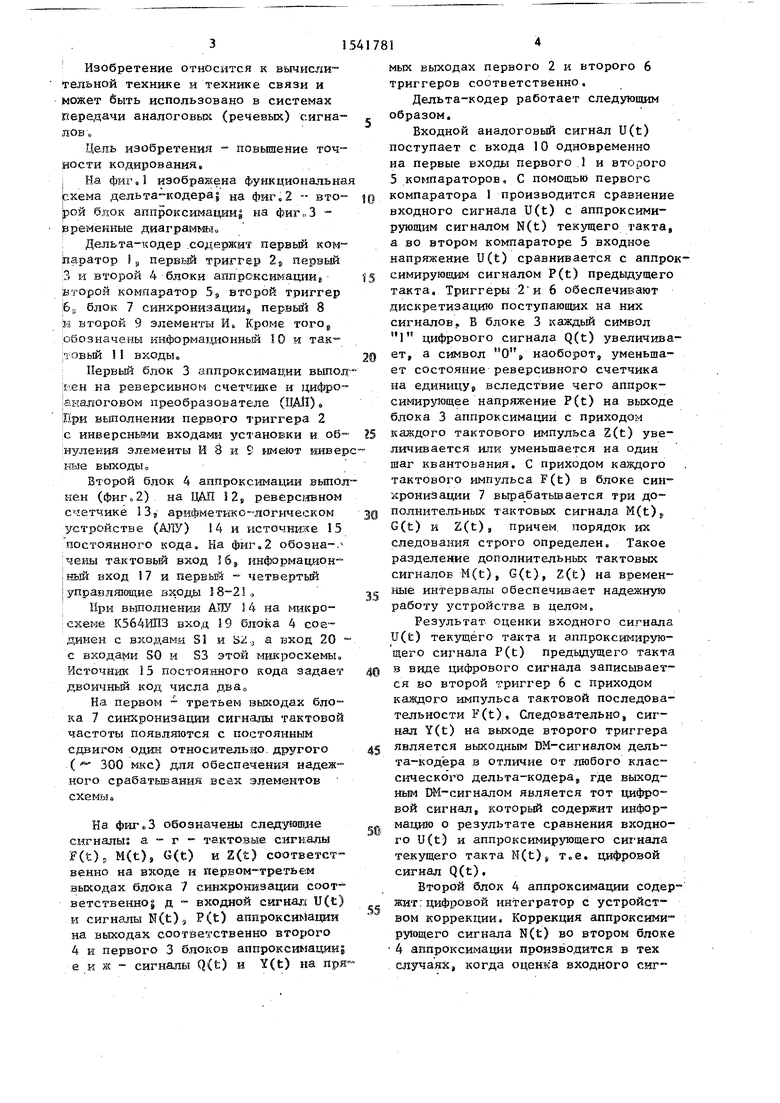

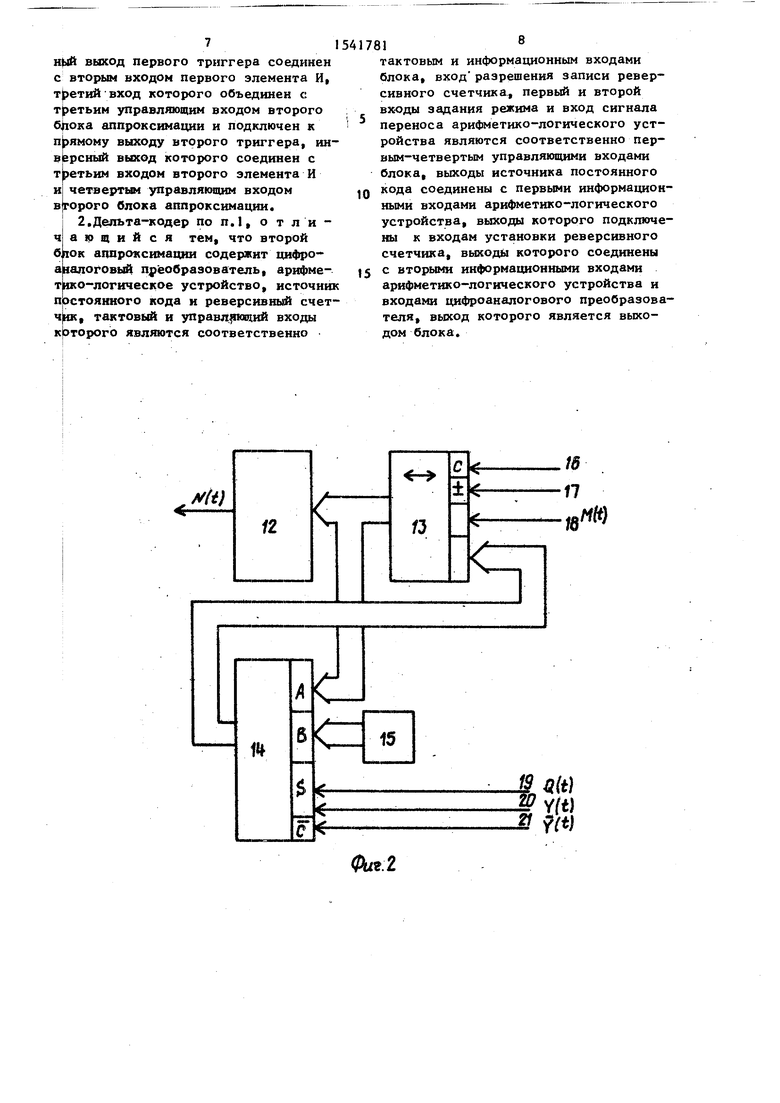

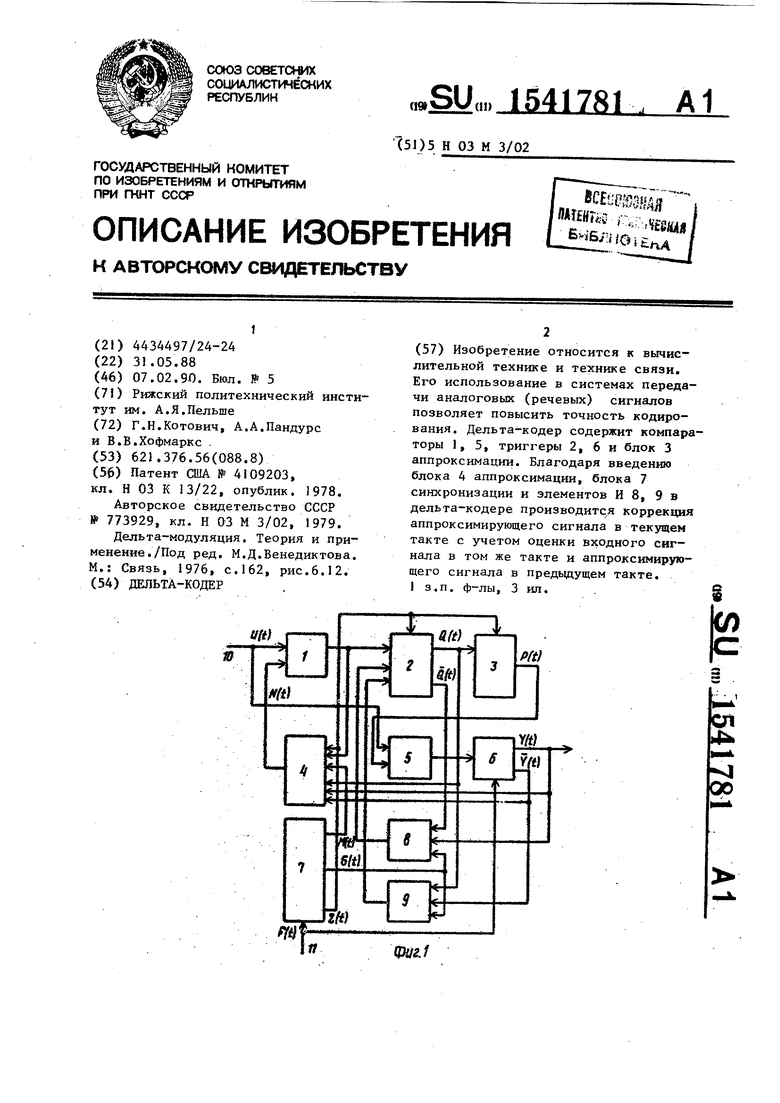

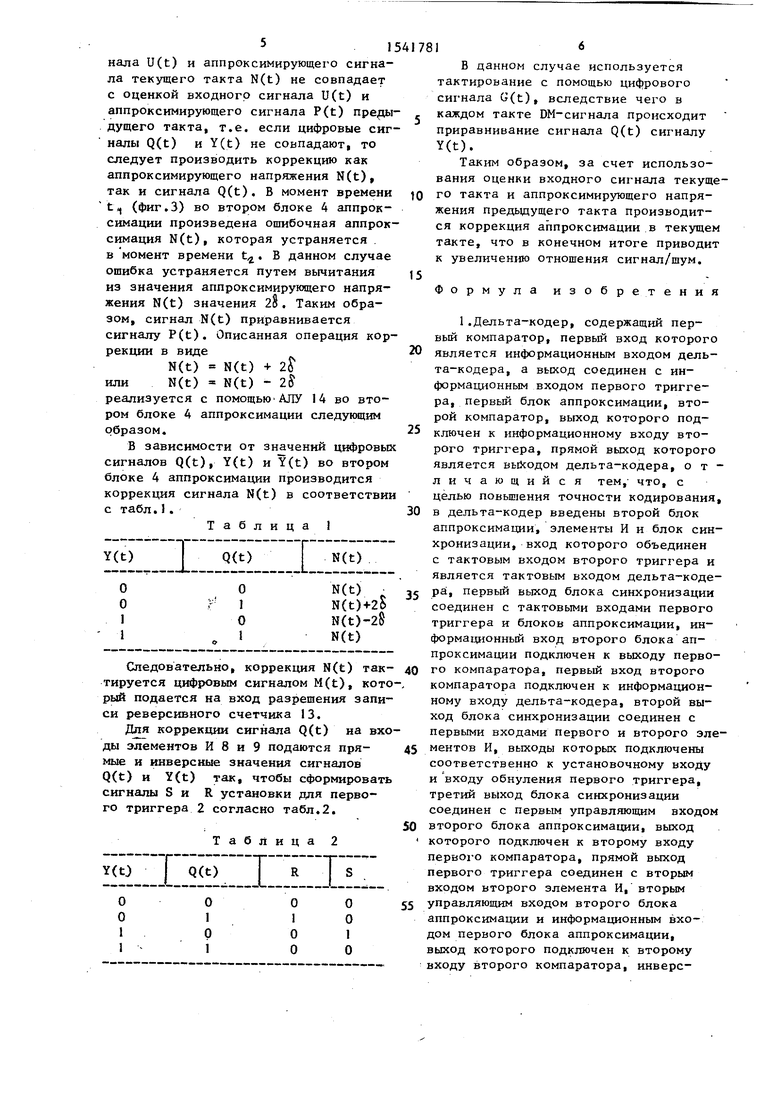

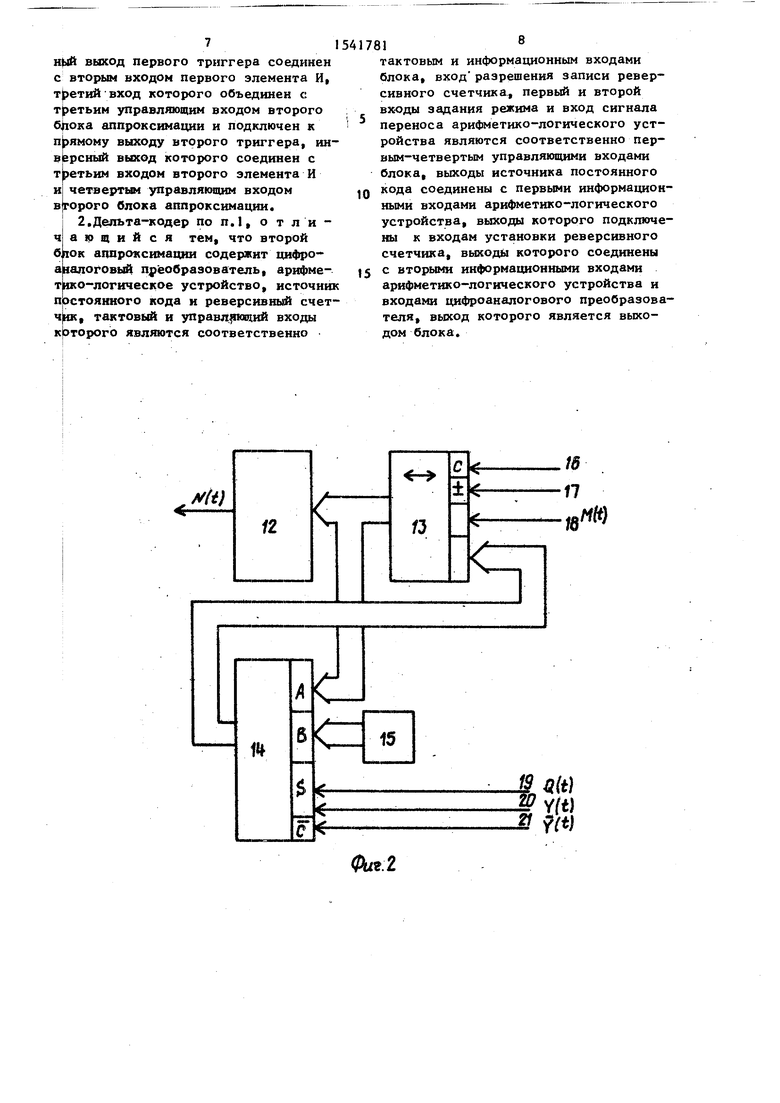

На фчг.1 изображена функциональна Схема дельта-кодераj Ha фиг.2 второй бпок аппроксимации} на фиг,3 - Временные диаграммы,,

Дельта-кодер содержи первый ком- пэратор 19 первый триггер 28 первый 3 и второй 4 блоки аппроксимациие Агорой компаратор 59 второй триггер б„ блок 7 синхроннаации9 первый 8 н второй 9 элементы И„ Кроме того обозначены информагщонный 10 ч так10ВЫЙ 11 ВХОДЫ

Первый блок 3 аппроксимации выполнен на реверсивной счетчике и цифро- аналоговом преобразователе (ПАЙ),, При выполнении первого триггера 2 с инверсными входами установки к обнуления элементы И 8 и S имеют швэер кые выходы

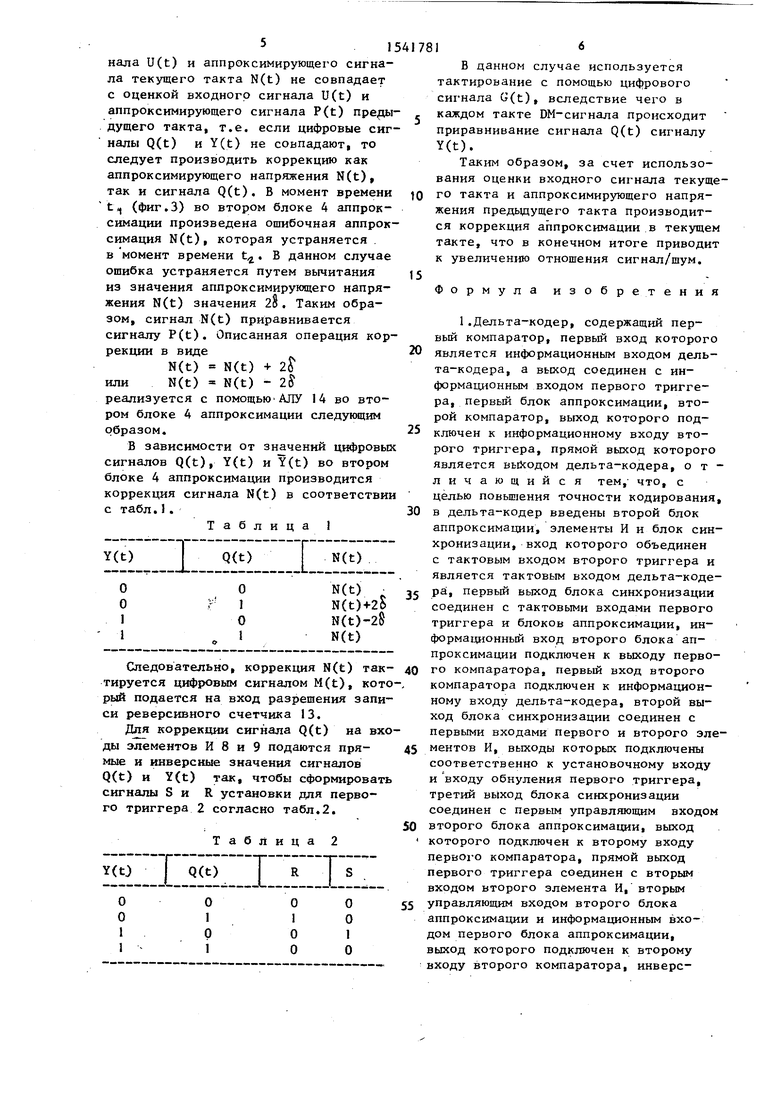

Второй блок 4 аппроксимации выполнен (фиг.2) на ЦДЛ 128 реверсивном сметчике 13Э арисЬметикс--лопгческом устройстве (АЛУ) 14 и источнике 15 постоянного кода На фиг,2 обозна- чены тактовый вход 16, информационный вход 17 и первьй - четвертый управляющие входы 18-21,,

При выполнении АЛУ 14 на микросхеме К564ИПЗ вхоц 19 блока 4 соединен с входами S1 и ЪЈ, а ьход 20 с входами SO и S3 этой микросхемы. Источник 15 постоянного кодп задает двоичный код числа два0

На первом - третьем выходах блока 7 синхронизации сигналы тактовой частоты появляются с постоянным сдвигом один относительно другого ( 300 мкс) для обеспечения надежного срабатывания всех элементов схемыо

На фигеЗ обозначены еледуюш,ие сигналы; а - г - тактовые сигналы F(tK M(t), G(t) и Z(Ј) соответственно на входе и первом-третьем выходах блока 7 синхронизации соответственно § д - входной сягнал U(t) и сигналы K(t), P(t) аппроксимации на выходах соответственно второго 4 и первого 3 блоков аппроксимацяи| е и ж - сигналы Q(t) и Y(t) на прямых выходах первого 2 и второго 6 триггеров соответственно.

Дельта-кодер работает следующим образом.

Входной аналоговый сигнал U(t) поступает с входа 10 одновременно на первые входи первого 1 и второго 5 компараторов, С помощью первого

компаратора 1 производится сравнение входного сигнала U(t) с аппроксимирующим сигналом N(t) текущего такта, а во втором компараторе 5 входное напряжение U(t) сравнивается с аппрок5 симируюЕщм сигналом P(t) предыдущего такта. Триггеры 2 и 6 обеспечивают дискретизацию поступающих на них сигналов. Б блоке 3 каждый символ 1 цифрового сигнала Q(t) увеличиваQ ет, а символ наоборот, уменьшает состояние реверсивного счетчика на единицу вследствие чего аппроксимирующее напряжение P(t) на выходе блока 3 аппроксимации с приходом

5 каждого тактового импульса Z(t) увеличивается или уменьшается на один шаг квантования, С приходом каждого тактового импульса F(t) в блоке синхронизации 7 вырабатывается три доU полнительных тактовых сигнала M(t)f G(t) и Z(t), причем порядок их следования строго определен. Такое разделение дополнительных тактовых сигналов M(t), G(t), Z(t) на времене «bie интервалы обеспечивает надежную работу устройства в целом.

Результат оценки входного сигнала U(t) текущего такта и аппроксимирующего сигнала P(t) предыдущего такта

в виде цифрового сигнала записывается во второй риггер 6 с приходом каждого импульса тактовой последовательности F(t), Следовательно, сигнал Y(t) на выходе второго триггера « является выходным DM-сигналом дель$а5

та-кодера в отличие от любого классического дельта-кодера, где выходным Ш-сигналом является тот цифровой сигнал, который содержит инфор- « мацию о результате сравнения входного U(t) и аппроксимирующего сигнала текущего такта N(t)s т„е. цифровой сигнал Q(t),

Второй блок 4 аппроксимации содержит цифровой интегратор с устройством коррекции Коррекция аппроксимирующего сигнала N(t) во втором блоке 4 аппроксимации производится в тех случаях, когда оценка входного сигS

нала U(t) и аппроксимирующего сигнала текущего такта N(t) не совпадает с оценкой входного сигнала U(t) и аппроксимирующего сигнала P(t) предыдущего такта, т.е. если цифровые сигналы Q(t) и Y(t) не совпадают, то следует производить коррекцию как аппроксимирующего напряжения N(t), так и сигнала Q(t). В момент времени t,, (фиг.З) во втором блоке 4 аппроксимации произведена ошибочная аппроксимация N(t), которая устраняется в момент времени Ц. В данном случае ошибка устраняется путем вычитания из значения аппроксимирующего напряжения N(t) значения 2§. Таким образом, сигнал N(t) приравнивается сигналу P(t). Описанная операция коррекции в виде

N(t) N(t) + 261 или N(t) N(t) - 2§ реализуется с помощью АЛУ 14 во втором блоке 4 аппроксимации следующим образом.

В зависимости от значений цифровых сигналов Q(t), Y(t) и Y(t) во втором блоке 4 аппроксимации производится коррекция сигнала N(t) в соответствии с табл.1.

Таблица 1

I

)

Е

N(t)

Следовательно, коррекция N(t) так- 40 тируется цифровым сигналом M(t), кото-, рый подается на вход разрешения записи реверсивного счетчика 13.

Для коррекции сигнала Q(t) на входы элементов И 8 и 9 подаются пря- 45 мые и инверсные значения сигналов Q(t) и Y(t) так, чтобы сформировать сигналы S и R установки для первого триггера 2 согласно табл.2.

50

30 4

5

0

5

0

5

0

В данном случае используется тактирование с помощью цифрового сигнала G(t), вследствие чего в с каждом такте DM-сигнала происходит приравнивание сигнала Q(t) сигналу Y(t).

Таким образом, за счет использования оценки входного сигнала текуще- 0 го такта и аппроксимирующего напряжения предыдущего такта производится коррекция аппроксимации в текущем такте, что в конечном итоге приводит к увеличению отношения сигнал/шум.

Формула изобретения

1.Дельта-кодер, содержащий первый компаратор, первый вход которого является информационным входом дельта-кодера, а выход соединен с информационным входом первого триггера, первый блок аппроксимации, второй компаратор, выход которого под5 ключей к информационному входу второго триггера, прямой выход которого является выходом дельта-кодера, отличающийся тем, что, с целью повышения точности кодирования,

0 в дельта-кодер введены второй блок аппроксимации, элементы И и блок синхронизации, вход которого объединен с тактовым входом второго триггера и является тактовым входом дельта-кодера, первый выход блока синхронизации соединен с тактовыми входами первого триггера и блоков аппроксимации, информационный вход второго блока аппроксимации подключен к выходу первого компаратора, первый вход второго компаратора подключен к информационному входу дельта-кодера, второй выход блока синхронизации соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к установочному входу и входу обнуления первого триггера, третий выход блока синхронизации соединен с первым управляющим входом второго блока аппроксимации, выход 4 которого подключен к второму входу первого компаратора, прямой выход первого триггера соединен с вторым входом второго элемента И, вторым

5 управляющим входом второго блока аппроксимации и информационным входом первого блока аппроксимации, выход которого подключен к второму входу второго компаратора, инверс71

ный выход первого триггера соединен с вторым входом первого элемента И, третий вход которого объединен с третьим управляющим входом второго блока аппроксимации и подключен к прямому выходу второго триггера, инверсный выход которого соединен с третьим входом второго элемента И и четвертым управляющим входом второго блока аппроксимации.

2.Дельта-кодер по п.1, отличающийся тем, что второй блок аппроксимации содержит цифро- аналоговый преобразователь, арифметико-логическое устройство, источник постоянного кода и реверсивный счетчик, тактовый и управляющий входы которого являются соответственно

5417818

тактовым и информационным входами блока, вход разрешения записи реверсивного счетчика, первый и второй входы задания режима и вход сигнала

5 переноса арифметико-логического устройства являются соответственно первым-четвертым управляющими входами блока, выходы источника постоянного

10 кода соединены с первыми информационными входами арифметико-логического устройства, выходы которого подключены к входам установки реверсивного счетчика, выходы которого соединены

15 с вторыми информационными входами арифметико-логического устройства и входами цифроаналогового преобразователя, выход которого является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Устройство связи с дельта-модуляцией | 1986 |

|

SU1365364A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Дельта-кодер | 1985 |

|

SU1290529A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи аналоговых (речевых) сигналов позволяет повысить точность кодирования. Дельта-кодер содержит компараторы 1, 5, триггеры 2, 6 и блок 3 аппроксимации. Благодаря введению блока 4 аппроксимации, блока 7 синхронизации и элементов И 8, 9 в дельта-кодере производится коррекция аппроксимирующего сигнала в текущем такте с учетом оценки входного сигнала в том же такте и аппроксимирующего сигнала в предыдущем такте. 1 з.п.ф-лы, 3 ил.

#м

12

Л

6

$

-

.18 17

Я

.«

-Ј« )

Л W

Фиг.г

| Патент США № 4109203, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Устройство адаптивной дельта-модуляции | 1979 |

|

SU773929A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дельта-модуляция | |||

| Теория и применение | |||

| /Под ред | |||

| М.Д.Бенедиктова | |||

| М.: Связь, 1976, с.162, рис.6.12. | |||

Авторы

Даты

1990-02-07—Публикация

1988-05-31—Подача