Изобретение относится к вычислит тельной технике и микроэлектронике и предназначено для выполнения операции Х+С над n-разрядными числами в мультиконвейерном режиме.

Цель изобретения - расширение функциональных возможностей за счет выполнения операции сложения при одновременном сокращении аппаратурных затрат.

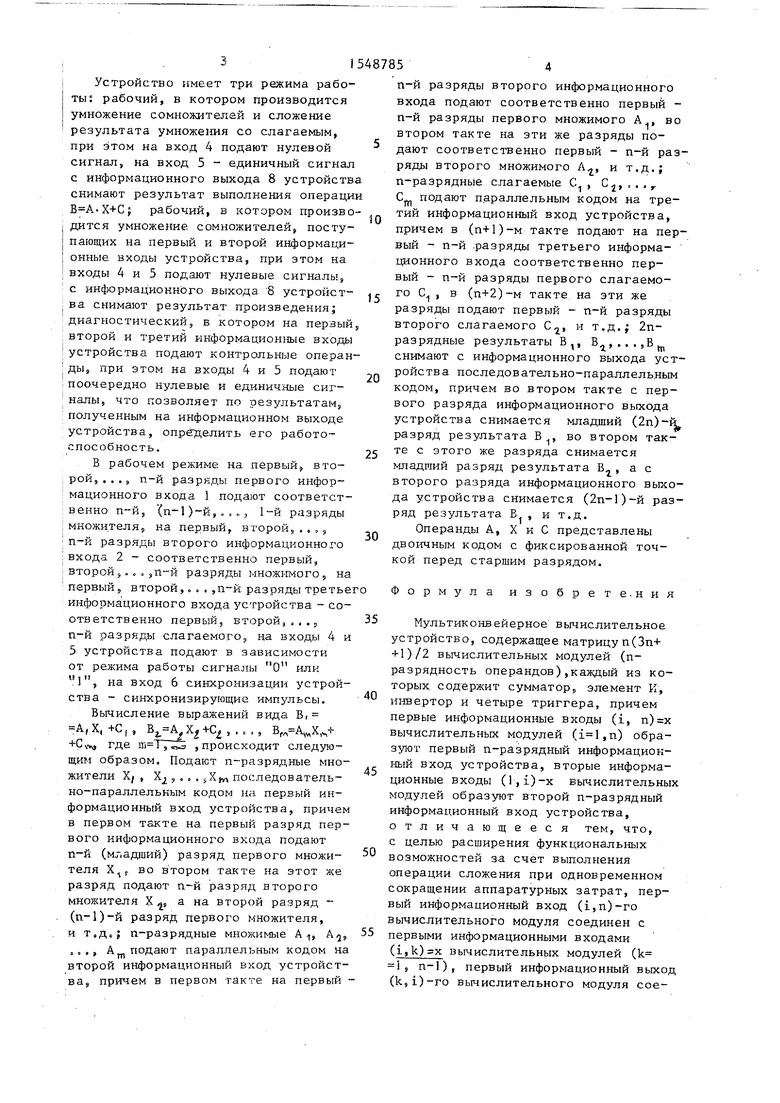

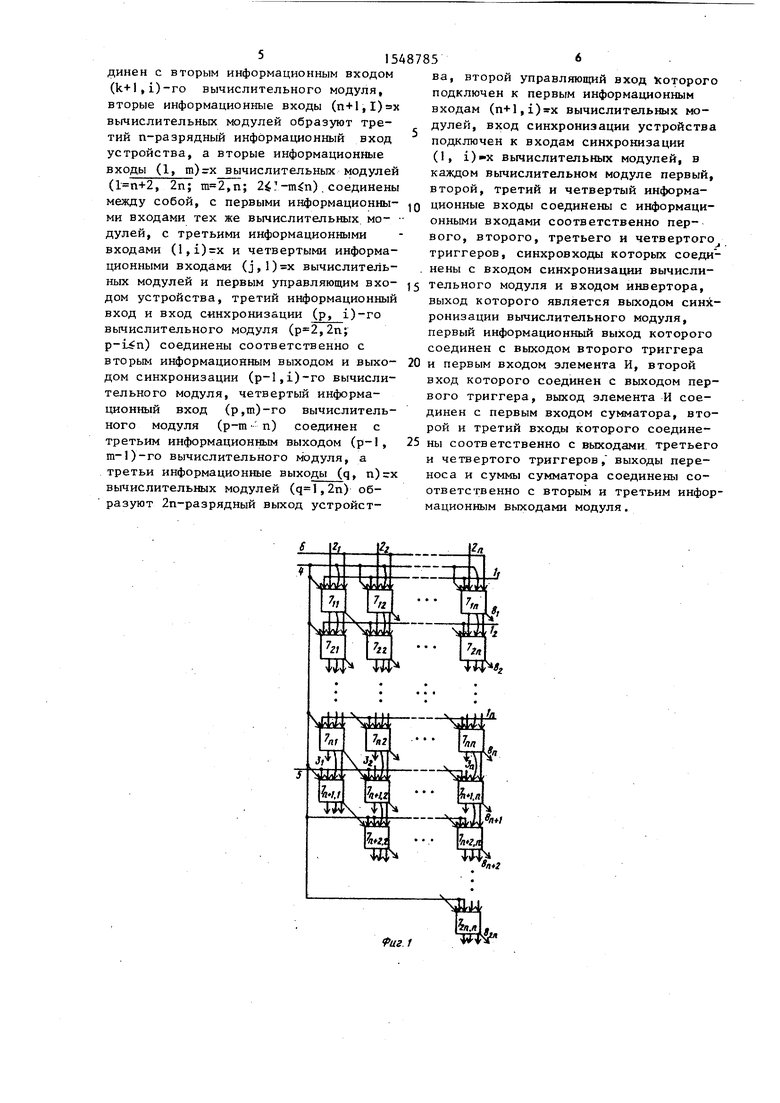

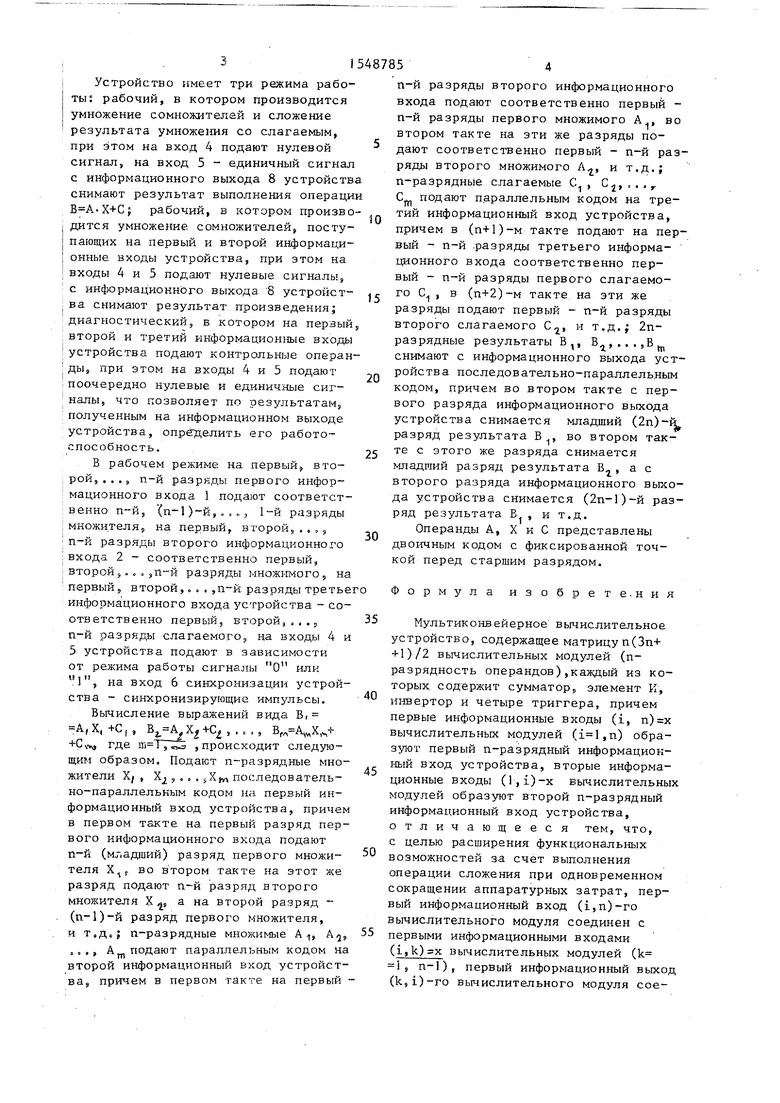

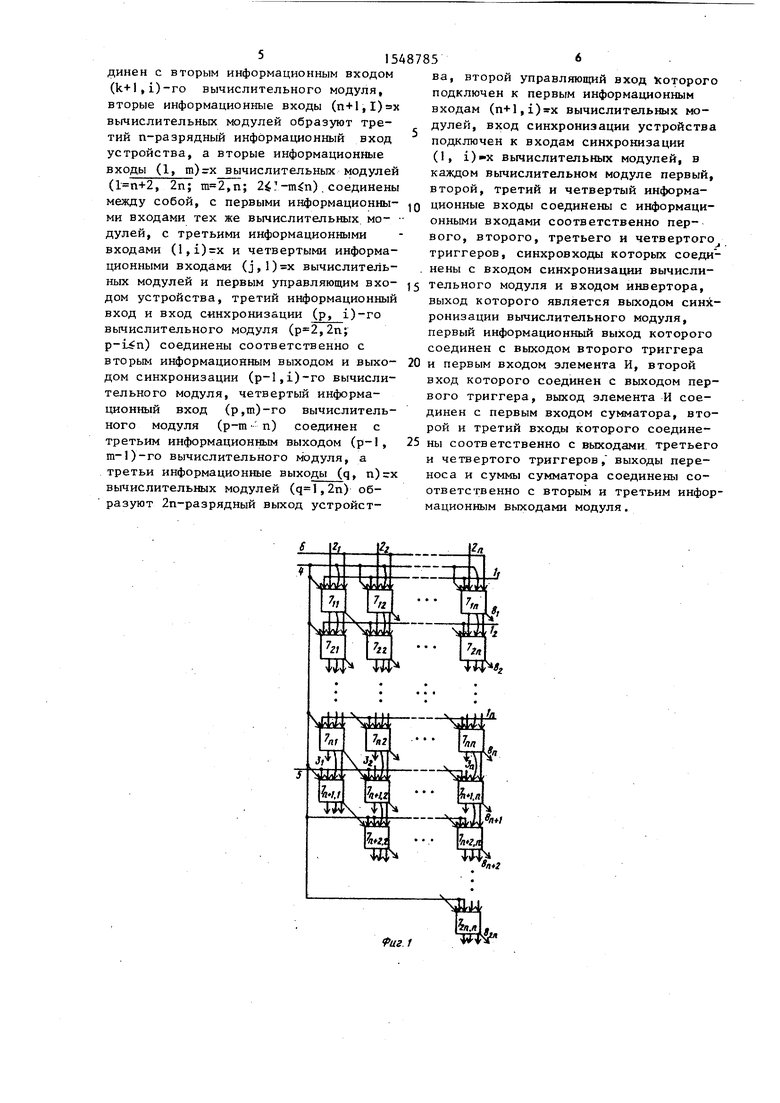

На фиг. 1 представлена функциональная схема устройства; на фиг.2- функциональная схема вычислительного

модуля.

Устройство содержит (фиг. 1) с первого по n-й разряды первого информационного входа 1 устройства, соответственно 1; -Ц , с первого по п-ый

разряды второго информационного входа 2 устройства, соответственно 2 -2п , с с первого по n-й разряды третьего информационного входа 3 устройства, соответственно 3,-Зп, первый 4 и .второй 5 управляющие входы устройства, вход 6 синхронизации устройства, вычислительные модули 7, с первого по 2-й разряды информационного выхода 8 устройства, соответственно 8(, Каждый вычислительный модуль содержит (фиг. 2) первый, второй, третий и четвертый информационные входы 9- 12, вход 13 синхронизации, четыре триггера 14, элемент И -15, инвертор 16, сумматор 17, первый и второй информационные выходы 18 и 19, выход 20 синхронизации и третий информационный выход 21.

сл

4Ь

00

1

00 СП

Устройство имеет три режима работы: рабочий, в котором производится умножение сомножителей и сложение результата умножения со слагаемым, при этом на вход 4 подают нулевой сигнал, на вход 5 - единичный сигнал с информационного выхода 8 устройства снимают результат выполнения операции рабочий, в котором производится умножение сомножителей,, посту- пагащих на первый и второй информаци- онные входы устройства, при этом на входы 4 и 5 подают нулевые сигналы, с информациоиного выхода 8 устройства снимают результат произведения; диагностический, в котором на перзый, второй и третий информационные входы устройства подают контрольные операнды, при этом на входы 4 и 5 подают поочередно нулевые и единичные сигналы, что позволяет пп оезультатам, полученным на информационном выходе устройства, определить его работоспособность.

В рабочем режиме на первый, второй, ..., разряды первого информационного входа I подают соответственно n-й, (п-1)-й,

1-й разряды

множителя, на первый, второй,.,,, n-й разряды второго информационного входа 2 - соответственно первый, зторой9.,о,п-й разряды множимого, на первый, второй,. „ . ,п-й разряды третье информационного входа устройства - соответственно первый, второй,.,,, n-й разряды слагаемого, на входы 4 и 5 устройства подают в зависимости от режима работы сигналы О или ul, на вход 6 синхронизации устройства - синхронизирующие импульсы. Вычисление выражений вида Б, А,Х(+С(9 ,.,., , +Cv где , происходит следующим образом Подают п-разрядные множители X/ , Х з . . . последовательно-параллельным кодом H«I первый информационный вход устройства, причем в первом такте на первый разряд первого информационного входа подают (младший) разряд первого множителя X,f во втором такте на этот же разряд подают n-й разряд второго

множителя X

а на второй разряд

(п-1)-й разряд первого множителя, и т, n-разрядные множимые А 1( A/J, ,, ., А подают параллельным кодом на второй информационный вход устройства, причем в первом такте на первый 0

5

0

5

0

5

0

5

0

5

n-й разряды второго информационного входа подают соответственно первый - n-й разряды первого множимого А., во втором такте на эти же разряды подают соответственно первый - n-й разряды второго множимого А, и т.д.; n-разрядные слагаемые С , С2, . , г С подают параллельным кодом на третий информационный вход устройства, причем в (п+1)-м такте подают на первый - n-й разряды третьего информационного входа соответственно первый - n-й разряды первого слагаемого С1 , в (п+2)-м такте на эти же разряды подают первый - n-й разряды второго слагаемого Сг, и т.д.; 2п- разрядные результаты В,, Вг,...,В11) снимают с информационного выхода устройства последовательно-параллельным кодом, причем во втором такте с первого разряда информационного выхода устройства снимается младший (2п)-й разряд результата В во втором такте с этого же разряда снимается младший разряд результата Вг, а с второго разряда информационного выхода устройства снимается (2п-1)-й разряд результата В , и т.д.

Операнды А, X и С представлены двоичным кодом с фиксированной точкой перед старшим разрядом.

Формула изобретения

Мультиконвейерное вычислительное устройство, содержащее матрицу п(3п+ +1)/2 вычислительных модулей (п- разрядность операндов),каждый из которых содержит сумматор, элемент К, инвертор и четыре триггера, причем первые информационные входы (i, n)x вычислительных модулей (,n) образуют первый n-разрядный информационный вход устройства, вторые информационные входы (l,i)-x вычислительных модулей образуют второй n-разрядный информационный вход устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операции сложения при одновременном сокращении аппаратурных затрат, первый информационный вход (i,n)-ro вычислительного модуля соединен с первыми информационными входами (i,k)ах вычислительных модулей (k i, n-1), первый информационный выход (k,i)-ro вычислительного модуля соединен с вторым информационным входом (k+l,i)-ro вычислительного модуля, вторые информационные входы (п+1,1)х вычислительных модулей образуют третий п-разрядный информационный вход устройства, а вторые информационные входы (1, т):х вычислительных модулей (, 2n; ,n; ) соединены между собой, с первыми информационными входами тех же вычислительных мо- - дулей, с третьими информационными входами (l,i)x и четвертыми информационными входами (j,1)х вычислительных модулей и первым управляющим входом устройства, третий информационный вход и вход синхронизации (р, i)-ro вычислительного модуля (,2п; ) соединены соответственно с вторым информационным выходом и выходом синхронизации (p-l,i)-ro вычислительного модуля, четвертый информационный вход (р,т)-го вычислительного модуля (р-т п) соединен с третьим информационным выходом (р-1, т-1)-го вычислительного модуля, а третьи информационные выходы (q, n)rx вычислительных модулей (,2n) образуют 2п-разрядный выход устройства, второй управляющий вход Которого подключен к первым информационным входам (n+l,i)x вычислительных модулей, вход синхронизации устройства подключен к входам синхронизации (1, i)-x вычислительных модулей, в каждом вычислительном модуле первый, второй, третий и четвертый информационные входы соединены с информационными входами соответственно первого, второго, третьего и 4eTBepToroj триггеров, синхровходы которых соединены с входом синхронизации вычислительного модуля и входом инвертора, выход которого является выходом синхронизации вычислительного модуля, первый информационный выход которого соединен с выходом второго триггера

0 и первым входом элемента И, второй вход которого соединен с выходом первого триггера, выход элемента И соединен с первым входом сумматора, второй и третий входы которого соедине5 ны соответственно с выходами третьего и четвертого триггеров, выходы переноса и суммы сумматора соединены соответственно с вторым и третьим информационным выходами модуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Мультиконвейерный делитель | 1988 |

|

SU1587499A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Отказоустойчивое устройство для умножения чисел | 1990 |

|

SU1777134A1 |

| Устройство для умножения | 1990 |

|

SU1789981A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для умножения чисел | 1988 |

|

SU1536374A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1988 |

|

SU1529215A1 |

Изобретение относится к области вычислительной техники и микроэлектроники и предназначено для реализации операции B=A.X + C над N-разрядными двоичными числами в мультиконвейерном режиме. Цель изобретения - расширение функциональных возможностей за счет выполнения операции сложения при одновременном сокращении аппаратурных затрат. Устройство содержит матрицу однотипных вычислительных модулей с локальными связями и, таким образом, ориентировано на СБИС-технологию. Особенностью работы устройства является параллельно-поточная организация вычислений. 2 ил.

9,иг 1

to. 2

| Матричный вычислитель | 1985 |

|

SU1265765A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Patrice Quinbon, Pierrick Cachet | |||

| Automatic design of systolic chips.- IRISA, Campus de Beaulien 35042 Rennes-Codex, France, Rapports de Recherche, № 450, octobre, 1985 | |||

| p | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

1990-03-07—Публикация

1988-06-14—Подача